EMIFNandFlash文档.docx

《EMIFNandFlash文档.docx》由会员分享,可在线阅读,更多相关《EMIFNandFlash文档.docx(13页珍藏版)》请在冰豆网上搜索。

EMIFNandFlash文档

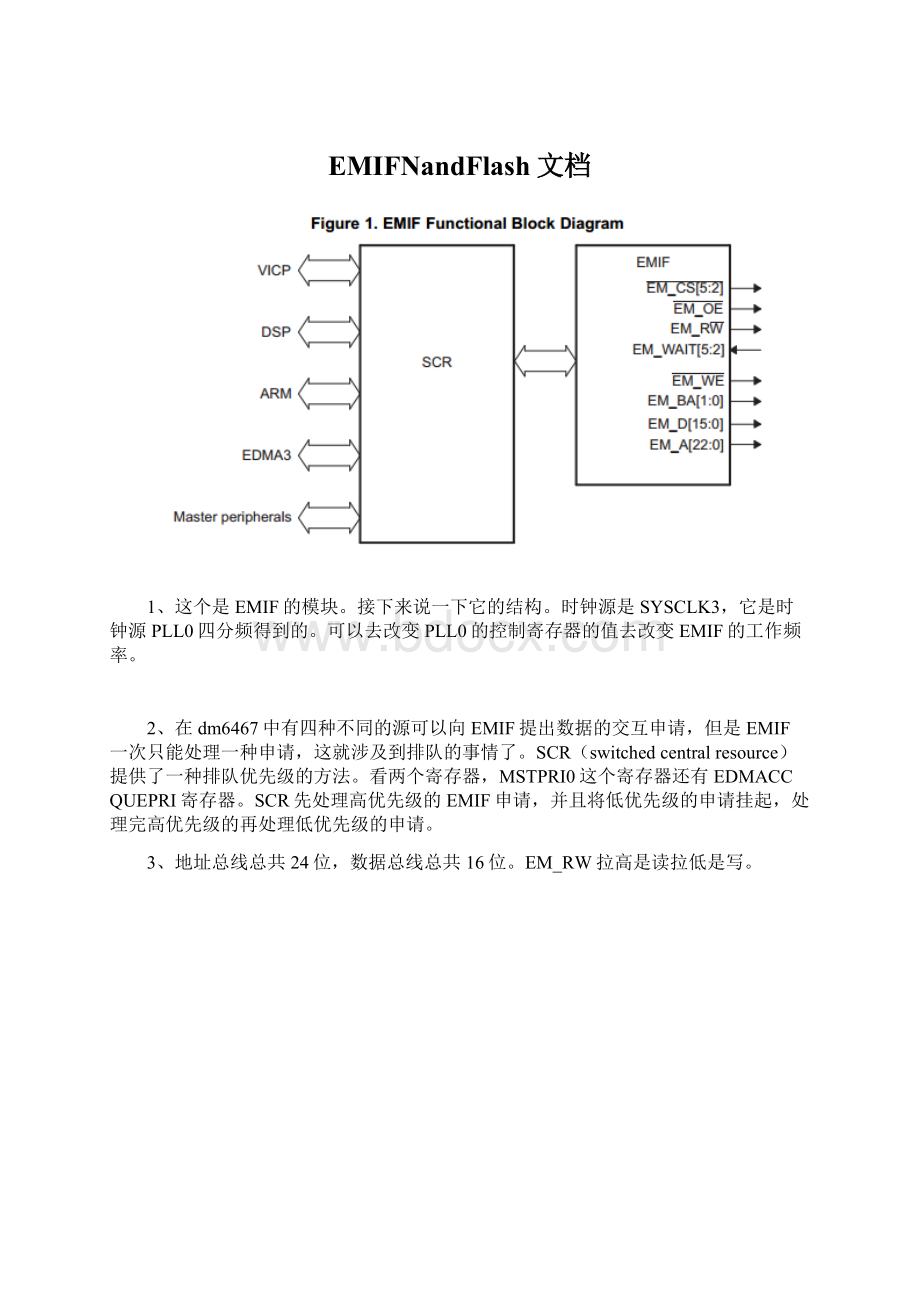

1、这个是EMIF的模块。

接下来说一下它的结构。

时钟源是SYSCLK3,它是时钟源PLL0四分频得到的。

可以去改变PLL0的控制寄存器的值去改变EMIF的工作频率。

2、在dm6467中有四种不同的源可以向EMIF提出数据的交互申请,但是EMIF一次只能处理一种申请,这就涉及到排队的事情了。

SCR(switchedcentralresource)提供了一种排队优先级的方法。

看两个寄存器,MSTPRI0这个寄存器还有EDMACCQUEPRI寄存器。

SCR先处理高优先级的EMIF申请,并且将低优先级的申请挂起,处理完高优先级的再处理低优先级的申请。

3、地址总线总共24位,数据总线总共16位。

EM_RW拉高是读拉低是写。

这里面的后三个引脚得再看看。

4、EMIF的三种工作模式,一个是normal模式,另一个是selectstrobe模式,第三个是NANDflash模式。

normal的工作模式在整个异步的访问期间,selectstrobe模式是在strobe期间。

这两个模式好理解,主要指的是EM_CS这个信号的持续时间做区分。

对于NAND_FLASH模式,EMIF的硬件能计算出ECC(errorcorrectioncode)在每512个字节数据的传输。

5、EM_BA[1:

0]这里的bit1用的对应的16位的传输,bit0对应的是8bit位的传输。

EM_BA[1]如果连到A[0],就是16bit的数据传输。

6、读写操作的正常模式

写时序:

与NANDFLASH互联模式。

驱动CLE和ALE。

如果用EM_A2和EM_A1这个去连接CLE和ALE,00h是让这两个信号都为低。

10HS是CLE高ALE低。

01H是CLE低ALE高。

如果连接到NANDFLASH的基地址是42000000,如果想让CLE高ALE低。

映射地址应该是0x42000010h

NAND的读操作

NAND访问周期由命令,地址,还有数据三个阶段。

EMIF在一个访问请求下不会自动的产生这三个阶段去完成NAND的访问。

为了完成NAND的访问周期,EMIF将要完成多个异步的访问。

软件需要恰当的异步访问去完成NANDFLASH的访问。

软件要指定哪个NANDflash设备。

因为NANDFLASH读写要分成多个异步周期的访问所以片选信号的时间也要分开。

ECC是errorcorrectioncode意思。

在NANDFLASH模式下,每512个字节的数据传输就会计算出ECC。

ECC的产生,NANDFCR寄存器里面的CS2ECC这个bit位被设置为1。

读操作的正常模式:

NANDFLASH用EDMA需要注意的事情与ALE和CLE有关。

他俩应该都为低。

要是有一个为高可能就不好用了。

NandFlash里面的结构。

时序图

往NANDFLASH写数据

读取ID,然后后面跟00h返回来的信息是5字节的ID信息,包括deviceID。

有各个信息位的信息还有整个字节的信息。