完整板基于EDA的交通灯设计.docx

《完整板基于EDA的交通灯设计.docx》由会员分享,可在线阅读,更多相关《完整板基于EDA的交通灯设计.docx(28页珍藏版)》请在冰豆网上搜索。

完整板基于EDA的交通灯设计

1.1EDA设计的发展状况:

本设计是建立在EDA基础上完成的项目。

EDA技术经历了CAD阶段,CAE阶段,EDA阶段三个发展阶段。

在今天,EDA技术已经成为电子设计的普遍工具,无论设计芯片还是设计系统,没有EDA工具的支持,都是难以完成的。

如今的EDA区别于曾经的:

构成系统的“积木块”是各种标准芯片。

EDA技术的出现改变了这种传统思路,使人们可以立足于PLD芯片来实现各种不同的功能,新的设计方法能够由设计者自己定义器件的内部逻辑和管脚,将原来由电路版设计完成的工作大部分放在芯片的设计中进行。

1.2国内外交通灯的发展状况:

本人所设计的交通灯设计早已经不仅仅禁锢于当初的红黄绿三色灯上了,在各大交通紧张的十字路口还可能设有左转灯,四盏灯按合理顺序亮灭。

同样也可以运用Verilog语言进行编译完成此设计。

而目前,国内外专家和学者普遍采用模糊控制方法来设计交通灯实时控制系统实践表明,采用这种方法设计的控制系统可进一步提高路网的通行能力,减少路口延误时间和停车次数,对高度非线性的、随机的十字路口车流量的控制更加精确,并取得了更高的经济效益。

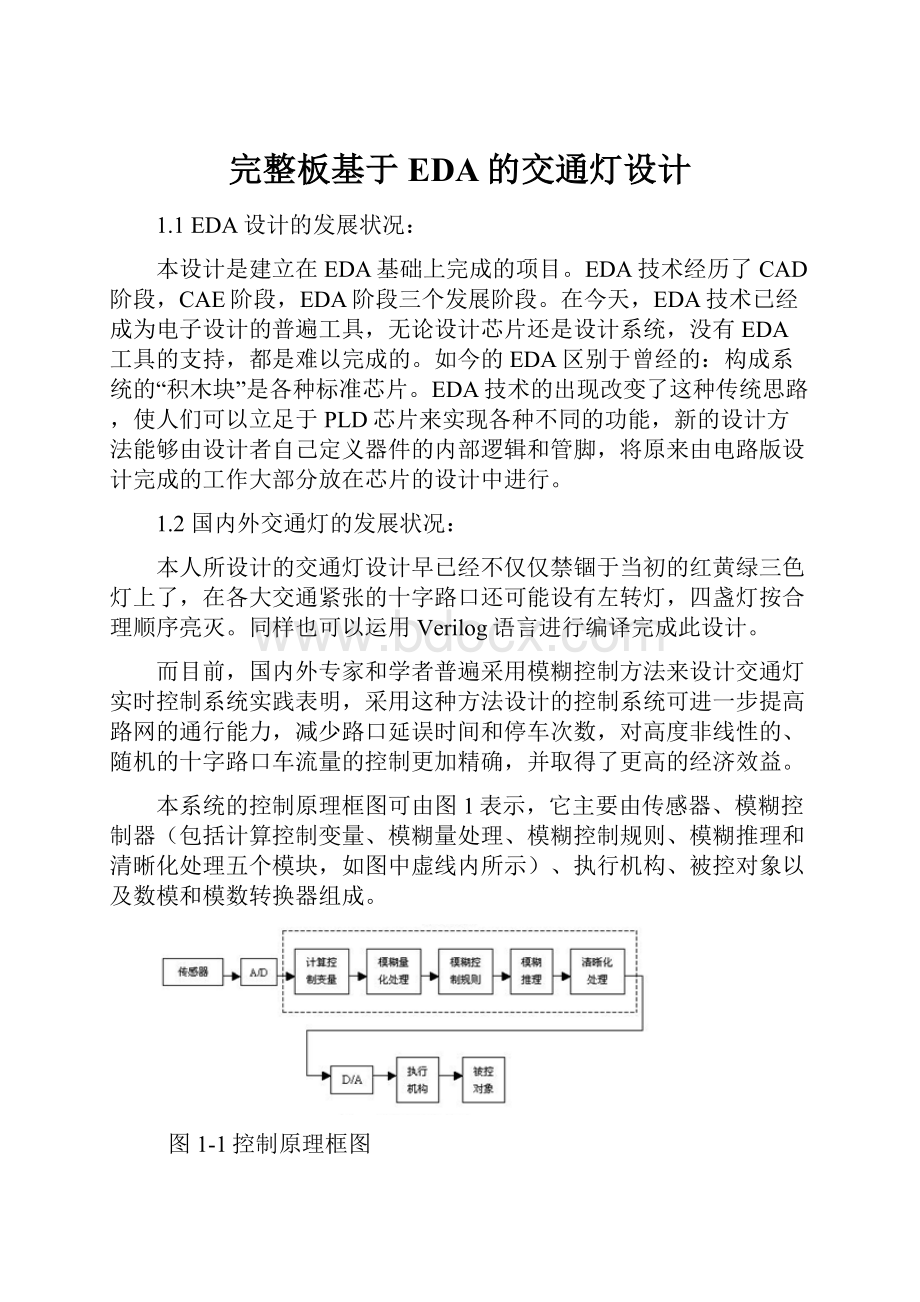

本系统的控制原理框图可由图1表示,它主要由传感器、模糊控制器(包括计算控制变量、模糊量处理、模糊控制规则、模糊推理和清晰化处理五个模块,如图中虚线内所示)、执行机构、被控对象以及数模和模数转换器组成。

图1-1控制原理框图

本系统以单向上有三个车道的道路为实验模型,共使用了24个传感器设计的交通灯模糊控制系统比传统的交通灯控制系统平均节约7.8秒的等待时间。

而本人所要设计的交通灯控制器仅仅需要红绿两种颜色,控制两个干道的车辆,并且有5秒的闪烁时间以便提示车辆或者行人做好禁止通行准备.而此种设计已经可以用各种语言不同方式实现.我所使用的是较为简单的VerilogHDL语言编译程序,最终通过MAX+PLUS2这个全英文工具加以实现.

第二章.方案论证

2.1设计要求

设计一个十字路口交通信号灯的控制电路。

要求红、绿灯按一定的规律亮和灭,并在亮灯期间进行倒计时,并将运行时间用数码管显示出来。

绿灯亮时,为该车道允许通行信号,红灯亮时,为该车道禁止通行信号。

要求主干道每次通行时间为99秒,支干道每次通行时间为30秒。

每次变换运行车道前绿灯闪烁,持续时间为5秒。

即车道要由X转换为Y时,X在通行时间只剩下5秒钟时,绿灯闪烁显示,Y仍为红灯,以便X上已过停车线的车继续通行,未过停车线的车停止通行。

同理,当车道由Y转换为X时,Y绿灯闪烁显示5秒钟,X仍为红灯。

可以对X,Y车道上红、绿灯运行的时间进行重新设置。

对器件进行在系统编程和实验验证。

2.2方案设计

分析设计要求,交通灯的控制要保证在同一个时刻,只有一条干道是通行状态。

并且任一条干道的绿灯在运行时间只剩5秒的时候开始闪烁,而另一条干道的红灯继续亮,反之亦然。

设A方向是主干道,车流量大,B方向支干道。

A方向和B方向的红,黄,绿分别用R1,Y1,G1和R2,Y2,G2来表示。

(1)绿黄红黄绿由于本设计老师没有安排黄灯亮,仅可代表绿灯闪烁5秒的时间。

(2)在置数模块中,设四个并行的ALWAYS同时对四个置数键键控。

置数值分别放在chief_h,chief_l,sub_h,sub_l.

(3)每种灯亮的时间采用一个减法计数器进行记数,计数器用同步预置法设计,这样只需改变预置数据,就能改变计数器的模,因此每个方向只要一个记数器进行记时即可。

(4)为便于显示灯亮的时间,计数器的输出可采用BCD码,显示由四个数码管来完成,A方向和B方向各用两个数码管。

这样设计中就需要四条输出线,用来选通指定一个LED七段显示数码管;当正常计时开始后,需要进行定时技数操作,由于东西和南北两个方向上的时间显示器是由两个LED七段数码管组成的,因此需要产生两个2位的计时信息:

2个十位信号,2个个位信号,这个定时计数操作可以由一个定时计数起来完成,又因为交通灯的状态变化是在计时为0的情况下才能进行的,因此需要一个计时电路来产生使能信号,因此定时计数的功能就是用来产生2个2位计时信息和使能信号。

(5)采用自上而下的设计方法,将其分为各个小模块,然后连接最后达到最后的设计目的.交通灯状态图如下:

图2-1交通灯状态图

第三章.设计论述:

本设计的完成是运用VerilogHDL语言进行编译,用MAX+PLUS2软件来实现的。

对此我对VerilogHDL语言与MAX+PLUS2进行简单描述。

最后再详细介绍本设计的全部内容。

3.1.VerilogHDL语言:

1.VerilogHDL语言的发展过程:

VerilogHDL语言是在1983年由GDA(GateWayDesignAutomation)公司的PhilMoorby首创的:

在1984-1985年间,Moorby设计出第一个关于Verilog-XL的仿真器;1986年,又提出了用于快速门级仿真的XL算法。

随着Verilog-XL算法的成功,VerilogHDL语言得到迅速发展,1989年,CADENCE公司收购GDA公司,VerilogHDL成为CADENCE公司的私有财产。

1990年CANDENCE公司决定公开发表VerilogHDL,于是成立了OVI(OpenVeriloginternational)组织来负责VerilogHDL的发展。

基于VerilogHDL的优势,

IEEE于1995年制定了VerilogHDL的IEEE标准。

2.VerilogHDL的特点:

1.Verilog语言是一种通用的硬件描述语言,并且易学易用,在语法上和C语言类似。

2.同一个设计中,Verilog语言允许设计者在不同层次上进行抽象。

Verilog语言提供开关级,门级。

RTL级和行为级的支持,一个设计可以先用行为级语法描述它的算法,仿真通过后,再用RTL级描述,得到可综合的代码。

3.Verilog语言支持广泛,基本上所有流行的综合器,仿真器都支持此语言。

4.能够描述层次设计,可使用模块实例结构描述任何层次,模块的规模可以是任意的,语言对此没有任何限制。

5.Verilog语言对仿真提供强度的支持。

VerilogHDL语言中,描述进程的基本语句是always和initial.always过程反复执行其中的块语句,而initial过程中的语句块只执行一次.除了always和initial过程块外,一个assign赋值语句,一个实例元件的调用都可以看做是一个进程.在VerilogHDL语言中已预定义了门级原型:

表3-1

VerilogHDL行为描述方法:

过程块的组成:

过程语句@(事件控制敏感表)

begin(:

块名)

块内局部变量说明

一条或多条过程赋值或高级程序语句

end

在always下面使用的高级程序语句:

(1)if-else条件语句

if(条件表达式)块语句1

elseif(条件表达式2)块语句2

……..

elseif(条件表达式n)块语句n

else块语句n+1

(2)case语句

case(敏感表达式)

值1:

块语句1

值2:

块语句2

……

值n:

块语句n

default:

块语句n+1

endcase

(3)for循环语句

for(表达式1;表达式2;表达式3)块语句

3.2MAX+PLUS2的介绍:

本设计很关键的一步就是对MAX+PLUS2的学习,因为后面所涉及到的文本编译,建立模块,仿真都需要对此软件的熟练掌握才能很好的达到最终目的,因此我粗略的把使用MAX+PLUS2的基本流程描述一下。

我完成此设计是采用文本编译,然后建立模块最后实现仿真的。

使用MAX+plusII软件进行开发的流程如图3所示,主要包括以下步骤:

图3-1

而MAX+PLUS2可以采用两种方法来完成:

1.文本设计法。

2.图形输入法。

而我采用的第一种方法。

采用VerilogHDL进行文本设计的步骤如下:

1>指定项目并建立新文件;

2>输入文本设计文件;

3>文件命名、保存;

4>编译文件并检查、修改句法错误;

5>若需要,可生成默认逻辑符号。

以下我简单介绍下自己运用时的步骤:

1编译:

MAX+plusII的编译器能够接受多种输入文本格式,也能输出多种文件格式。

如前所述,它能接受的设计文件包括:

MAX+plusII自己的图形文件(.gdf)、AHDL文件(.tdf)、VHDL文件(.vhd)和VerilogHDL文件(.v);包括第三方EDA工具书输入文件,如EDIF文件(.edf)、库映射文件(.lmf)、OrCAD文件(.sch)及Xilinx文件(.xnf);它还能接受赋值和配置文件(.acf)。

另一方面,MAX+plusII的输出文件包括设计校验、MAX+plusII的模拟器网表文件(.snf)、第三方EDA工具所用的网表文件(.vo)和标准格式的SDF文件(..sdo)。

另外还可以输出可编程文件,包括用于E2PROM类器件编程的目标文件(.pof)、用于配置SRAM类器件的目标文件(.sof)和JEDEC文件(.jed)。

正常运行MAX+PLUS2后,先建立一个文件夹如123。

然后点FILE中的NEW出现如下图,选择TEXTEDITOR变会出现输入文本的空白界面,便可以输入你编的

程序,完成编译后进行保存。

然后点project建立工程并且使名字也和程序名一致。

然后点MAX+PLUS2中的compiler进行程序验证,如有错误便可按照提示查出错误进行改正,直到正确无误为止。

图3-2

2.波形仿真:

再点击FILE选择NEW出现上面同样的界面,这回选择waveeditorfile然后保存。

然后打开后出现图点击右键选择你要观察的引脚,将输入INPUT键入初始值。

点击MAX+PLUS2选择simulator进行仿真,点击start检验无误后便可以仿真了。

图3-3

图3-4

3.建立模块

完成以上内容后点FILE中的createdefaultsymbol,然后点NEW选择第一个GRAPLICEDITORFILE然后在空白中输入SYMBOL就会出现你要的模块。

这样整个过程就算初步完成,此后还有模块的整合在后面会叙述到。

此处就不再累赘。

MAX+PLUSII能够将设计的结果用层次显示方式显示出树的形式显示出整个项目和电路的设计层次。

打开层次显示窗口的方法是在MAX+PLUSII菜单中选择HierarchyDisplay项,选择后,当前项目的层次便显示出来。

图3.8是上例中模块mul4_look的结构层次,层次中的每个文件都可以通过双击文件名打开,并送到前台显示来。

它以一个层次:

图3-5

3.3.基于交通灯控制的设计论述:

本设计遵循着自上而下的方法来完成的,先建立各个小的模块最后再进行整合。

我们将整个分成设置模块,计时模块,显示模块与最终的顶层模块。

我完成计时控制模块和顶层模块。

简要介绍下置数模块和显示模块。

在置数模块中,ALWAYS语句中用置数键的上升沿跳变做触发。

每按次置数案键,便产生电平变化,对应的置数键加1。

当置数位加到9后下一次归0。

四个并行的ALWAYS同时对四个置数键监控。

置数值分别放在chief_h,chief_l,sub_h,sub_l’显示模块中完成交通灯的显示和闪烁功能。

我们完成的交通灯的逻辑功能如下:

通过外部:

chief_l_botton;chief_h_button;sub_l_button;sub_h_button,分别对主干道和次干道的通行时间进行设置。

在按下enable键后,交通灯开始运行。

运行时间以设置的值为初始值,以秒为单位进行减计数并且在数码管上显示。

并且保持交通灯的控制在同一时刻,只有一条干道是通行状态。

并且任何一条干道的绿灯在运行时间只剩下5秒钟的时间开始闪烁,而另一条干道的红灯继续亮。

反之亦然。

控制及译码表格:

输入信号

输出信号

select

flash

Chief_green

Chief_red

Sub_green

Sub_red

0

0

1

0

0

1

0

1

闪烁

0

0

1

1

0

0

1

1

0

1

1

0

1

闪烁

0

表3-2

所有的功能按键设置为脉冲模式chief_h_button(主干道通行时间置数高位键),chief_l_button(主干道通行时间置数低位键),sub_h_button(次干道通行时间置数高位键),sub_l_button(次干道通行时间置数低位键)。

每次置数从0开始,每按一次键加1,到9归零,依次循环(置数范围为0——99)。

整体电路图如下:

图3-6

其中输入端(INPUT)包括Enable控制计时器的运行和关闭.CLK为时钟脉冲.chief_h_button,chief_l_button,sub_h_button,sub_l_button则为四个控制两个干道的置数键.

输出端(OUTPUT)chief_green,chief_red,sub_green,sub_red接发光管.

其中闪烁的效果用flash&clk实现的.

既然采用的是自顶向下的设计思想,那么顶层的设计就很重用,顶层设计好后,下面各个部分写起来就比较容易了,一旦出了什么问题也好检查错误在哪里进行相应的改动。

3.3.1设计过程:

完成真个交通灯的设计主要经过了电路的分析,模块划分,程序的编译,模块的建立,波形的仿真,和最后模块的整合这几个步骤:

在设计中我主要负责计时模块和顶层模块的建立,所以本文只对此进行详细叙述,对另两个模块就不做详解。

(Enable键控制计时器的运行和关闭。

Enable按下后,将置数值赋给计数变量chief_h_temp,chief_l_temp,sub_h_temp,sub_l_temp.)

根据设计要求先将整个电路的输入输出规划出来。

其中输入:

一个运行控制键enable(按下后可以使交通灯运行,再按下后交通灯停止运行。

)一个时钟信号CLK,四个功能按键分别控制主干道高低位键,支干道高低位键。

(chief_h_button,chief_l_button,sub_h_button,sub_l_button)。

输出:

chief_green,chief_red,sub_green,sub_red(分别控制发光管)。

并且设置输出chief_h,chief_l,sub_h,sub_l可以控制数码管显示。

初步对电路分析后建立了一个系统的框架。

如图9所式:

而模块的划分是设计中要求的所以不必再做叙述。

、

图3-7系统框图

3.3.2计时模块

(1)程序的编译

我主要负责的是计时控制模块的编译,首先我们确定的是用文本输入的方法来实现。

在程序中完成了计时功能同时也完成了控制的功能:

初始状态,计数选择寄存器select=0,对主干道的计数变量进行减计数。

每到一个时钟上升沿,对变量减1。

建立一个文件夹并再在其中建立个名为jishi的文件夹,与程序同名,为以后整合时调用模块做依据。

然后点击file中的new选择text editor file。

根据以上的要求编译计时程序如下

Modulejishi(start,Initial,clk,chief_h,chief_l,sub_h,sub_l,enable,select,flash,chief_h_temp,chief_l_temp,sub_h_temp,sub_l_temp)

inputstart,enable;

inputclk;

inputchief_h,chief_l;

inputsub_h,sub_l;

inputInitial;

outputselect,flash;

outputchief_l_temp,chief_h_temp;

outputsub_l_temp,sub_h_temp;

always@(posedgeenable)

begin

start=~start;end

always@(posedgeclk)

begin

if(start)

begin

if(!

Initial)

begin

chief_l_temp<=chief_l;

chief_h_temp<=chief_h;

sub_l_temp<=sub_l;

sub_h_temp<=sub_h;

Initial<=1;

end

else

begin

if(!

select)

begin

if((chief_l_temp==0)&&(chief_h_temp>=1))

begin

chief_h_temp<=chief_h_temp-1;

chief_l_temp<=9;

end

if((chief_l_temp>=1)&&(chief_l_temp<=9))

begin

if((chief_h_temp==0)&&(chief_l_temp==5))

beginflash<=1;chief_l_temp<=chief_l_temp-1;end

elsechief_l_temp<=chief_l_temp-1;

end

elseif((chief_h_temp==0)&&(chief_l_temp==0))

beginselect<=1;flash<=0;end

end

elseif(select)

begin

if((sub_l_temp==0)&&(sub_h_temp>=1))

begin

sub_h_temp<=sub_h_temp-1;

sub_l_temp<=9;

end

if((sub_l_temp>=1)&&(sub_l_temp<=9))

beginif((sub_h_temp==0)&&(sub_l_temp==5))

beginflash<=1;sub_l_temp<=sub_l_temp-1;end

elsesub_l_temp<=sub_l_temp-1;

end

elseif((sub_h_temp==0)&&(sub_l_temp==0))

beginselect<=0;flash<=0;

chief_l_temp<=chief_l;

chief_h_temp<=chief_h;

sub_l_temp<=sub_l;

sub_h_temp<=sub_h;

end

end

end

end

else

begin

chief_l_temp<=0;

chief_h_temp<=0;

sub_l_temp<=0;

sub_h_temp<=0;

end

end

endmodule

说明:

当k1键按下,Enable为高点平时,定时器开始运行,否则定时器关闭。

clk上升沿触发,如果start为1,则将置数值赋给计数变量chief_h_temp,chief_l_temp,sub_h_temp,sub_l_temp;如果start为0,则chief_h_temp,chief_l_temp,sub_h_temp,sub_l_temp都将赋0值。

Select为计数干道选择寄存器,其初始值为0,对主干道的计数变量进行减计数。

每到来一个时钟上升沿,对变量减1。

其中有3种特殊情况:

(以主干道为例)

1chief_l_temp为0,chief_h_temp大于1时,chief_l_temp减1,chief_h_temp赋9。

2chief_l_temp大于1,小于9时,当chief_l_temp为5,chief_h_temp为0时,flash赋1,低位继续减,否则chief_l_temp减1。

3chief_l_temp为0,chief_h_temp等于0时,select赋1,flash赋0

当计数选择寄存器select=1,对支干道的计数变量进行减计数。

每到来一个时钟上升沿,对变量减1。

同样也要分三种情况讨论。

(2)建立计时控制模块

将上述程序保存到先设定的文件夹jishi中,然后点file进入project选择setprojectcurrentfile。

再对程序进行检查,选择MAX+PLUS2点compiler就可以检测了。

若有错误会出现提示,可以根据提示找到错误的行数进行纠错。

直至正确为止。

然后再次进入FILE点createDefaulesymbol生成模块。

然后建立一个新的.gdf文件,在空白处点右键选择entersymbol

便可以出现所设计出的模块,计时模块图如下:

图3-8计时控制模块

具体操作过程在前面的MAX+PLUS2中介绍过了在此不在多说。

3.3.3顶层模块:

(1)程序

顶层模块的建立是建在同组同学的模块与自己的子模块全部通过检测后完全通过的基础上的。

看到以下的部分程序代码为顶层模块的输入输出口:

定义的输入,输出的管脚;

moduletrafficlamp(enable,clk,chief_h_button,chief_l_button,

sub_h_button,sub_l_button,counter_play,

chief_green,chief_red,sub_green,sub_red,

chief_h,chief_l,sub_h,sub_l);

inputclk;

inputenable;

inputchief_h_button;

inputchief_l_button;

inputsub_h_button;

inputsub_l_button;

output[7:

0]counter_play;

outputchief_green,chief_red,sub_green,sub_red;

output[3:

0]chief_h,chief_l,sub_h,sub_l;

regflash;

regselect;

regstart;

regInitial;

reg[3:

0]chief_ltemp,chief_htemp;

reg[3:

0]sub_ltemp,sub_htemp;

reg[3:

0]chief_h,chief_l,sub_h,sub_l;

(2)建立顶层模块

将同组人员的设置模块,显示模块和本人的计时控制模块进行连接校对整合,从单个模块可以看出(图显示,设置模块图请看附录),各个模块间有相同的端口部分,将同名端口进行连线即可,将鼠标停留在路基函数脚位尾端,鼠标光标会变成“+”的形状,在此处按住鼠标并拖曳,可进行连接。

检测方法:

可选取连线的逻辑函数符号并拖曳,若线会跟着移动则代表连接成功。

同时注意线的粗细,若要更改连接线的类型,可在窗口菜单中选择OptionsLineStyle,选择接线类型。

当连接线传送多种信号时必须选用总线(实粗线),当连接线仅传送一种信号时最好使用缺省类型实细线。

(顶层模块图如图11)

图3-9顶层模块

第四章.结果分析

仿真中要学会如何去分析模块是否满足设计要