数电实验实验报告.docx

《数电实验实验报告.docx》由会员分享,可在线阅读,更多相关《数电实验实验报告.docx(18页珍藏版)》请在冰豆网上搜索。

数电实验实验报告

数字电路实验报告

实验一组合逻辑电路分析

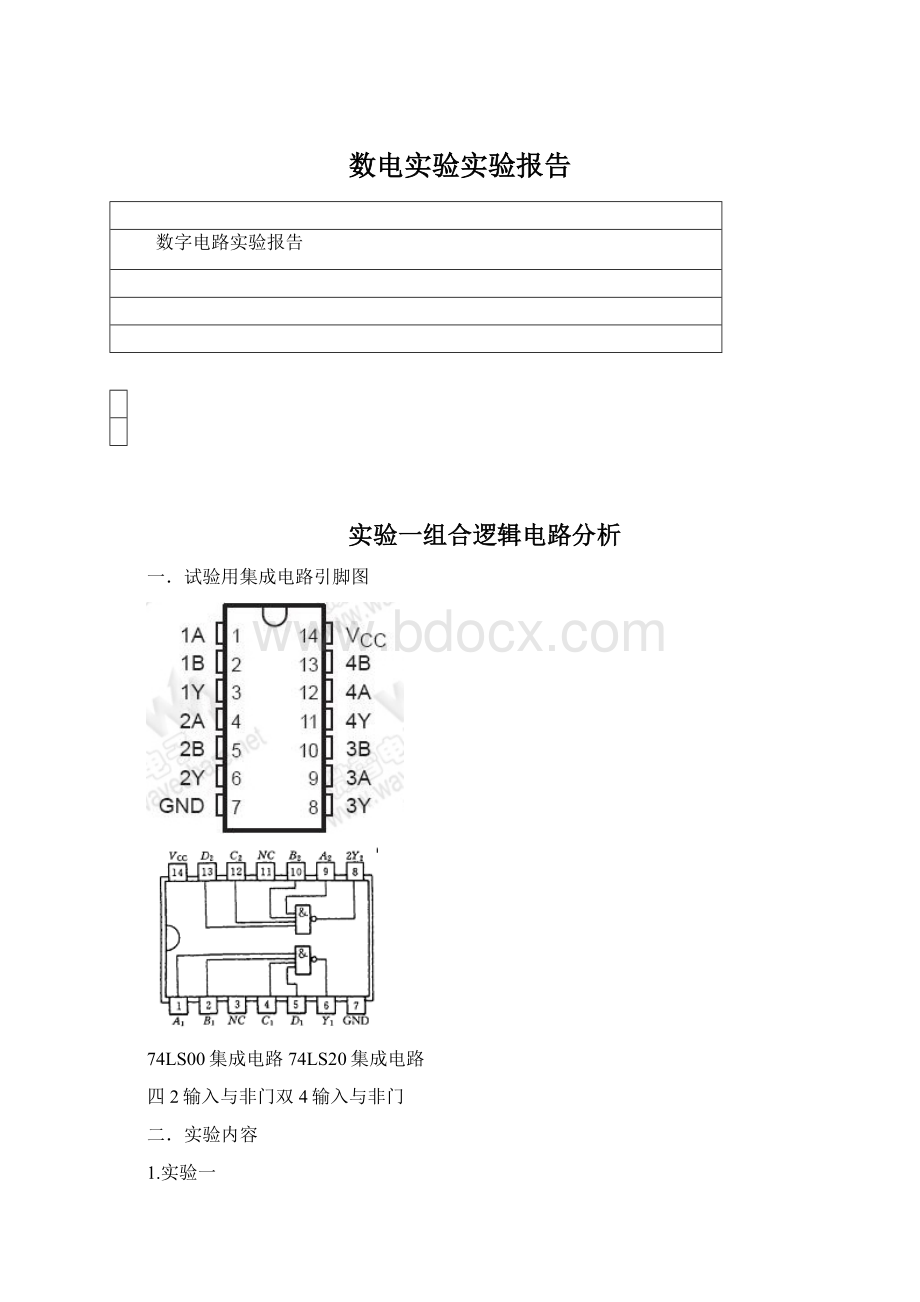

一.试验用集成电路引脚图

74LS00集成电路74LS20集成电路

四2输入与非门双4输入与非门

二.实验内容

1.实验一

自拟表格并记录:

A

B

C

D

Y

A

B

C

D

Y

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

1

0

0

1

0

0

0

1

0

0

1

0

1

0

0

0

0

1

1

1

1

0

1

1

1

0

1

0

0

0

1

1

0

0

1

0

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

1

1

0

1

0

1

1

1

1

1

1

1

1

1

2.实验二

密码锁的开锁条件是:

拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。

否则,报警信号为“1”,则接通警铃。

试分析密码锁的密码ABCD是什么?

ABCD接逻辑电平开关。

最简表达式为:

X1=AB’C’D密码为:

1001

表格为:

A

B

C

D

X1

X2

A

B

C

D

X1

X2

0

0

0

0

0

1

1

0

0

0

0

1

0

0

0

1

0

1

1

0

0

1

1

0

0

0

1

0

0

1

1

0

1

0

0

1

0

0

1

1

0

1

1

0

1

1

0

1

0

1

0

0

0

1

1

1

0

0

0

1

0

1

0

1

0

1

1

1

0

1

0

1

0

1

1

0

0

1

1

1

1

0

0

1

0

1

1

1

0

1

1

1

1

1

0

1

三.实验体会:

1.分析组合逻辑电路时,可以通过逻辑表达式,电路图和真值表之间的相互转换来到达实验所要求的目的。

2.这次试验比较简单,熟悉了一些简单的组合逻辑电路和芯片,和使用仿真软件来设计和构造逻辑电路来求解。

实验二组合逻辑实验

(一)半加器和全加器

一.实验目的

1.熟悉用门电路设计组合电路的原理和方法步骤

二.预习内容

1.复习用门电路设计组合逻辑电路的原理和方法步骤。

2.复习二进制数的运算。

3.用“与非门”设计半加器的逻辑图。

4.完成用“异或门”、“与或非”门、“与非”门设计全加器的逻辑图。

5.完成用“异或”门设计的3变量判奇电路的原理图。

三.元件参考

依次为74LS283、74LS00、74LS51、74LS136

其中74LS51:

Y=(AB+CD)’,74LS136:

Y=A⊕B(OC门)

四.实验内容

1.用与非门组成半加器,用或非门、与或非门、与非门组成全加器(电路自拟)

半加器

全加器

被加数Ai

0

1

0

1

0

1

0

1

加数Bi

0

0

1

1

0

0

1

1

前级进位Ci-1

0

0

0

0

1

1

1

1

和Si

0

1

1

0

1

0

0

1

新进位Ci

0

0

0

1

0

1

1

1

2.用异或门设计3变量判奇电路,要求变量中1的个数为奇数是,输出为1,否则为0.

3变量判奇电路

输入A

0

0

0

0

1

1

1

1

输入B

0

0

1

1

0

0

1

1

输入C

0

1

0

1

0

1

0

1

输出L

0

1

1

0

1

0

0

1

3.“74LS283”全加器逻辑功能测试

测试结果填入下表中:

被加数A4A3A2A1

0111

1001

加数B4B3B2B1

0001

0111

前级进位C0

0或1

0或1

和S4S3S2S1

1000

1001

0000

0001

新进位C4

0

0

1

1

五.实验体会:

1.通过这次实验,掌握了熟悉半加器与全加器的逻辑功能

2.这次实验的逻辑电路图比较复杂,涉及了异或门、与或非门、与非门三种逻辑门,在接线时应注意不要接错。

各芯片的电源和接地不能忘记接。

实验三组合逻辑实验

(二)数据选择器和译码器的应用

一.实验目的

熟悉数据选择器和数据分配器的逻辑功能和掌握其使用方法

二.预习内容

1.了解所有元器件的逻辑功能和管脚排列

2.复习有关数据选择器和译码器的内容

3.用八选一数据选择器产生逻辑函数L=ABC+ABC’+A’BC+A’B’C和L=A⊕B⊕C

4.用3线—8线译码器和与非门构成一个全加器

三.参考元件

数据选择器74LS151,3—8线译码器74LS138.

四.实验内容

1.数据选择器的使用:

当使能端EN=0时,Y是A2,A1,A0和输入数据D0~D7的与或函数,其表达式为:

Y=

(表达式1)

式中mi是A2,A1,A0构成的最小项,显然当Di=1时,其对应的最小项mi在与或表达式中出现。

当Di=0时,对应的最小项就不出现。

利用这一点,不难实现组合电路。

将数据选择器的地址信号A2,A1,A0作为函数的输入变量,数据输入D0~D7作为控制信号,控制各最小项在输出逻辑函数中是否出现,是能端EN始终保持低电平,这样,八选一数据选择器就成为一个三变量的函数产生器。

用八选一数据选择器74LS151产生逻辑函数

将上式写成如下形式:

L=m1D1+m3D3+m6D6+m7D7

该式符合表达式1的标准形式,显然D1、D3、D6、D7都应该等于1,二式中没有出现的最小项m0、m2、m4、m5,它们的控制信号D0、D2、D4、D5都应该等于0。

由此可画出该逻辑函数产生器的逻辑图。

L=ABC+ABC’+A’BC+A’B’C

用八选一数据选择器74LS151产生逻辑函数

根据上述原理自行设计逻辑图,并验证实际结果。

2.3线—8线译码器的应用

用3线—8线译码器74LS138和与非门构成一个全加器。

写出逻辑表达式并设计电路图,验证实际结果。

3.扩展内容

用一片74LS151构成4变量判奇电路

五、实验体会

1.数据选择器用来对数据进行选择,特别选择适用于函数的分离,是比较常用的组合逻辑器件;译码器用于数据的编码与译码中,也是较常用的逻辑器件。

2.集成的组合逻辑电路也是有简单的门电路组合而成,可以根据对逻辑电路的连接,集成的逻辑器件之间可以相互转化,功能也进行了扩展了。

实验四:

触发器和计数器

一、实验目的

1、熟悉J-K触发器的基本逻辑功能和原理。

2、了解二进制计数器工作原理。

3、设计并验证十进制,六进制计数器。

二、预习内容

1、复习有关R-S触发器,J-K触发器,D触发器的内容。

触发器是构成时序逻辑电路的基本逻辑单元,具有记忆、存储二进制信息的功能。

从功能上看,触发器可分为RS、D、JK、T、T’等几种类型。

上述几种触发器虽然功能不同,但相互之间可以转换。

边沿触发器是指,只有在时钟脉冲信号CP的上升沿或者是下降沿到来时,接收此刻的输入信号,进行状态转换,而在其它任何时候输入信号的变化都不会影响到电路的状态。

2、预习有关计数器的工作原理。

统计输入脉冲个数的过程计数。

能够完成计数工作的电路成为计数器。

计数器的基本功能是统计时钟脉冲的个数,即实现计数操作,也用于分频、定时、产生节拍脉冲等。

计数器的种类很多,根据计数脉冲引入方式的不同,将计数器分为同步计数器和异步计数器;根据计数过程中计数变化趋势,将计数器分为加法计数器、减法计数器、可逆计数器;根据计数器中计数长度的不同,可以将计数器分为二进制计数器和非二进制计数器(例如十进制、N进制)。

二进制计数器是构成其他各种计数器的基础。

按照计数器中计数值的编码方式,用n表示二进制代码,N表示状态位,满足N=2“的计数器称作二进制计数器。

74LS161D是常见的二进制加法同步计数器

3、用触发器组成三进制计数器。

设计电路图。

4、用74LS163和与非门组成四位二进制计数器,十进制计数器,六进制计数器。

设计电路图。

三、参考元件

74LS0074LS107

74LS7474LS163

四、实验内容

1.R-S触发器逻辑功能测试

R—S触发器

R

S

Q

触发器电位

0

1

0

1

0

1

0

1

0

1

1

1

0

0

不确定

0

0

不变

不变

保持

2.74LS163的逻辑功能测试

74LS163的逻辑功能表如下

输入

输出

CTP

CTT

CP

D0

D1

D2

D3

Q0

Q1

Q2

Q3

0

X

X

X

X

X

X

X

0

0

0

0

1

0

X

X

d0

d1

d2

d3

d0

d1

d2

d3

1

1

1

1

X

X

X

X

计数

1

1

0

X

X

X

X

X

保持

1

1

X

0

X

X

X

X

保持

3.用74LS163组成六进制计数器

输出QAQBQCQD从0000逐渐增1直至0101,此时QA=1,QC=1,经过与非门后为低电平,输入至CLR同步清零,又开始了下一轮的计数。

故计数范围为0000——0101,为六进制计数器。

4.用74LS163组成十进制计数器

输出QAQBQCQD从0000逐渐增1直至1001,此时QA=1,QD=1,经过与非门后为低电平,输入至CLR同步清零,又开始了下一轮的计数。

故计数范围为0000——1001,为十进制计数器。

1、用74LS163组成六十进制计数器

五、实验体会:

这次试验熟悉了计数器、译码器、显示器等器件的使用方法,学会用它们组成具有计数、译码、显示等综合电路,并了解它们的工作原理。

利用常用计数器通过设计可以实现非常用进制计数器,一般有同步和异步两种不同的方案,同时也可以采用清零和预置数来达到归零的目的。

实验五555集成定时器

一.实验目的

熟悉与使用555集成定时器

二.实验内容

1.555单稳电路

1)按图连接,组成一个单稳触发器

2)测量输出端,控制端的电位与理论计算值比较

3)用示波器观察输出波形以及输出电压的脉宽。

tw=RCln3=1.1RC

2.555多谐振荡器

1)按图接线,组成一个多谐振荡器

输出矩形波的频率为:

f=1.43/(R1+2R2)

2)用示波器观察波形

通过示波器观察到输出波形为脉冲波

3.接触开关

按图接线,构成一个接触开关,摸一下触摸线,LED亮一秒

三.实验体会

本次实验是关于555集成定时器以及它构建的触发器和振荡器。

555定时器在逻辑电路中用得非常广泛,可以由它产生各种各样的脉冲波形,一般作为信号源来使用。

实验六数字秒表

一.实验目的:

1、了解数字计时装置的基本工作原理和简单设计方法。

2、熟悉中规模集成器件和半导体显示器的使用。

3、了解简单数字装置的调试方法,验证所设计的数字秒表的功能。

二.实验元件:

集成元件:

555一片,74LS163一片,74LS248两片,LED两片,74LS00两片。

二极管IN4148一个,电位器100K一个,电阻,电容。

三.实验内容:

1、实验原理框图

1秒信号发生器用555定时器构建多谐振荡电路而成

2六十进制计数器用两块74LS163组成

3译码电路由74LS148组成

4数码显示由LED组成。

2、设计内容及要求

①用上述元器件设计一个数字秒表电路,电路包含秒脉冲发生器、计数、译码,显示00至59秒。

②具有清零、停止、启动功能。

③至少使用一块74LS248芯片及共阴极显示器。

3实验电路图设计如下:

开关AB置于高电平时开始计数,A置于低电平的时候暂停计数,B置于低电平的时候清零。

四.实验体会:

最后的实验为一综合性实验,综合考察了555定时器与计数电路的应用。

其中在接线时应先检查导线的通断后在使用,可以节省不必要浪费的时间;另外要将电路分割成不同的功能块来拼接会是过程清晰、简洁。

由多谐振荡器产生的信号接入计数器时应用与非门来处理一下,否则计数器会出现乱码,可见理论与实际是有偏差的,可能是多谐振荡器产生的方波中有干扰信号。