EDA实训报告FPGA的最小硬件系统设计.docx

《EDA实训报告FPGA的最小硬件系统设计.docx》由会员分享,可在线阅读,更多相关《EDA实训报告FPGA的最小硬件系统设计.docx(17页珍藏版)》请在冰豆网上搜索。

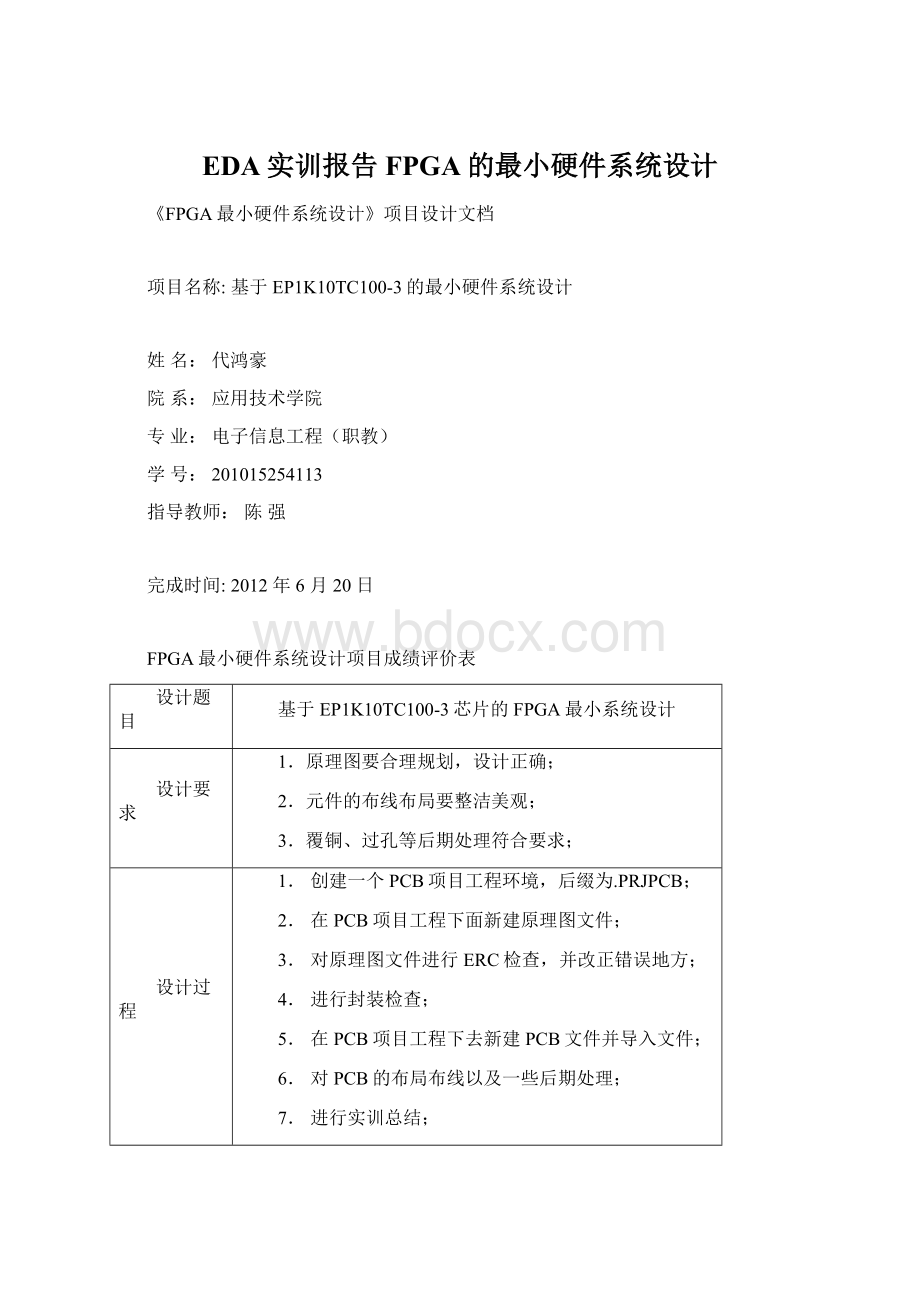

EDA实训报告FPGA的最小硬件系统设计

《FPGA最小硬件系统设计》项目设计文档

项目名称:

基于EP1K10TC100-3的最小硬件系统设计

姓名:

代鸿豪

院系:

应用技术学院

专业:

电子信息工程(职教)

学号:

201015254113

指导教师:

陈强

完成时间:

2012年6月20日

FPGA最小硬件系统设计项目成绩评价表

设计题目

基于EP1K10TC100-3芯片的FPGA最小系统设计

设计要求

1.原理图要合理规划,设计正确;

2.元件的布线布局要整洁美观;

3.覆铜、过孔等后期处理符合要求;

设计过程

1.创建一个PCB项目工程环境,后缀为.PRJPCB;

2.在PCB项目工程下面新建原理图文件;

3.对原理图文件进行ERC检查,并改正错误地方;

4.进行封装检查;

5.在PCB项目工程下去新建PCB文件并导入文件;

6.对PCB的布局布线以及一些后期处理;

7.进行实训总结;

项目设计成绩评价

评价项目

指标

满分

评分

工作量、工作态度和出勤率

按期圆满的完成了规定的任务,难易程度和工作量符合教学要求,工作努力,遵守纪律,出勤率高,工作作风严谨,善于与他人合作。

30

课程设计质量

项目设计最小系统架构合理,设计过程简练正确,分析问题思路清晰,结构严谨,文理通顺,撰写规范,图表完备正确。

40

创新

工作中有创新意识,对前人工作有一些改进或有一定应用价值。

15

答辩

能正确回答指导教师所提出的问题。

15

综合成绩等级

指导教师:

年月日

目录

1设计项目名称、内容与要求…………………………………1页

1.1设计内容…………………………………………………1页

1.2具体要求…………………………………………………1页

2FPGA最小系统硬件电路整体架构……………………………1页

2.1系统总体原理框图与设计说明…………………………1页

2.2最小系统原理图设计与PCB设计工具介绍……………1页

3FPGA最小系统硬件电路原理图设计…………………………3页

3.1基于AltiumDesigner的原理图设计流程……………3页

3.2单元电路原理图分析与设计……………………………4页

3.3FPGA最小系统整体电路原理图与元器件清单…………6页

4FPGA最小系统电路PCB板设计……………………………6页

4.1基于AltiumDesigner的PCB设计流程………………6页

4.2最小系统电路PCB板设计………………………………7页

4.3FPGA最小系统硬件电路整体PCB版图…………………11页

5总结(Closing)……………………………………………12页

参考书目(Reference):

……………………………………12页

附录(Appendix):

……………………………………………13页

1设计项目名称、内容与要求

1.1设计内容

AltiumDesigner中以设计项目为中心,一个设计项目中可以包含各种设计文件,如原理图SCH文件,电路图PCB文件及各种报表,多个设计项目可以构成一个ProjectGroup(设计项目组)。

因此,项目是AltiumDesigner工作的核心,所有设计工作均是以项目来展开的。

完成FPGA最小EP1K10TC100-3芯片的系统的PCB、原理图的设计。

1.2具体要求

﹝1﹞掌握FPGA开发板的六大组成部分的设计。

﹝2﹞初步掌握AltiumDesigner的使用,设计流程。

﹝3﹞掌握AltiumDesigner的高级设计方法。

﹝4﹞完成FPGA最小EP1K10TC100-3芯片系统的PCB、原理图的设计。

﹝5﹞学习调试方法;探讨FPGA最小EP1K10TC100-3芯片系统设计。

﹝6﹞FPGA的开发流程及设计方法。

2FPGA最小系统硬件电路整体架构

2.1系统总体原理框图与设计说明

﹝1﹞原理框图

﹝2﹞电源电路采用LT1086-3芯片和LT1587-芯片,将输入的电压+5V直流转换为电压为+3V和+1.5V电源,复位电路采用高低电平控制;

﹝3﹞显示电路采用依次显示的6个7端数码管进行显示;

﹝4﹞下载电路采用JTAG模式进行计算机与芯片之间的数据传递;外部时钟电路将产生频率可调的秒脉冲信号。

2.2最小系统原理图设计与PCB设计工具介绍

在AltiumDesigner中进行原理图设计的具体步骤如下。

2.2.1新建PCB项目及原理图文件

AltiumDesigner中的设计是以项目为单位的,通常一个PCB设计项目中包含原理图文件和PCB文件,在进行原理图设计前,需要创建一个PCB设计项目,然后再在新建的PCB项目中添加空白原理图文档,当打开新建的原理图文档时,系统会自动进入原理图编辑界面。

2.2.2设置原理图编辑界面的系统参数和工作环境

为适应不同用户的操作习惯,以及不同的项目的原理图格式需求,AltiumDesigner允许用户设置原理图编辑界面的工作环境,例如设置网格的大小和类型以及鼠标指针类型等,其中大多数参数都可以用系统默认值,但根据用户个人习惯来适当调整环境设置,将会给

设计者带来方便,显著提高设计效率。

在对原理图编辑界面进行调整后,用户还需要对原理图的图纸尺寸及版面进行设置,以满足图纸使用者的要求,图纸的格式、规格要根据实际情况进行选择,良好的图纸格式会使图纸管理工作变得更加轻松。

尤其是在一个项目中包含多张原理图的时候。

2.2.3布置元件并调整元件属性和布局

这一步是原理图设计的关键,用户根据实际电路的需要,选择合适的电子元件,然后载入包含所需元件的集成元件库,从元件库中提取元件放置到原理图的图纸上,同时还须设定零件的标识、封装等属性。

对于当前元件库中没有的元件,则可以自行定义。

在布置新建PCB项目及原理图文件元件时,元件之间的位置要尽量合理,这样能减少原理图布线过程的工作量,提高原理图的可读性。

2.2.4原理图布线

原理图布线就是利用“Wiring”工具栏中的连线工具将图纸上的独立元件用具有电气意义的导线、符号连接起来,构成一个完整的原理图。

2.2.5检查、仿真、校对及线路调整

当原理图绘制完成以后,用户还需要利用系统所提供的各种工具对项目进行编译,找出原理图中的错误,进行修改,如有需要,也可以在绘制好的电路图中添加信号进行软件模拟仿真,检验原理图的功能。

2.2.6输出报表,保存文件

原理图校对结束后,用户可利用系统提供的各种报表生成服务模块创建各种报表,例如网络列表、元件列表等。

为后续的PCB板设计做准备。

获得报表输出后,保存原理图文档或打印输出原理图,设计工作结束。

PCB板设计流程图设计过程介绍如下:

2.2.1绘制编译原理图

绘制编译原理图是PCB板设计的准备工序,设计者将其设计的电路采用原理图的形式输入系统,通过编译过程检验原理图设计是否满足原理图设计规则的要求,同时生成连线网络,这些工作步骤在前几章已经作了详细介绍。

在特殊情况下,例如电路比较简单的情况下可以不进行原理图设计而直接进入PCB板的设计过程,然后在PCB编辑器中手工布线或者利用网络管理器人工创建网络表后进行交互布线。

2.2.2添加PCB文件

这一步是PCB板设计中的第一步,首先必须在已有的项目中添加新的PCB文件,这样,该PCB文件就与该项目中的原理图联系起来,这是非常重要的,新建的PCB文件还需要设置一些主要参数,例如:

电路板的结构及其尺寸、PCB板的层数、格点的大小和形状。

一般情况下大多数参数可以用系统的默认值。

2.2.3同步PCB文件

同步PCB文件是将原理图中的内容与PCB文件中的内容同步起来,这种同步是通过网络列表来实现的,网络列表示描述电路连接的列表文件,是连接原理图设计和PCB板设计的纽带,同步过程中,系统会显示同步操作将对PCB文件进行得的修改内容,用户可以逐个选择是否进行修改,这个过程将在以后详细介绍。

同步完成后,PCB文件中将具有原理图中所有元件的PCB封装,以及元件的连接关系。

2.2.4PCB板元件布局规则设置

好的元件布局是布线成功的保障,AltiumDesigner中提供了自动布局的功能,可以按照用户设置的布局规则,自动进行元件位置的布局。

即使用户采用交互布局的方式进行布局,系统也会自动检查当前布局状态,显示当前违反布局规则的错误或警告。

降低由于布局失误为后续工作带来的麻烦。

为得到一个满意的元件布局,用户必须设置好PCB板元件布局规则。

2.2.5布线规则设置

布线规则是布线时依据的各个规范,如安全间距、导线宽度等,这是对自动布线的约束。

布线规则的设置也是印制电路板设计的关键之一,需要一定的实践经验,布线规则设置不能过高也不能过低,当约束条件设置得过高,给布线带来较大的困难,会使布线成功率降低,约束条件设置得过低,不限质量将受到影响,会给实际产品带来隐患,甚至无法满足实际需要。

2.2.6输出生产制造文件

在绘制完成PCB板后,系统可以生成各种生产制造文件和输出报表,例如PCB光绘文件“Gerber”、数控钻文件“NCdrill”、元件插置文件“PickandPlace”和材料清单报表等,使用这些文件,设计者就可以开始批量生产PCB板以及进行元件自动焊接。

3FPGA最小系统硬件电路原理图设计

3.1基于AltiumDesigner的原理图设计流程

电路原理图设计是EDA设计的基础,原理图设计的大致流程如图1所示。

设计过程介绍如下。

3.2单元电路原理图分析与设计

3.2.1电源电路模块和复位电路

该电路实现对输入+5V到输出+3V和+1.5V电压的转换,以及利用稳压二极管对输入电源进行稳压;复位电路是采用高低电平原理对芯片的nCONEIG管脚控制,达到复位的作用。

3.2.2滤波电路模块

采用电容并联,对变压之后的+3V和+1.5V电源进行滤波。

3.2.3外部时钟电路

由+5V电压利用NE555JG芯片产生频率可调的脉冲信号

3.2.4下载电路

采用JTAG配置模式,利用计算机并行口进行计算机和芯片之间的数据传递。

3.2.5显示电路

数码管采用逐一显示的原理,利用74LS138对公共阴极进行控制,始终显示一个,显示的时候利用动态扫描程序,显示出肉眼不能分辨的动态显示。

3.3FPGA最小系统整体电路原理图与元器件清单

3.3.1系统原理

利用AltiumDesigner6软件对电路进行设计,电路采用分块设计,对电源电路和复位电路、电源滤波电路,下载电路、外部时钟电路以及显示电路分开模块化进行设计。

原理图如下所示

FPGA最小系统原理图

3.3.2元器件清单

4FPGA最小系统电路PCB板设计

4.1基于AltiumDesigner的PCB设计流程

利用AltiumDesigner设计PCB板通常需要经过,同步PCB文件、元件布局、PCB布线等几个步骤,其具体的的流程图如图2所示。

4.2最小系统电路PCB板设计

AltiumDesigner新建PCB工程

文件——>新建——>工程——>PCB工程如图所示,单击此处,新建PCB工程。

2.7给新建的PCB工程添加原理图文件

单击如图所示的Schematic选项,出现空白原理图,然后对图纸按要求进行一些必要的设置,然后进行原理图的编辑。

2.8原理图的ERC(电器规则)检查

如上图所示对原理图进行ERC(电器规则检查),如果有错误的话,将会弹出一个Message信息框,提醒错误的地方,然后单击错误将会在原理图错误的地方出现高亮,对错误的地方进行必要的修改,直到没有错误出现。

2.9对元器件进行封装的检查

检查是否每个元器件都有封装,如果某些元器件没有封装的话,从原理图到PCB文件的导入将会出现封装的缺失,PCB板错误。

所以检查之后要将差封装的元器件封装加上,以便能够正确导入,不使PCB板出错。

2.10给FPGA工程添加新的PCB文件

添加PCB文件以后,对PCB板进行参数设置,比如说板子形状、尺寸、布线规则等的设置,然后单击保存,因为如果不保存的话是将不能从原理图导入到PCB文件。

2.11PCB文件的设计

使原理图和PCB文件同时处于打开状态,并使原理图文件处于当前工作窗口中。

单击原理图编辑器的“设计”|“UpdatePCBDcoumentPcb1.PcbDoc”菜单如图所示

单击之后选择如下图所示的使更改生效,看是否有错误的地方,如果有错误还回到原理图进行改正,如果没有错误选择执行更改。

导入之后的PCB文件窗口如下图所示

然后对元器件进行布局和布线,布局布线之后的PCB文件如下图所示

4.3FPGA最小系统硬件电路整体PCB版图

5总结(Closing)

在为期两周的实训课程,从中让我深刻的理解到了从一个原理图到一个真正的PCB板文件夹的的设计过程,通过查询资料和不断的实践对AltiumDesigner软件进行电路图和PCB板的设计有了深刻的认识。

电路的设计从模块化分部份进行逐一设计,然后包括对电路中的模拟地和数字地的处理都有了比较深刻的认识。

对PCB各种参数的设置以及对覆铜的各种要求和覆铜之后对电路板起到的作用都有着一定的了解。

在制作FPGA开发板之前不光是要熟悉AltiumDesigner这个设计软件,还要对FPGA开发板有一定的了解,包括开始准备过程中对芯片的熟悉了解,对芯片管脚进行查询和对各个管脚在电路中所起到的不同作用。

以前使用开发板不知道开发板是如何实现计算机与芯片之间的数据的传递,现在对这些都有了很深刻的认识,包括各种下载配置模式等。

虽然由于条件限制,没能够将自己制作的PCB板实物,但是这次实训让我对电路的设计增添了不少兴趣,通过这次实训,让自己学习的理论知识得到了应用,以及在老师的带领下,解决在实训过程中遇到的各种难题,克服各种困难,为以后工作打下了一定的基础。

参考书目(Reference)

[1]李辉.PLD与数字系统设计.[M].西安电子科技大学出版社,2005

[2]陈学平兰帆胡勇.Protel2004电路设计与电路仿真.北京:

清华大学出版社,2007

[3]张义和.AltiumDesigner完全电路设计.北京:

机械工业出版社,2007

[4]《CPLD技术及其应用》宋万杰等编著,西安电子科技大学出版社,2000-6

[5]《CPLD/FPGA的开发与应用》徐志军等编著,电子工业出版社,2002-7

[6]《基于CPLD/FPGA的数字通信系统建模与设计》作者:

段吉海黄智伟电子工业

出版社出版日期:

2004年8月。

[7]《数字电子技术基础》(第四版),阎石主编,高教出版社

[8]陈立万等.脉冲与数字电路.北京:

中国物资出版社.2003

[9]《VHDL实用教程》(修订版)潘松王国栋电子科技大学出版社2001.7

附录(Appendix)

管脚说明:

用户I/O:

输入输出管脚。

MSEL[1:

0]用于选择配置模式,比如AS、PS等。

DATA0FPGA串行数据输入,连接到配置器件的串行数据输出管脚。

DCLKFPGA串行时钟输出,为配置器件提供串行时钟。

nCSO(I/O)FPGA片选信号输出,连接到配置器件的nCS管脚。

ASDO(I/O)FPGA串行数据输出,连接到配置器件的ASDI管脚。

nCEO下载链期间始能输出,在一条下载链中,当第一个器件配置完成后,此信号将始能下一个器件开始进行配置。

下载链上最后一个器件的nCEO悬空。

nCE下载链器件始能输入,连接到上一个器件的nCEO,下载链的最后一个器件nCE接地。

nCNFIG用户模式配置起始信号。

nSTATUS配置状态信号。

CONF_DONE配置结束信号。

VCCINT内核电压。

130nm为1.5V,90nm为1.2V。

VCCIO端口电压。

一般为3.3V,还可以支持多种电压,5V、1.8V、1.5V的VREF参考电压。

GND信号地 。

VCC_PLLPLL管脚电压,直接连VCCIO。

VCCA_PLLPLL模拟电压,截止通过滤波器接到VCCINT上。

GNDA_PLLPLL模拟地

GNDD_PLLPLL数字地。

CLK[n]PLL时钟输入。

PLL[n]_OUTPLL时钟输出。

VCCPD用于寻则驱动。

VCCSEL用于控制配置管脚和PLL相关的输入缓冲电压。

PROSEL上电复位选项。

NIOPULLUP用于控制配置时所使用的用户I/O的内部上拉电阻是否工作。

TEMPDIODEN用于关联温度敏感二极管