计算机系统结构基础习题.docx

《计算机系统结构基础习题.docx》由会员分享,可在线阅读,更多相关《计算机系统结构基础习题.docx(22页珍藏版)》请在冰豆网上搜索。

计算机系统结构基础习题

第三.四章习懸一、选择题

1.对真值0表示形式唯一的机器数是_B。

A.原码B.补码和移码C.反码D.以上都不对

2.某机字长8位.采用补码形式(其中1位为符号位),则机器数所能表示的围是

C。

A.-127^127B.-128^128C・一128~+127D.0、255

3•用n+1位字长表示定点数(其中1位为符号位),它所能表示的整数国是_A—,它所能表示的小数围是—D

A.OWINIW21B・0WINIW2宀一1

C・OWINIWl-2-wD・0WINIW1—2-

1-订机器数釆用补码形式(含1位符号位),若寄存器容为9BH,则对应的十进制数为C

A.-27B.-97

C.-101D.155

5.若9BH表示移码(含1位符号位人其对应的十进制数是—A移码符号位用1表示正数,用0表示负数

A.27B.-27

C.-101D.101

6.设奇存器容为10000000.(移码,符号位为1,表示正0)若它等于0,则为

A.原码B.补码

C.反码D.移码'

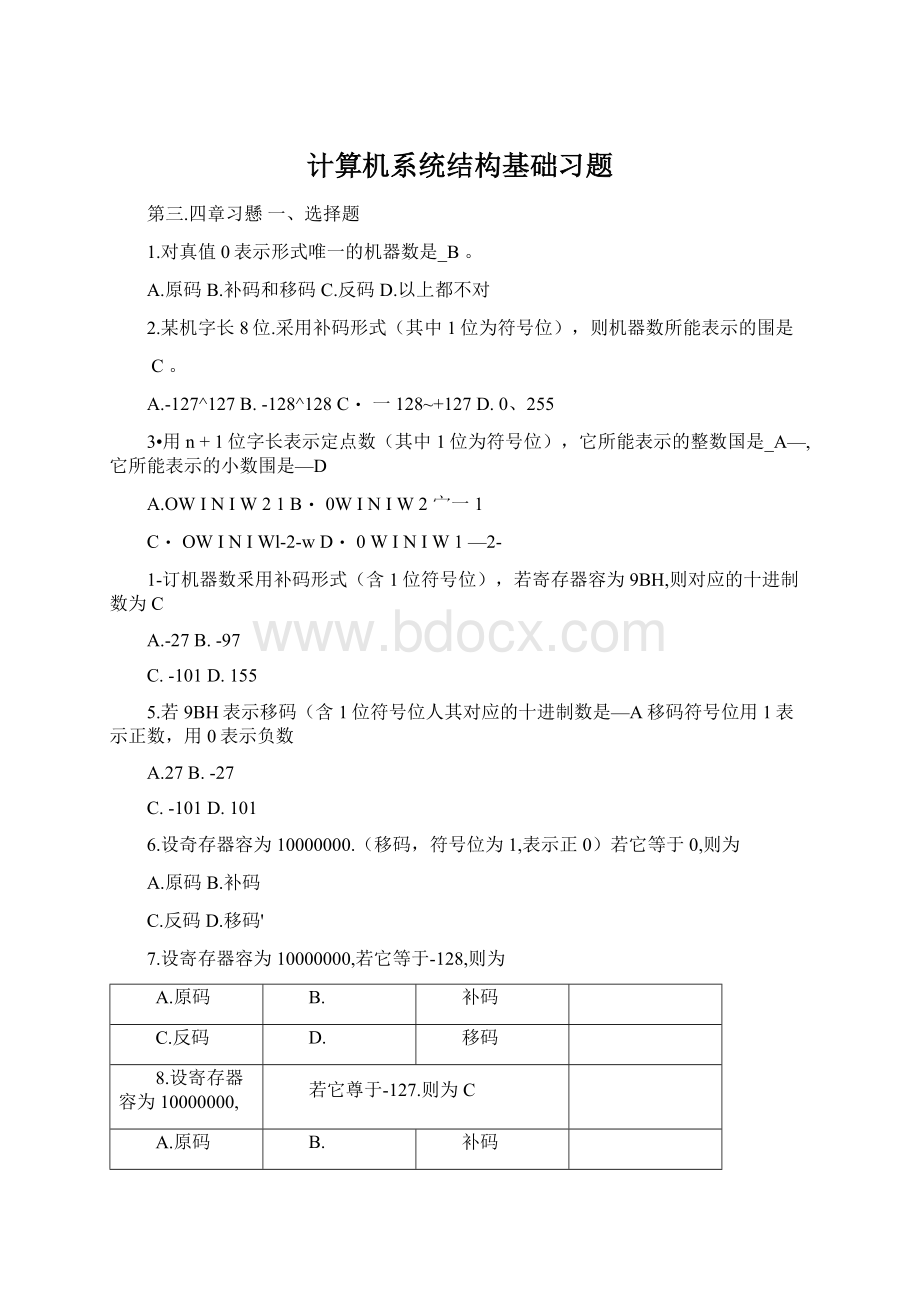

7.设寄存器容为10000000,若它等于-128,则为

A.原码

B.

补码

C.反码

D.

移码

8.设寄存器容为10000000,

若它尊于-127.则为C

A.原码

B.

补码

C.反码

D.

移码

9.设寄存器容为10000000,

若它等于-0,则为

A

0

A.原码

B.

补码

C.反码

D.

移码

10・设寄存器容为11111111,若它等于H27,则为

A.原码B.补码

C反码D.移码

11・大部分计算机的减法是用实現。

A将被减数加到絨数中B从被减数中减去减数

C补数的相加

I)从减数中减去被絨数

在原码一位乘中,符号位单独处理,参加操作的数是

A最高位有进位

B最高位进位和次高位进位异或结果为0

C最高位为1

D最高位进位和次高位进位异或结果为1

15.在定点机中执行算术运算时会产生溢出,其原因是

16.在浮点机中,下列说法_—是正确的。

A.尾数的第一数位为1时,即为规格化形式。

B.尾数的第一数位与数符不同时,即为規格化形式。

C.不同的机器数有不同的规格化形式。

D.尾数的第一数位为0时,即为规格化形式。

17.在浮点机中,判断原码规格化形式的原则是_

A.尾数的符号位与第一数位不同

B.尾数的第一数位为1,数符任意。

C.尾数的符号位与第一数位相同。

D.阶符与数符不同。

18.在浮点机中,判断补码规格化形式的原则是。

A.尾数的第一数位为U数符任意。

B•尾数的符号位与第一数位相同。

C.尾数的符号位与第一数位不同。

D.阶符与数符不同。

19.设机器数字长8位(含1位符号位人若机器数BHA为原码,则算术左移一位得•算术右移一位得

A.F4IIEDHB.B4H6DH

C.E4II9DUD.B5HEDH

20.运算器的主要功能是进行。

A.算术运算。

B.逻辑运算

C.算术逻辑运算D.初等函数运算

21•运算器由许多部件组成.其核心部分是。

A.数据总线B•算术逻辑运算单元

C.累加寄存器D.多路开关

22.定点运算澤用来进行。

A.十进超数的加法运算

B.定点运算

C.浮点运算

D.既进行浮点运算也进行定点运算。

23•串行运算器结构简单,其运算规律是。

A.由低位到高位先行进行进位运算

B.由高位到低位先行进行进位运算

C.由低位到高位逐位运算

D.由高位到低位逐位运算

21.四片74181和一片74182相配合,具有如下种仅为传递功能。

A.行波进位

B.组(小组)并行进位,组(小组)问并行进位

C.组(小组)并行进位,组(小组〉问行波进位

D.组行波进位,组问并行进位

25•早期的硬件乘法器设计中,通常釆用加和移位相结合的方法,具体算法是,但

需要有控制。

A.串行加法和串行移位

触发器

B.并行加法和串行左移

计数器

C.并行加法利串行右移

计数器

D.串行加法和串行右移

触发器

25.下面有关浮点运算器的描述正确的是—•(多项选择)。

A.浮点运算器可用两个松散连接的顶点运算部件(阶码部件和尾数部件)来实现

B.阶码部件可实現加、减.乘、除四种运算

C.阶码部件只进行加、减和比较操作

D.尾数部件只进行乘、除操作

26•计算机中表示地址时,釆用o

A.原码B.补码

C.反码D.无符号数

27.浮点数的表示围和精度取决于・

A.阶码的位数和尾数的机器数形式

B.阶码的机器数形式和尾数的位数

C.阶码的位数和尾数的位数

D.阶码的机器数形式和尾数的机器数形式

28.崔浮点机中是隐含的。

A.阶码

B.数符

C.尾数

D.基数

29.ALU属于o

A时序电路B组合逻辑电路

C控制器D寄存器

30.在运算器中不包含。

CALUD地址寄存器

31.下列叙述中正确的是。

(多项选择)

A定点补码运算时,其符号位不参加运算

B浮点运算可白阶码运算利尾数运算两部分组成

C阶码部件在乘除运算时只进行加、减操作

D浮点数的正负由阶码的正负符号决定

E尾数部件只进行乘除运算

32加法弄采用先行进位的目的是o

A优化加法器的结构

B节省器材

C加速传递进位信号

D増强加法器结构

33在定点补码运算器中,若采用双符号位,当时表示结果溢出。

A双符号位相同B双符号位不同

C两个正数相加I)两个负数相加

34下列说法中是错误的。

A符号相同的两个数相见时不会产生溢出的

B符号不同的两个数相加是不会产生溢出的

C逻辑运算是没有进位或错位的运算

D浮点乘除运算需进行对阶操作

35釆用規格化的浮点数是为了。

A増加数据的表示围B方便浮点运算

C防止运算时数据溢出I)增加数据的表示精度

36•在浮点数加减法的对阶过程中,。

A.将被加(减)数的阶码向加(减)数的阶码看齐

B.将加(减)数的阶码向被加(减)数的阶码看齐

C.将较大的阶码向较小的阶码看齐

D.将较小的阶码向较大的阶码看齐二、填空燧

1・设机器数字长8位(含1位符号位),若机器数为80H(十六进制),当它分别代表原码、补码、反码.和移码时,等价的十进制整数分别为—A_、—B_、—C_和—D_。

2•釆用浮点表示时,若尾数为规格化形式,则浮点数的表示国取决于—A_的位数,精度取决于—B_的位数,—C—确定浮点数的正负。

3.巳知寄存器位数为8位,机器数取1位符号位,设其容为1110101当它代表无符号数时,逻辑左移一位后得—A_,逻辑右移一位后得—B_o当它代表补码时,算术左移一位后得—C_,算术右移一位后得—D_。

4•浮点运算器由—A_和—B_组成,它们都是—C_运算器。

前者只要求能执行—D_运算,而后者要求能进行—E_运算。

5•現代计算机中,通常将运算器和—A_制作在一个芯片,称为—B_芯片。

6•先行进位指的是—A_。

7•运算器由许多部件组成,除寄存器外,其核心部件是—A_,记为—B_o

8•若移码的符号为1,则该数为—A_如若符号为0,则为—B_数。

9•在原码.补码、反码和移码中,—A_对0的表示有两种形式,—B_对0的表示只有中形式。

10・设机器宇长位8位.-1的补码在整数定点机中表示为—A_,在小数定点机中表示为—B_o

三、问答题

1•设浮点数字长16位,其中阶码5位(含1位阶符人尾数11位(含1位数符人写出(-29/1024)对应的浮点規格化数的原码.补码.反码、和阶码用移码.尾数用补码形式。

2.巳知十进制数x-41•严+101.设机器数宇长8位(含1位符号位〉计算[x+y]补和[x-y]补,并给出相应的Z(零标志)、V(溢出标志)利C(进位标志)。

3.巳知十进制数x=25/32•尸-21/64.设机器数宇长8位(含1位符号位)计算[x+y]补和[x-y]补,并给出相应的Z(零标志)、V(溢出标志)和C(进位标志)。

4•巳知二进钢数x二-0.1100,y二0.1001,按一位乘法计算x*y,要求列出详细过程,机器数形式自定。

5.设X=0.1101x2,0,y=-0.1111x2"

其阶码5位(含2位阶符),补码表示:

尾数7位(含2位数符),补码表示;求X+Y二?

6•在定点机中采用单符号位,如何判断补码加减运算是否溢出,有几种方案?

参考答案

一、选择题

1.

B

11.C

12.C

13.C

14.D

15.B

16.C

17.B

18.C

19.C

20.C

21.B

22.B

23.C

24.B

25.C

26.D

27.C

2&D

29.B30.D

31.BC

32.C

33.B

34.D

35.D

36.D

二、填空题

1.A.-0

B.-128

C.-127

D.±0

2.A•阶码

B.尾数

C.数符

3.A.11101010B.01111010C.11101010D.11111010

4.A•阶码运算器B.尾数运算弄C・定点D.加减E・加减乘除

5.A.控制器B.CPU

6.A.高位的进位不必等低位的进位产生后再形成,高位的进位与低位的进位同时产生

7.A•算术逻辑运算单元B.ALU

8.A•正B.负

9.A.原码、反码B.反码.补吗

10.A.1J111111B.1.0000000

三、问答题

1•设:

x=(-29/1024)lo=-0.0000011101-2101X(-0.1110100000)

[X]原二1,0101:

1.1110100000

[X]补二1,1011;1.0001100000

[X]反=1,1010:

L0001011111

阶码用穆码,尾数用补码的机器数形式是0.1011:

1.0001100000

2.[X]补=11010111

[Y]补=01100101[-Y]补=10011011

[x+y]补二[X]补+[丫]补=0,0111100,Z=0.V=0.OA

[x-y]补二[X]补H-Y]补二0,1110010,Z=0.V=LC=l

3.[x+y]补二0.0111010,Z=0.V二0.01

[x-y]Ib=1.0001110.Z=0,V=LC=0(过程略)

4.按原码一位乘做乘法计算[x•y]原=1,01101100.则x•y—0.01101100(过程略)

5.解:

[X]戸00,010;00.11010[Y],-00.011:

11.00010

1)对阶:

[Aj]#=[jx]^[jy]#=00,010-00.011=11.111

即△j—1,则X的尾数右移一位,阶码加1,则[X]'00.011:

00.01101

2)尾数求和

[sj*[Sy]戸00.01101+11.00010=11.01111

即[X+Y]•二00,Oil:

11.0111U

3)規格化

[X+Yh是规格化形式。

4)阶符为"00",不溢出。

则

X+Y=(-0.10001)X2°”

6•定点机中釆用单符号位判断补码加减运算是否溢出有两种方案。

(1)参加运算的两个操作数(减法时絨数需连同符号位在每位取反,末位加1)符号相同,结果的符号又与操作数的符号

不同,则为溢出。

(2)求和时最高位进位与次高位进位异或结果为1时,则为溢出。

第五章习题

一、选择题

1.存取周期是指0

A存储器的写入时问

B存俸器进行连续写操作允许的最短问隔时问

C存储器进行连续读或写操作所允许的最短问隔时问

D以上都不对

2.和辅存相比,主存的特点是。

A容量小,速度快,成本高

B容量小,速度快,成本低

C容量大,速度快,成本高

D容量大,速度慢,成本高

3.一个16K*32位的存储器•其地址线和数据线的总和是o

A48B46C36D35

4.一个512KB的存储器,其地址线利数据线的总籾是。

5.某计算机字长是16位,它的存储容量是64KB,按字編址.它的寻址国是

A61KB32KBC32KD16K

6.某一RAM芯片,其容量为512*8位,除电源和接地端外,该芯片引出线的最少数目是

A21B17C19D18

7•某一RM芯片,其容量为32K*8位,除电源和接地端外,该芯片引出线的最少数目是一

A25B40C23D24

8.若主存毎个存储单元为16位,则。

A其地址线为16根

B其地址线数与16无关

C其地址线数与16有关

D以上描述均错误

9.某存储器容量为32K*16位,则。

A地址线为16根,數据线为32根

B地址线为32根,数据线为16根

C地址线为15根,数据线为16根

D地址线为15根,数据线为32根

10・下列叙述中是正确的。

A主存可由RAM和ROM组成

B主存只能由ROH组成

C主存只能由R"组成

D以上描述均錯误

11.EPROH是指。

A只读存储器

B可编程的只读存储器

C可擦除可编程的只读存储器

D电可擦除可编程的只读存條器

12.下述说法中是正确的。

A半导体RAN信息可读可写,且断电后仍能保持记忆

B动态RAM是易失性RAM,而静态RAM中的存储信息是不易失的

C半导体R"是易失性RM,而帝态RAM只有在电源不棹电时,所存信息是不易失的

D动态RAM与挣态RAM中的存储信息趋是不易失的

13.主存和CPU之问増加高速缓冲存储器的目的是o

A解决CPU和主存之问的速度匹配问题

B扩大主存容量

C既扩大主存容量,又提高存取速度

D解决主存容量不足的问題

14.在程序的执行过程中,Cache与主存的地址映射是由。

A操作系统来管理的

B程序员调度的

C由硬件自动完成的

D以上均不正确

15.Cache的地址映像中,若主存中的任一块均可映射到Cache的任一块的位置上,称作。

A直搂映射B全相联映射C组相联映射D部分相联

16.下列器件中存取速度最快的是o

ACacheB主存C寄存器D硬盘

二、填空题

1.主存、快速缓冲存储器、通用寄存器、磁带都可用来存储信息,按存取时问由快至慢排列,其顺序是_A。

2._A_.—B_和—C—组成三级存储系统,分级的目的是D—o

3.半导体静态RAM依据A存储信息,半导体动态RAN依据—B存储信息。

4.动态RAM依据—A—的原理存储信息,因此一般在—B—时问必须刷新一次。

5.RAH的速度指标一般用—A—表示。

6.动态半导体存储器的刷新一般有—A_和_B_两种方式,之所以刷新是因为_C_。

7.半导体待态RAM进行读/写操作时,必须先接受_A_信号,再接受_B_和_C_信号。

8.欲组成一个32K*8位的存储器,当分别选用1K初位,16K*1位,2K*8位的三种不同规格的存储芯片时,各需—A_.

—B_和_C_片。

9.欲组成一个64K*16位的存储器,若选用32K*8位的存借芯片,共第—A_片:

若选用16KH位的存储芯片,则需

_B_片:

若选用1K判位的存储芯片共需_C_片。

10・主存储器容量通常以KB为单位,其中K=_A—o硬盘的容量通常以GB为单位,其中G=_B—。

11.主存储器为MB即等于—_・LKB,又可表示为B

12.当我们说16位徹机的主存储器容量是640KB时,表示主存储器有_A—字节存储空问,地址号从_B—到_C_(本題均要求写出十进制各位数值)

13.主存和Cache的地址映像方法很多,饬用的有—A—、—B—和—C—三种,在存储管理上常用的替换算法是—D—和—E—。

14.Cache的命中率是指—A,命中率与—B有关。

15.Cache是一种—A—存储器,用来解决CPU与主存之问—B—不匹配的问题。

现代的Cache可分为—C—和—D—两级,并将—E—和_F_分开设置。

16.计算机系统中常用到的存储器有:

(1)SRAM,

(2)DRAM,(3)Flash,(4)EPROM,(5)玫盘存储器,(6)软盘

存储器。

其中非易失的存储器有_A—;具有在线能力的有_B—;可以单宇节修改的有_C—;可以快速读出的存储器包括D。

17.如果Cache的容量为128块,在直接映像下,主存中第i块映像到缓存第—A—块。

18.在Cache—主存的地址映像中,—A—灵活性强,—B—成本最高。

19.在写操作时.对Cache与主存单元同时修改的方法称为—A—,若每次只暫时写入Cache.直到替换时才写入主存的方法称为—B—。

20.—个n路组相联映像的Cache中,共有M块数据。

当门二1时,该Cache变为—A映像:

当时,该Cache

成为—B映像。

21.层次化存储器结构设计的依据是_Ao

22.一个四路组相联的Cache共有64块,主存共有8192块,毎块32个字。

则主存地址中的主存字块标记为—A

位,组地址为—B_位,宇块地址为—C_位。

三、问答题

1.试比较RAN和ROM

2试比较静态RAM和动态RAM

3.存储器的主要功能是什么?

如何衡量存储器的性能?

为什么要把存储系统分成若干不同的层次?

主要有哪些层次?

4.什么是刷新?

刷新有几种方式?

简要说明之

5.存储芯片的地址译码有几种方式?

是分析它们各自的特点及应用场合。

6.简述主存的读/写过程

7.提高访存速度可采取哪些措施?

8.什么是快速缓冲存储器,它与主存有什么关系?

9.什么是“程序访问的局部性"?

存储系统中哪一级釆用了程序访问的局部性原理?

10•使用4K*8位的RAH芯片组成一个容量为8K*16位的存储弄,画出结构框图,并标明途号线的种类、方向和条数。

11.设CPU挂有16根地址线,8根数据线,并用111腿Q作为访存控制信号(低电平有效),用尬作为读/写控制信号(高电平为读,低电平为写)。

现有下列存储芯片:

1K*1位R",4K*8位RAM,2K*8位ROM以及74138亿马奇和各种门电路,如图4.14所示。

画出CPU与存储芯片的连接图,要求:

(1)主存地址空间分配:

8000H-87ITH徹系统程序区:

8800H-8BFFH为用户程序区。

(2)合理选用上述存储芯片,说明各选几片。

(3)详细画出存储芯片的片选逻辑。

12.在32题给出的条件下,画出CPU与存储芯片的连接图,要求:

(1)主存地址空问分配:

A000-A7FFH徹系统程序区;A800H-AFFH为用户程序区。

(2)合理选用上述存储芯片,说明各选几片,并写出每片存储芯片的二进制地址围。

(3)详细画出存储芯片的片选逻辑。

13某计算机的主存容量为256K字,cache的容量为2K字,毎个字块为16字,访存地址为字地址,问:

(1)该cache可以容纳多少个块?

(2)主存的地址有多少位?

(3)在二路组相联映像方式下.设计主存的地址格式,画出主存地址格式图。

M.某计算机的cache的容量为2K宇,毎块为16字。

问:

O该cache可以容纳多少个块?

❷若主存容量是256K字,则有多少个块?

❸主存的地址有多少位?

O在直接地址映像方式下,主存中的•第129块映像到cache中的哪一块?

O画出主存地址格式图。

参考答案

一、选择题

1.C2.A3.B4.C5.C6.C7.A8.B

9.C10.All.C12.C13.A14.C15.B16.C

二、填空题

1.A.il用寄存器、快速缓冲存储器、主存、磁盘.磁带

2.A.CacheB•主存C.辎存D.提高访问速度、扩大存储容量

3.A.触发器原理B.电容存储电荷原理

4.A.电容存储电荷B.2ms

5.A.存取周期

6.A•集中刷新B.分散刷新C.存储电荷的电容放电

7.A•地址B.片选C.读/写

8.A.64

B.16

C.16

9.A.4

B.64

C.256

10.A.

1024

B.2他

11.A.

1021

B.2”B

12.A.

655360

B.0<

C.655359

13.A.直褛映像B.全相联映像C;•组相联映像

D.先进先出算法(FIFO)E.近期最少使用算法(LRU)

14.A.CPU要访问的信息已在Cache中的比率

B.Cache的块长和容量

15.

A•高速缓冲B.速度C.片载CacheD片外CacheE.指令CacheI;•数Cache

17.A.imod128

18.

B.全相联映像

B.写回法

B.全相联

A•全相联映像

19.A•写直达法

20・A•直接

21.A•程序访问的局部性

22.A.9B.4C.5

三、问答题

1.RAM是随机存取存储弄,在程序的执行过程中既可读出又可写人ROM是只读存储器,在程序执行过程中只能读出信息,不能写人信息。

2.棘态RAM和动态RAM都属随机存储器,即在程序的执行过程中既可读出又可写人信息。

但静态RAM靠触发器原理存储信息只要电遽不掉电,信息就不丢失;动态RAM*电容存储电荷原理存储信息,即使电源不禅电,自于电容要放电,信息也会丢失,故需再生。

3•存储器的主要功能是存放程序或各类数据。

通常用存储容量、存取周期以及存倫器的带宽(毎秒从存储器读出或写入二进制代码的位数)三项指标来反映存储器的性能。

为了扩大存储器容量和提高访存速度,将存储系统分成若于不同层次,有Cache一主存层次和主存一舗存层次。

前考为使存借器与CPU速度匹史,在CPU和主存之问増设Cache离速缓冲存储器,其容量比主存小,速度比主存快,用来存放CPU最近期要用的信息,CPU可直接从Cache中取到信息,从而提高了访存速度。

后者为扩大存储器容量,把主存和辅存统一成一个整体,从整体上看,速度取决于主存,容量取决于辅存,称为虛存°CPl;只与主存交换信息,但程序员可用指令地址码进行编程,其位数与虚存的地址空问对应。

4•动态RAM#电容存储电荷原理存储信息,电容上的电荷要放电,信息即丢失。

为了维持所存信息,需在一定时问(2ms),将所存信息读出再重新写人(恢复),这一过程称为刷新,刷新是一行一行进行的,由UPU自动完成。

刷新通常可分集中刷新和分散刷新两种。

巣中刷新即在2ms时问,集中一段时问对存储芯片的毎行刷新一遍,在这段时问里不能对存储器进行访问,即所谓死时问。

分散刷新是将存储系统周期分为两半,前半段时问用来进行读/写操作,后半段时问用来进行刷新操作,显然整个系统的速度降低了,但分散刷新没有存储器的死时问。

还可瘠这两种刷新结合起来,即异步刷新,这种刷新可在2ms时问对存储芯片的每一行刷新一遍,两行之问的刷新问隔时问为2(ns/芯片的行数。