数字逻辑电路实验报告.docx

《数字逻辑电路实验报告.docx》由会员分享,可在线阅读,更多相关《数字逻辑电路实验报告.docx(15页珍藏版)》请在冰豆网上搜索。

数字逻辑电路实验报告

数字逻辑电路实验报告

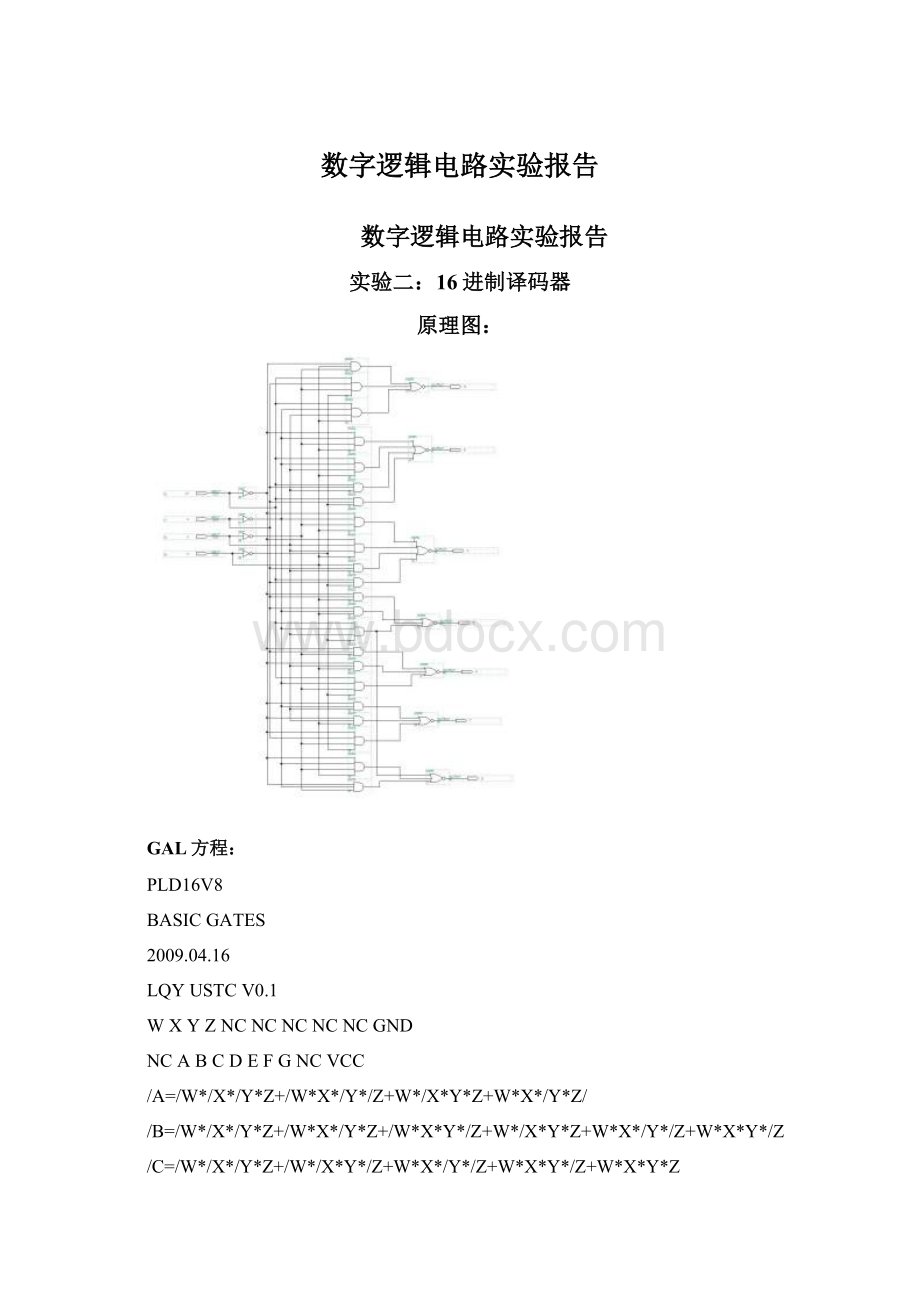

实验二:

16进制译码器

原理图:

GAL方程:

PLD16V8

BASICGATES

2009.04.16

LQYUSTCV0.1

WXYZNCNCNCNCNCGND

NCABCDEFGNCVCC

/A=/W*/X*/Y*Z+/W*X*/Y*/Z+W*/X*Y*Z+W*X*/Y*Z/

/B=/W*/X*/Y*Z+/W*X*/Y*Z+/W*X*Y*/Z+W*/X*Y*Z+W*X*/Y*/Z+W*X*Y*/Z

/C=/W*/X*/Y*Z+/W*/X*Y*/Z+W*X*/Y*/Z+W*X*Y*/Z+W*X*Y*Z

/D=/W*/X*/Y*Z+/W*X*/Y*/Z+/W*X*Y*Z+W*/X*Y*/Z+W*X*Y*Z

/E=/W*/X*Y*Z+/W*X*/Y*/Z+/W*X*/Y*Z+/W*X*Y*Z+W*/X*/Y*Z

/F=/W*/X*Y*/Z+/W*/X*Y*Z+/W*X*Y*Z+W*X*/Y*Z

/G=/W*/X*/Y*Z+/W*X*Y*Z+W*X*/Y*/Z+/W*/X*/Y*/Z

DESCRIPTION

注释:

实验中使用的是共阳极数码管,设计的时候还没有化简

VHDL代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYcode16IS

PORT(w,x,y,z:

INSTD_LOGIC;

A,b,c,d,e,f,g:

OUTSTD_LOGIC

);

ENDcode16;

ARCHITECTUREWORKOFcode16IS

BEGIN

A<=(NOTWANDNOTXANDNOTYANDZ)OR(NOTWANDXANDNOTYANDNOTZ)OR(WANDNOTXANDYANDZ)OR(WANDXANDNOTYANDNOTZ);

B<=(NOTWANDNOTXANDNOTYANDZ)OR(NOTWANDXANDNOTYANDZ)OR(NOTWANDXANDYANDNOTZ)OR(WANDNOTXANDYANDZ)OR(WANDXANDNOTYANDNOTZ)OR(WANDXANDYANDNOTZ);

C<=(NOTWANDNOTXANDNOTYANDZ)OR(NOTWANDNOTXANDYANDNOTZ)OR(WANDXANDNOTYANDNOTZ)OR(WANDXANDYANDNOTZ)OR(WANDXANDYANDZ);

D<=(NOTWANDNOTXANDNOTYANDZ)OR(NOTWANDXANDNOTYANDNOTZ)OR(NOTWANDXANDYANDZ)OR(WANDNOTXANDYANDNOTZ)OR(WANDXANDYANDZ);

E<=(NOTWANDNOTXANDYANDZ)OR(NOTWANDXANDNOTYANDNOTZ)OR(NOTWANDXANDNOTYANDZ)OR(NOTWANDXANDYANDZ)OR(WANDNOTXANDNOTYANDZ);

F<=(NOTWANDNOTXANDYANDNOTZ)OR(NOTWANDNOTXANDYANDZ)OR(NOTWANDXANDYANDZ)OR(WANDXANDNOTYANDZ);

NOTG<=(NOTWANDNOTXANDNOTYANDZ)OR(NOTWANDXANDYANDZ)OR(WANDXANDNOTYANDNOTZ)OR(NOTWANDNOTXANDNOTYANDNOTZ);

ENDWORK;

实验三:

海明校验电路

原理图:

做实验时,造错在总线上造错,导致读和写没有很好体现出来。

GAL方程:

PLD01V0

HAMMING

2009.04.16

LQYUSTCV0.1

ABCDEAEBECEDNCGND

NCS1S2S3R1R2R3R4NCVCC

IA=A$EA

IB=B$EB

IC=C$EC

ID=D$ED

K1=A$B$D

K2=A$C$D

K3=B$C$D

S1=A$B$D$K1

S2=A$C$D$K2

S3=B$C$D$K3

E1=S1*S2*S3

E2=S1*S2*/S3

E3=S1*/S2*/S3

E4=/S1*S2*S3

R1=A$E1

R2=B$E2

R3=C$E3

R4=D$E4

DESCRIPTION

VHDL代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYhammIS

PORT(i1,i2,i3,i4,e1,e2,e3,e4:

INSTD_LOGIC;

r1,r2,r3,k1,k2,k3,k4:

OUTSTD_LOGIC);

ENDhamm;

ARCHITECTUREhammingOFhammIS

SIGNALs1,s2,s3,b1,b2,b3,b4,c1,c2,c3,c4,d1,d2,d3,d4:

STD_LOGIC;

BEGIN

b1<=i1XORe1;

b2<=i2XORe2;

b3<=i3XORe3;

b4<=i4XORe4;

s1<=i4XORi2XORi1;

s2<=i4XORi3XORi1;

s3<=i4XORi3XORi2;

c1<=b4XORb2XORb1XORs1;

c2<=b4XORb3XORb1XORs2;

c3<=b4XORb3XORb2XORs3;

d1<=c1ANDc2AND(NOTc3)AND(NOTc4);

d2<=c1AND(NOTc2)AND(NOTc3)ANDc4;

d3<=(NOTc1)ANDc2ANDc3ANDc4;

d4<=c1ANDc2ANDc3ANDc4;

r1<=c1;

r2<=c2;

r3<=c3;

k1<=d1XORc1;

k2<=d2XORc2;

k3<=d3XORc3;

k4<=d4XORc4;

ENDhamming;

实验四:

时序脉冲分频电路

原理图:

二分频电路

四分频电路

五分频电路

三周期电路

GAL方程:

VHDL代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYexp5txIS

PORT(clk:

INSTD_LOGIC;

CP1,CP2,CP3,CP4,CP5,CP6:

OUTSTD_LOGIC;

Q3,Q4,Q4b,Q5,Q6,Q7,Q8:

BUFFERSTD_LOGIC);

ENDexp5tx;

ARCHITECTUREDISTRIBUTEROFexp5txIS

BEGIN

PROCESS(clk,Q3,Q5)

VARIABLEcount_5:

STD_LOGIC_VECTOR(2DOWNTO0);

VARIABLEcount_2:

STD_LOGIC;

VARIABLEcount_4:

STD_LOGIC_VECTOR(1DOWNTO0);

VARIABLEcount_3:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

IF(clk'EVENTANDclk='1')THEN

IF(count_5="000")THEN

count_5="001";Q3<='1';

ELSIF(count_5="001")THEN

count_5:

="010";Q3<='0';

ELSIF(count_5="010")THEN

count_5:

="011";Q3<='0';

ELSIF(count_5="011")THEN

count_5:

="100";Q3<='0';

ELSIF(count_5="100")THEN

count_5:

="000";Q3<='0';

ENDIF;

ENDIF;

IF(Q3'EVENTANDQ3='1')THEN

IF(count_2='0')THEN

count_2:

='1';Q4<='1';Q4b<='0';

ELSIF(count_2='1')THEN

count_2:

='0';Q4<='0';Q4b<='1';

ENDIF;

ENDIF;

IF(Q3'EVENTANDQ3='1')THEN

IF(count_4="00")THEN

count_4:

="01";Q5<='1';

ELSIF(count_4="01")THEN

count_4:

="10";Q5<='1';

ELSIF(count_4="10")THEN

count_4:

="11";Q5<='0';

ELSIF(count_4="11")THEN

count_4:

="00";Q5<='0';

ENDIF;

ENDIF;

IF(Q5'EVENTANDQ5='1')THEN

IF(count_3="00")THEN

count_3:

="01";Q6<='1';Q7<='0';Q8<='0';

ELSIF(count_3="01")THEN

count_3:

="10";Q6<='0';Q7<='1';Q8<='0';

ELSIF(count_3="10")THEN

count_3:

="00";Q6<='0';Q7<='0';Q8<='1';

ENDIF;

ENDIF;

ENDPROCESS;

CP1<=Q4bANDQ5ANDQ6;

CP2<=Q4bANDNOTQ5ANDQ6;

CP3<=Q4bANDQ5ANDQ7;

CP4<=Q4bANDNOTQ5ANDQ7;

CP5<=Q4bANDQ5ANDQ8;

CP6<=Q4bANDNOTQ5ANDQ8;

ENDDISTRIBUTER;

实验五:

串并转换电路

原理图:

控制逻辑

十六进制计数器

GAL方程:

VHDL代码:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYspIS

PORT(clk,rd:

INSTD_LOGIC;

s7,s6,s5,s4,s3,s2,s1,s0:

OUTSTD_LOGIC

);

ENDsp;

ARCHITECTUREWORKOFspIS

SIGNALclr,cclk,c2,c16,d7,d6,d5,d4,d3,d2,d1,d0,st:

STD_LOGIC;

BEGIN

PROCESS(clk)

VARIABLEcount_4:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

IF(clk'EVENTANDclk='1')THEN

IF(count_4="00")THEN

count_4:

="01";c2<='1';

ELSIF(count_4="01")THEN

count_4:

="11";c2<='0';

ELSIF(count_4="11")THEN

count_4:

="10";c2<='0';

ELSIF(count_4="10")THEN

count_4:

="00";c2<='0';

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(c2,rd)

VARIABLEcount_2:

STD_LOGIC;

BEGIN

IF(c2'EVENTANDc2='1')THEN

d0<=rd;

d1<=d0;

d2<=d1;

d3<=d2;

d4<=d3;

d5<=d4;

d6<=d5;

d7<=d6;

ENDIF;

ENDPROCESS;

PROCESS(clk,d7,d6,d5,d4,d3,d2,d1,d0)

BEGIN

IF(clk'EVENTANDclk='1')THEN

IF(d7='0'andd6='1'andd5='1'andd4='1'andd3='1'andd2='1'andd1='1'andd0='0')THEN

st<='0';

ELSIF(d7='1'andd6='0'andd5='0'andd4='0'andd3='0'andd2='0'andd1='0'andd0='1')THEN

st<='1';

ENDIF;

ENDIF;

cclk<=stANDclk;

IF(d7='0'andd6='1'andd5='1'andd4='1'andd3='1'andd2='1'andd1='1'andd0='0')THEN

clr<='1';

ELSIF(d7='1'andd6='0'andd5='0'andd4='0'andd3='0'andd2='0'andd1='0'andd0='1')THEN

clr<='1';

ELSE

clr<='0';

ENDIF;

ENDPROCESS;

PROCESS

VARIABLEcount_4:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

WAITONcclkUNTIL(cclk'EVENTANDcclk='1');

IF(count_4="0000")THEN

count_4:

="0001";c16<='0';

ELSIF(count_4="0001")THEN

count_4:

="0010";c16<='0';

ELSIF(count_4="0010")THEN

count_4:

="0011";c16<='0';

ELSIF(count_4="0011")THEN

count_4:

="0100";c16<='0';

ELSIF(count_4="0100")THEN

count_4:

="0101";c16<='0';

ELSIF(count_4="0101")THEN

count_4:

="0110";c16<='0';

ELSIF(count_4="0110")THEN

count_4:

="0111";c16<='0';

ELSIF(count_4="0111")THEN

count_4:

="1000";c16<='0';

ELSIF(count_4="1000")THEN

count_4:

="1001";c16<='0';

ELSIF(count_4="1001")THEN

count_4:

="1010";c16<='0';

ELSIF(count_4="1010")THEN

count_4:

="1011";c16<='0';

ELSIF(count_4="1011")THEN

count_4:

="1100";c16<='0';

ELSIF(count_4="1100")THEN

count_4:

="1101";c16<='0';

ELSIF(count_4="1101")THEN

count_4:

="1110";c16<='0';

ELSIF(count_4="1110")THEN

count_4:

="1111";c16<='0';

ELSIF(count_4="1111")THEN

count_4:

="0000";c16<='1';

ENDIF;

ENDPROCESS;

PROCESS(c16,st,clr)

BEGIN

IF(c16='0'ORst='0'ORclr='1')THEN

s0<='Z';

s1<='Z';

s2<='Z';

s3<='Z';

s4<='Z';

s5<='Z';

s6<='Z';

s7<='Z';

ELSE

s0<=d0;

s1<=d1;

s2<=d2;

s3<=d3;

s4<=d4;

s5<=d5;

s6<=d6;

s7<=d7;

ENDIF;

ENDPROCESS;

ENDWORK;