用verilog语言编写交通灯程序.docx

《用verilog语言编写交通灯程序.docx》由会员分享,可在线阅读,更多相关《用verilog语言编写交通灯程序.docx(7页珍藏版)》请在冰豆网上搜索。

用verilog语言编写交通灯程序

交通灯

一、实验目的

写一个交通灯,要求:

1有东西南北四个方向,两组交通灯轮流交替变换,其中,红灯时间为30个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。

最后用modelsim软件进行仿真。

2要求设计是一个可综合设计。

二、实验原理

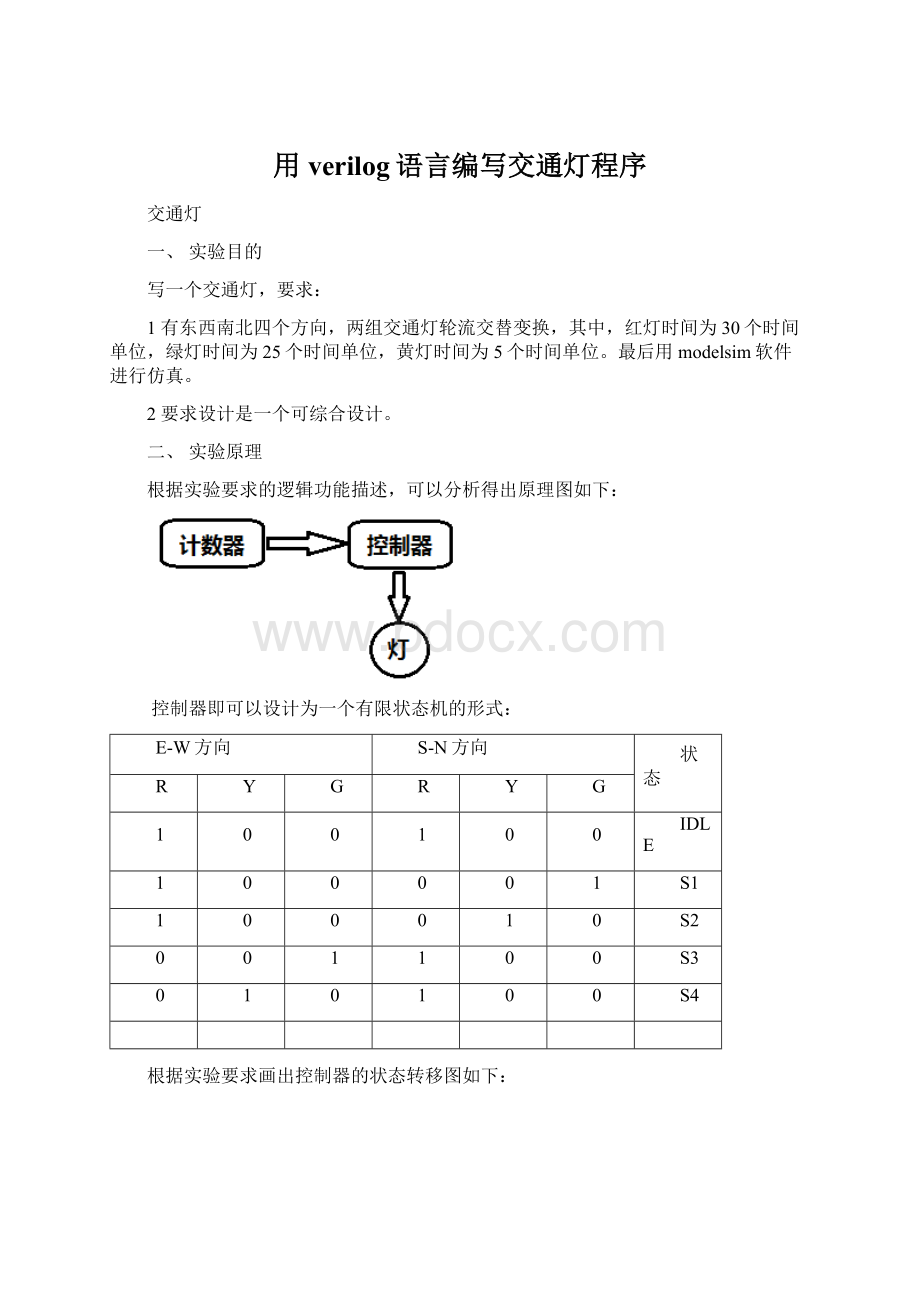

根据实验要求的逻辑功能描述,可以分析得出原理图如下:

控制器即可以设计为一个有限状态机的形式:

E-W方向

S-N方向

状态

R

Y

G

R

Y

G

1

0

0

1

0

0

IDLE

1

0

0

0

0

1

S1

1

0

0

0

1

0

S2

0

0

1

1

0

0

S3

0

1

0

1

0

0

S4

根据实验要求画出控制器的状态转移图如下:

三、代码

1、源代码

(1)控制器模块

moduletraffic_lights(clk,rst,count,ew,sn);

inputclk,rst;

input[5:

0]count;

output[2:

0]ew,sn;

reg[2:

0]ew,sn;

reg[3:

0]state;

parameterIdle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100;

always@(posedgeclk)

if(!

rst)

begin

state<=Idle;

end

else

casex(state)

Idle:

if(rst)

begin

state<=s1;

end

s1:

if(count=='d25)

begin

state<=s2;

end

s2:

if(count=='d30)

begin

state<=s3;

end

s3:

if(count=='d55)

begin

state<=s4;

end

s4:

if(count=='d60)

begin

state<=s1;

end

endcase

always@(posedgeclk)

begin

if(!

rst)

begin

ew<=3'b100;

sn<=3'b100;

end

else

casex(state)

Idle:

if(rst)

begin

ew<=3'b100;

sn<=3'b001;

end

s1:

if(count=='d25)

begin

ew<=3'b100;

sn<=3'b010;

end

s2:

if(count=='d30)

begin

ew<=3'b001;

sn<=3'b100;

end

s3:

if(count=='d55)

begin

ew<=3'b010;

sn<=3'b100;

end

s4:

if(count=='d60)

begin

ew<=3'b100;

sn<=3'b001;

end

default:

state<=Idle;

endcase

end

endmodule

(2)计数器模块

modulecounter(en,clk,rst,out);

output[5:

0]out;

inputen,clk,rst;

reg[5:

0]out;

always@(posedgeclkornegedgerst)

begin

if(!

rst)

out<='d0;

elseif(!

en&&out<'d60)

out<=out+1;

else

out<='d1;

end

endmodule

(3)将控制器与计数器进行连接

moduletraffic_lights_top(out,clk,rst,en,ew,sn);

inputclk,rst,en;

output[2:

0]ew,sn;

output[5:

0]out;

wire[5:

0]out;

traffic_lightsu1(

.clk(clk),

.rst(rst),

.count(out),

.ew(ew),

.sn(sn)

);

counteru2(

.en(en),

.clk(clk),

.rst(rst),

.out(out)

);

endmodule

2、激励

`timescale1ns/100ps

moduletraffic_lights_tb;

regclk,rst,en;

wire[2:

0]ew,sn;

wire[5:

0]out;

traffic_lights_topm(

.clk(clk),

.rst(rst),

.en(en),

.ew(ew),

.sn(sn),

.out(out)

);

always

#5clk=~clk;

initial

en<=1;

initial

begin

clk<=1;

en<=0;

rst<=0;

#5rst<=1;

end

endmodule

四、仿真波形

(图一)

(图二)

五、波形说明

波形图中,从上至下依次为:

时钟信号clk、复位信号rst、计数器使能端en、东西方向上灯的状态ew、南北方向上灯的状态sn、计数器的输出out。

该程序实现的功能是在一个十字路口的交通灯的轮流交替变换:

状态

方向

灯的状态

0——25

25——30

30——55

55——60

东西方向ew

红

红

绿

黄

南北方向sn

绿

黄

红

红

图一可以完整的看到60个时间单位内两个方向上灯交替的状况

图二可以清楚的看到在时间从0——30过程中灯的跳变时间和结果。

五、实验过程中遇到的问题及解决方法

1、在实验过程中得到的波形图跟我设计的时间间隔不一致,仔细检查过后发现是因为控制器和计数器没有很好的连接在一起,导致灯的跳变跟计数器的控制脱离了,修改之后得到时间间隔比例跟设计一致的波形。

2、在检查波形的过程中发现计数器实现的不是模60,而是模64,将计数器程序中的选择条件从if(!

en)改为if(!

en&&out<’d60)之后得到了自己想要的计数器。

六、实验心得

刚开始,程序调试过程中始终都有些莫名其妙的错误,自己只能凭着自己的理解和单纯靠一些感觉去修改。

有时候越改错误越多,到后来程序显示没有错误了,但是仿真却无法执行,一长串的警告看的我有点崩溃。

静下心来后从头开始分析每一句的程序,最后发现其实只是一个很小的失误。