QuartusII操作入门全加器设计.doc

《QuartusII操作入门全加器设计.doc》由会员分享,可在线阅读,更多相关《QuartusII操作入门全加器设计.doc(5页珍藏版)》请在冰豆网上搜索。

实验1QuartusII操作入门——全加器设计

友情提示:

实验做完后请保存到您的U盘中,以便后续实验要用。

另外,请保存实验报告

中要用到的屏幕截图。

1.1实验目的

熟悉使用QuartusII的基本操作方法,利用原理图输入设计方法设计1位全加器。

1.2实验内容

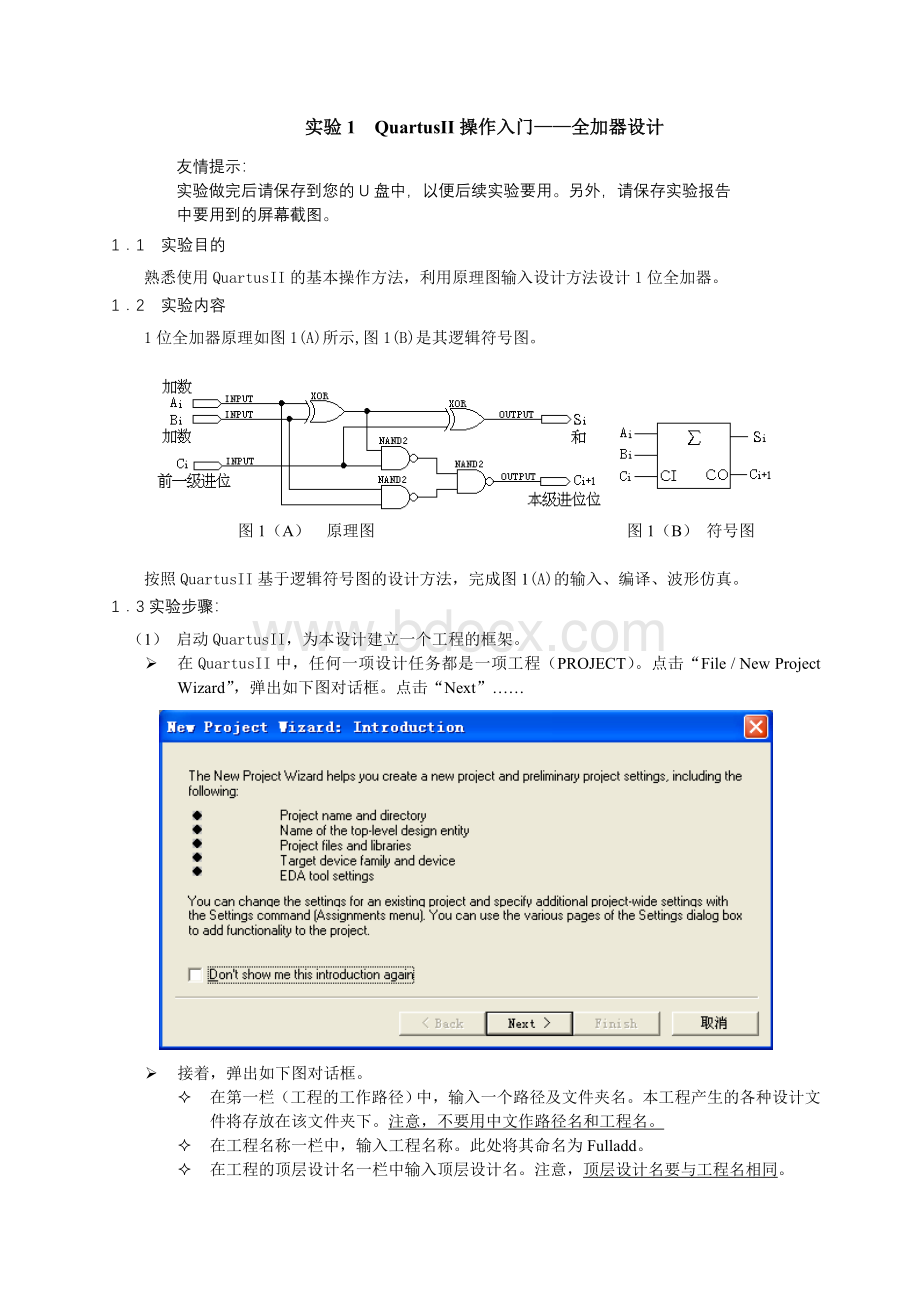

1位全加器原理如图1(A)所示,图1(B)是其逻辑符号图。

图1(A)原理图图1(B)符号图

按照QuartusII基于逻辑符号图的设计方法,完成图1(A)的输入、编译、波形仿真。

1.3实验步骤:

(1)启动QuartusII,为本设计建立一个工程的框架。

Ø在QuartusII中,任何一项设计任务都是一项工程(PROJECT)。

点击“File/NewProjectWizard”,弹出如下图对话框。

点击“Next”……

Ø接着,弹出如下图对话框。

²在第一栏(工程的工作路径)中,输入一个路径及文件夹名。

本工程产生的各种设计文件将存放在该文件夹下。

注意,不要用中文作路径名和工程名。

²在工程名称一栏中,输入工程名称。

此处将其命名为Fulladd。

²在工程的顶层设计名一栏中输入顶层设计名。

注意,顶层设计名要与工程名相同。

Ø点击“Finish”,完成建立工程的框架。

如果你输入的工作路径不存在,将弹出对话框,询问是否创建此工作路径。

点击“是”即可。

(2)在工程中加入顶层设计文件。

一个工程必须有一个顶层设计,在顶层设计中可以调用底层设计,从而形成一种逐层调用的层次结构。

点击“File/New”,弹出对话框。

选择“BlockDiagram/SchematicFile”,点击“OK”,于是新建了一个图形文件,其临时名称为Block1.bdf。

点击“File/Saveas”,将其保存为“Fulladd.bdf”,如下图所示。

“Fulladd.bdf”就是顶层设计文件。

(3)在“Fulladd.bdf”中绘制逻辑原理图。

Ø放置元件

以放置一个异或门为例,双击编辑区空白处,弹出如下对话框,在“Name”栏输入xor,点击“OK”。

Ø连接导线:

直接拖动鼠标即可将需要连接的端点连接起来。

按图1(A)原理图完成编辑,结果如下图。

将其存盘。

(4)编译工程。

点击对工程进行编译的快捷键“”,开始对工程进行编译。

如果有错,则应根据错误报告的提示改正错误,再编译,直到无错。

(5)仿真

Ø建立仿真需要的波形文件。

选择菜单“FILE/NEW”,弹出如下对话框。

按图选择,

并点击“OK”。

结果打开波形编辑窗。

它对应于波形文件,将其存盘为“Fulladd.vwf”。

注意,仿真波形文件的主名必须与工程名相同。

Ø输入信号结点。

双击波形编辑区中的“Name”栏下方的空白区,弹出对话框,再点击“NodeFoild…”,又弹出如下对话框,按图示操作。

点击“OK”,结果波形编辑窗中调入了全加器的所有节点信号,如下图。

Ø设置波形参量

²选“Edit/Endtime”,设置仿真时间总长度为1us;

²选“Edit/Gridsize”,设置时间周期为50ns。

(两条竖线站之间的时间)

Ø单击View→FitinWindows,以便在波形编辑窗观察全部仿真时间段。

再按下图编辑Ai、Bi和C的电平值。

(图中,8种输入值有)

编辑方法:

要设定某输入在某时段的电平值,在此时段上压住鼠标拖动,选中此时段;再 点击工具栏中的“1”或“0”按钮即可。

将编辑好的波形文件存盘。

Ø运行仿真器

单击快捷键“”,即进入仿真运行。

结果如下图。

Ø观察分析波形

检查全加器的时序波形是否正确。

图中的竖标线是测试参考线,上方标出的350.0ns是此线所在的时间位置,此时3个输入分别为Ai=1、Bi=1、Ci=0,两个输出分别为Si=1、Ci1=0,这与全加器的逻辑运算关系相符。

对所有时段进行检查,看是否与全加器的逻辑运算关系相符。

如全部相符,就说明加法运算结果正确。

1.4实验报告

实验报告应包含如下内容:

1、实验名称。

(占1行)

2、实验者,实验地点、时间。

(占1行)

3、实验用到的硬件(计算机:

PC,操作系统:

WindowsXP)。

主要软件:

QuartusⅡ7.0

4、实验目的

5、设计与仿真过程。

6、实验结果及分析。

7、列举在实验中遇到的问题及解决经过。