VHDL语言实例教学内容.docx

《VHDL语言实例教学内容.docx》由会员分享,可在线阅读,更多相关《VHDL语言实例教学内容.docx(10页珍藏版)》请在冰豆网上搜索。

VHDL语言实例教学内容

VHDL语言实例

例1:

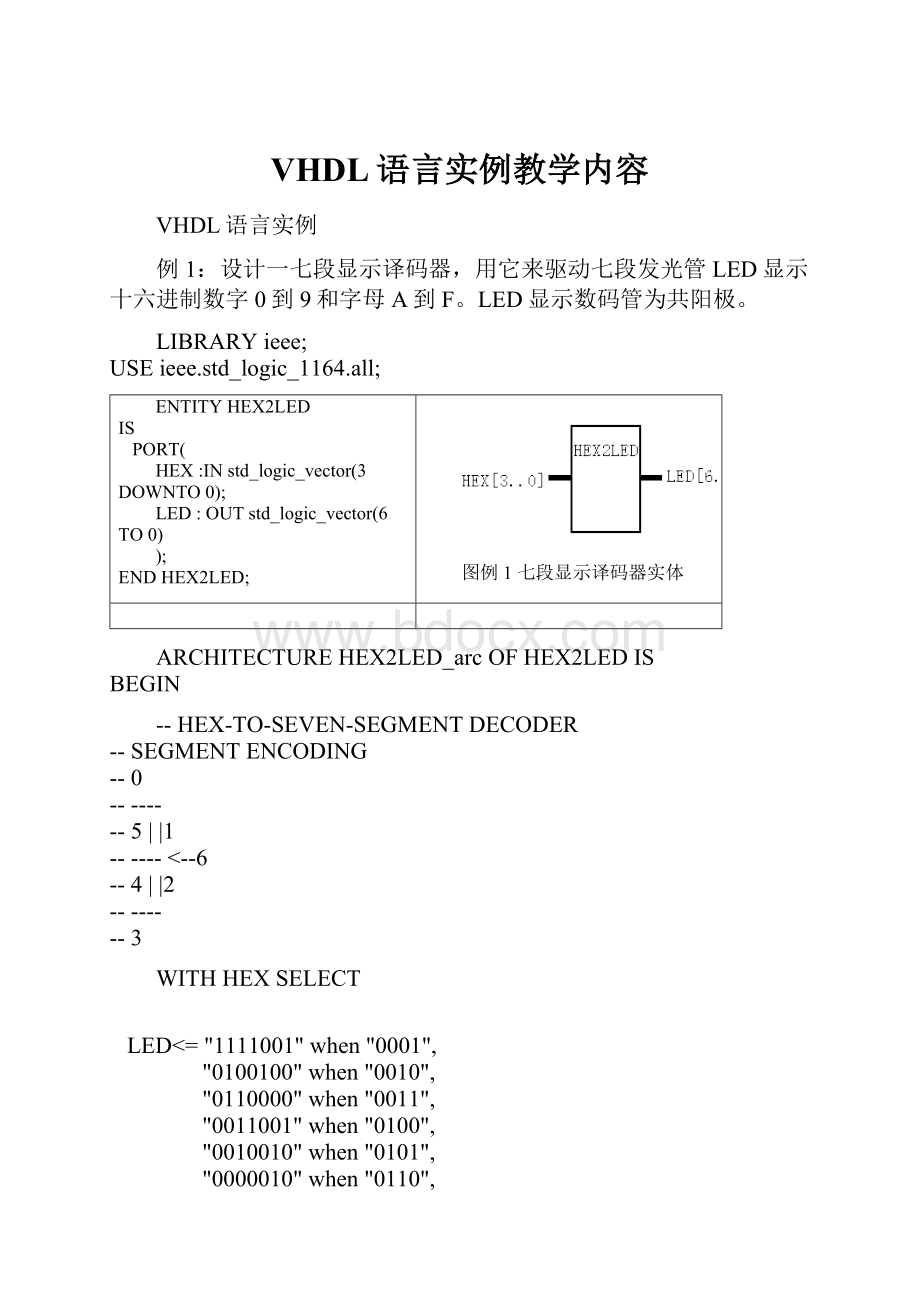

设计一七段显示译码器,用它来驱动七段发光管LED显示十六进制数字0到9和字母A到F。

LED显示数码管为共阳极。

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYHEX2LEDIS

PORT(

HEX:

INstd_logic_vector(3DOWNTO0);

LED:

OUTstd_logic_vector(6TO0)

);

ENDHEX2LED;

图例1七段显示译码器实体

ARCHITECTUREHEX2LED_arcOFHEX2LEDIS

BEGIN

--HEX-TO-SEVEN-SEGMENTDECODER

--SEGMENTENCODING

--0

------

--5||1

------<--6

--4||2

------

--3

WITHHEXSELECT

LED<="1111001"when"0001",

"0100100"when"0010",

"0110000"when"0011",

"0011001"when"0100",

"0010010"when"0101",

"0000010"when"0110",

"1111000"when"0111",

"0000000"when"1000",

"0010000"when"1001",

"0001000"when"1010",

"0000011"when"1011",

"1000110"when"1100",

"0100001"when"1101",

"0000110"when"1110",

"0001110"when"1111",

"1000000"whenothers;

ENDHEX2LED_arc;

例2:

设计一个八选一数据选择器

1)s是通道选择信号, d0,d1,d2,d3,d4,d5,d6,d7数据输入 out1是数据输出

ENTITYselsIS

PORT(d0,d1,d2,d3,d4,d5,d6,d7:

INBIT;

s:

INTEGERRANGE0TO7;

out1:

OUTBIT);

ENDsels;

图例2(a) 八选一数据选择器实体

ARCHITECTUREsels_arcOFselsIS

BEGIN

WITHsSELECT

out1<=d0WHEN0,

d1WHEN1,

d2WHEN2,

d3WHEN3,

d4WHEN4,

d5WHEN5,

d6WHEN6,

d7WHEN7;

ENDsels_arc;

2)A,B,C是通道选择信号, I0,I1,I2,I3,I4,I5,I6,I7数据输入 Q是数据输出

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYmux8IS

PORT(I0,I1,I2,I3,I4,I5,I6,I7,A,B,C:

INstd_logic;

Q:

OUTstd_logic);

ENDmux8;

图例2(b) 八选一数据选择器实体

ARCHITECTUREmux8_arcOFmux8IS

SIGNALsel:

INTEGER;

BEGIN

Q<=I0AFTER10nsWHENsel=0ELSE

I1AFTER10nsWHENsel=1ELSE

I2AFTER10nsWHENsel=2ELSE

I3AFTER10nsWHENsel=3ELSE

I4AFTER10nsWHENsel=4ELSE

I5AFTER10nsWHENsel=5ELSE

I6AFTER10nsWHENsel=6ELSE

I7AFTER10ns;

sel<=0WHENA=‘0’ANDB=‘0’ANDC=‘0’ELSE

1WHENA=‘1’ANDB=‘0’ANDC=‘0’ELSE

2WHENA=‘0’ANDB=‘1’ANDC=‘0’ELSE

3WHENA=‘1’ANDB=‘1’ANDC=‘0’ELSE

4WHENA=‘0’ANDB=‘0’ANDC=‘1’ELSE

5WHENA=‘1’ANDB=‘0’ANDC=‘1’ELSE

6WHENA=‘0’ANDB=‘0’ANDC=‘1’ELSE

7;

ENDmux8_arc;

例3:

设计一D触发器

d是输入端,clk是时钟信号控制端,q是触发器的输出端。

其程序如下:

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYregIS

PORT(d,clk:

INBIT;

q:

OUTBIT);

ENDreg;

图例3D触发器实体

ARCHITECTUREreg_arcOFregIS

BEGIN

PROCESS

BEGIN

WAITUNTILclk=‘1’;

q<=d;

ENDPROCESS;

PROCESS

ENDreg_arc;

例4:

设计一基本RS触发器

r、s为触发器的输入信号,q、not_q为触发器的输出信号。

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYRSFFIS

PORT(r,s:

INBIT;

q,not_q:

OUTBIT);

ENDRSFF;

图例4基本RS触发器实体

ARCHITECTURERSFF_arcOFRSFFIS

BEGIN

PROCESS(r,s)

VARIABLElast_state:

BIT:

=‘0’;

BEGIN

ASSERTNOT(r=‘1’ANDs=‘1’)

REPORT“BothrANDsequalto‘1’”

SEVERITYerror;

IFr=‘0’ANDs=‘0’THEN

last_state:

=last_state;

ELSIFr=‘1’ANDs=‘0’THEN

last_state:

=‘0’;

ELSE--r=‘0’ANDs=‘1’

last_state:

=‘1’;

ENDIF;

q<=last_stateAFTER10ns;

not_q<=NOT(last_state)AFTER20ns;

ENDPROCESS;

ENDRSFF_arc;

当r和s同时等于1时,触发器处于不定状态。

程序设计中设置了断言语句是为了判断r和s都等于1时,输出终端将显示报告“BothrANDsequalto‘1’”,同时终止模拟过程,并显示错误的严重error,以便设计者调试和修正模块程序。

从IF到ENDIF是条件语句,用到了可选项ELSIF和ELSE来判别RS触发器的其它三种情况。

IF语句后面是一赋值语句,将IF语句中赋值的中间变量lsat_state经10ns后送到q端。

图8-12是RS触发器的逻辑电路图。

例5:

设计一个带有异步清零、同步置数、使能控制的四位二进制计数器

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYCOUNT2IS

PORT(A:

ININTEGERRANGE0TO3;

CLK:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

EN:

INSTD_LOGIC;

LD:

INSTD_LOGIC;

Cout:

OUTINTEGERRANGE0TO3

);

ENDCOUNT2;

图例5 四位二进制计数器实体

ARCHITECTURECOUNT2_arcOFCOUNT2IS

SIGNAL SIG:

INTEGERRANGE0TO3;

BEGIN

PROCESS(CLK,CLR)

BEGIN

IFCLR='0'THEN

SIG<=0;

ELSIF(CLK'EVENTANDCLK='1')THEN

IFLD='1'THEN

SIG<=A;

ELSE

IFEN='1'THEN

SIG<=SIG+1;

ELSE

SIG<=SIG;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

Cout<=SIG;

ENDCOUNT2_arc

例6:

设计一个存储容量为28×8的RAM。

CS为RAM的片选信号,WR为RAM的写信号,RD为RAM读信号,ADR:

八位地址信号,Din:

八位数据输入线,Dout为八位数据输出线。

libraryIEEE;

useIEEE.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityRAMis

port(WR:

inSTD_LOGIC;

RD:

inSTD_LOGIC;

ADR:

inSTD_LOGIC_VECTOR(7downto0);

CS:

inSTD_LOGIC;

Din:

inSTD_LOGIC_VECTOR(7downto0);

Dout:

outSTD_LOGIC_VECTOR(7downto0)

);

endRAM;

图例6 RAM实体

architectureRAM_archofRAMis

subtypewordisstd_logic_vector(7downto0);

typememoryisarray(0to15)ofword;

signaladr_in:

integerrange0to15;

signalsram:

memory;

begin

adr_in<=conv_integer(ADR);

process(wr)begin

if(wr'eventandwr='1')then

if(cs='1'andwr='1')then

sram(adr_in)<=dinafter2ns;

endif;

endif;

endprocess;

process(rd,cs)begin

if(rd='0'andcs='1')then

dout<=sram(adr_in)after3ns;

else

dout<="ZZZZZZZZ"after4ns;

endif;

endprocess;

endRAM_arch;

例7:

利用枚举类型设计一个状态机,用灯的颜色代表相应的状态名。

libraryIEEE;

useIEEE.std_logic_1164.all;

ENTITYtraffic_lightIS

PORT(sensor,clock:

instd_logic;

red_light,green_light,yellow_light:

outstd_logic

);

endtraffic_light;

architectureabcoftraffic_lightis

typet_stateis(red,green,yellow);

signalpresent_state,next_state:

t_state;

begin

process(present_state,sensor)

begin

casepresent_stateis

whengreen=>

next_state<=yellow;

red_light<='0';

green_light<='1';

yellow_light<='0';

whenred=>

red_light<='1';

green_light<='0';

yellow_light<='0';

if(sensor='1')then

next_state<=green;

else

next_state<=red;

endif;

whenyellow=>

red_light<='0';

green_light<='0';

yellow_light<='1';

next_state<=red;

endcase;

endprocess;

process

begin

waituntilclock'eventandclock='1';

present_state<=next_state;

endprocess;

endabc;

该状态机由两个进程描述,第一计算下一个状态逻辑,第二个锁存下一个状态到当前状态。

例8:

用VHDL设计一家用告警系统的控制逻辑,告警系统有来自传感器的三个输入信号smoke、door、water和准备传输到告警设备的三个输出触发信号fire_alarm、burg_alarm、water_alarm以及使能信号en和alarm_en。

VHDL程序描述如下:

LIBRARYieee;

USEieee.std_logic_1164.all;

ENTITYalarmIS

PORT(smoke,door,water:

INstd_logic;

en,alarm_en:

INstd_logic;

fire_alarm,burg_alarm:

OUTstd_logic;

water_alarm:

OUTstd_logic);

ENDalarm;

图例8 家用告警系统的控制逻辑电路图

ARCHITECTUREalarm_arcOFalarmIS

BEGIN

PROCESS(smoke,door,water,en,alarm_en)

BEGIN

IF((smoke=‘1’)AND(en=‘0’))THEN

fire_alarm<=‘1’;

ELSE

fire_alarm<=‘0’;

ENDIF;

IF((door=‘1’)AND((en=‘0’)AND(alarm_en=‘0’)))THEN

burg_alarm<=‘1’;

ELSE

burg_alarm<=‘0’;

ENDIF;

IF((water=‘1’)AND(en=‘0’))THEN

water_alarm<=‘1’;

ELSE

water_alarm<=‘0’;

ENDIF;

ENDPROCESS;

ENDalarm_arc;

程序中用了三个分开的IF语句描述其功能,它们都没有ELSIF关键字,可以看出每个IF语句描述了一个输出端口。

第一个IF语句是检测有没有烟雾报警情况,有烟雾火警灾情发生立即产生报警信号,触发fire_alarm。

第二和第三IF语句检测不同的报警信号,和第一句相仿。

此模块的输入端口有两个使能信号,en使所有的输入都能到达输出,而用alarm_en端口,只对防盗告警系统使能。

需要指出的是这种功能很容易用逻辑方程描述,如前面的并行行为程序的例子。

但是有时IF语句的形式是更可读、更容易理解。

图8-11给出了报警控制逻辑电路图。

返回