ISE101软件操作步骤.docx

《ISE101软件操作步骤.docx》由会员分享,可在线阅读,更多相关《ISE101软件操作步骤.docx(14页珍藏版)》请在冰豆网上搜索。

ISE101软件操作步骤

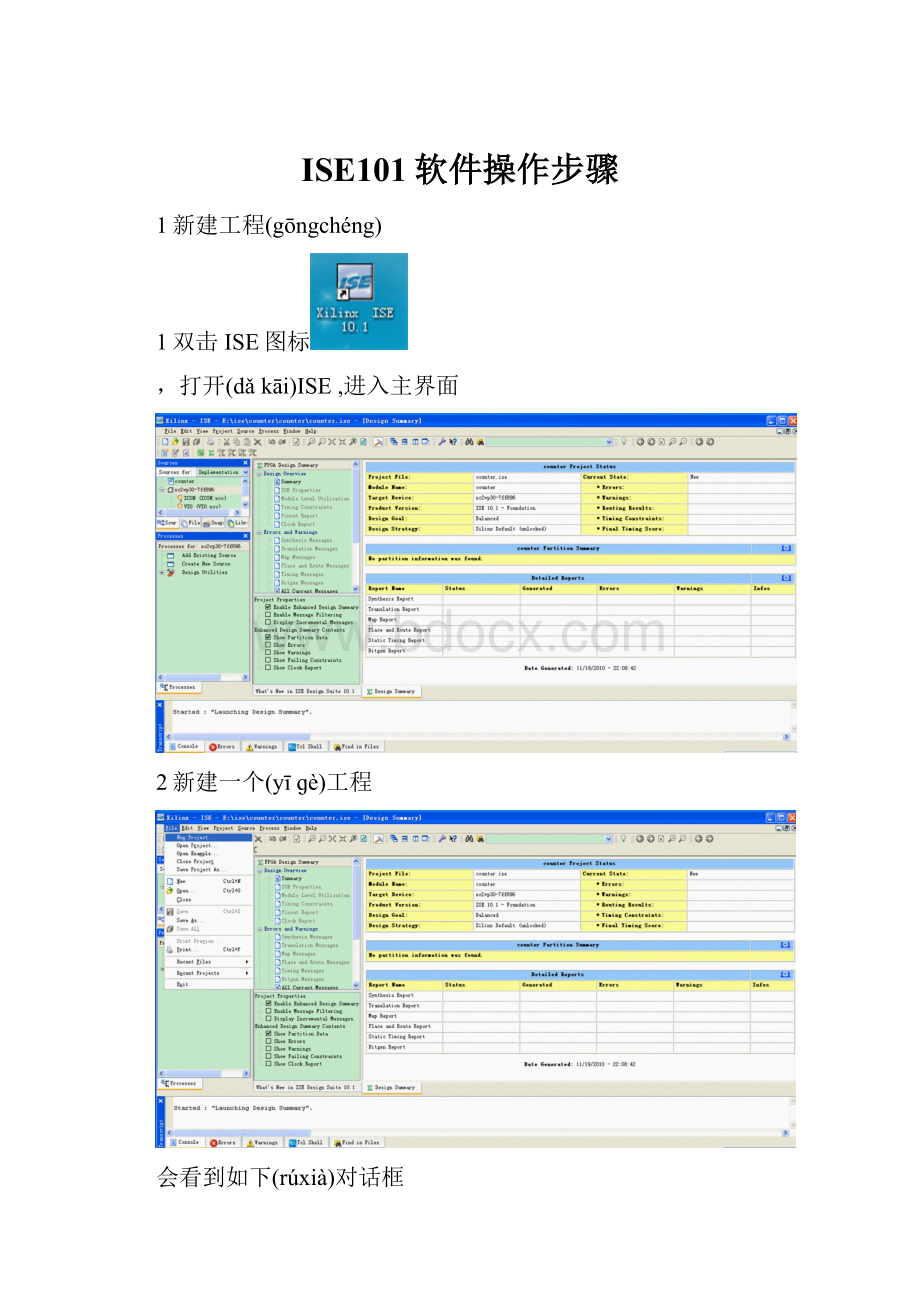

1新建工程(gōngchéng)

1双击ISE图标

,打开(dǎkāi)ISE,进入主界面

2新建一个(yīɡè)工程

会看到如下(rúxià)对话框

建立一个(yīɡè)工程名,注意文件的存储路径必须是英文,不能含有(hányǒu)汉字,选择next,进入(jìnrù)下一个对话框

选择相应的FPGA的型号,选择next,一直选择next,直到finish,然后(ránhòu)将会看到如下界面

3在工程(gōngchéng)suorcefor的下面的空白处单击,添加新的文件。

如下图所示。

选择(xuǎnzé)newsource之后将会看到如下对话框

给文件添加工程(gōngchéng)名,选择VerilogModule,注意(zhùyì)filename的工程名要加后缀.v,选择next,一直(yīzhí)到finish。

然后将会看到如下界面

2添加程序

1选择合适(héshì)的程序输入进去,注意保存。

2再在sourcefor的空白处单击,新建一个(yīɡè)newsource

选择(xuǎnzé)后,将会看到如下对话框

选择(xuǎnzé)testbenchwaveform,filename的文件名加下划线,作为与其他(qítā)文件的区分。

然后(ránhòu)一直next,直到看到如下对话框。

在InitialLengthofTestBench中可以选择所要仿真的时间(shíjiān)长度。

点击finish后就会看到如下界面。

有蓝色部分的是可以选择的,你能选择你所需要(xūyào)仿真的数据。

3仿真(fǎnɡzhēn)程序

1选定(xuǎndìnɡ)后,点击Source框下的的Sourcefor,如下图所示。

选择(xuǎnzé)Sourcefor选项下地BehavooralSimulation。

Processes框下的Processes

然后再在Source框下选择lizi.v。

打开XilinxISESimiltor下的子文件,双击SimilateBehavioralModel,进行仿真。

在最下面(xiàmian)的栏目中将会显示程序运行得进度,以及是否会出现错误。

仿真完成后就会出现(chūxiàn)如下界面

4给文件(wénjiàn)加核

Source框下的空白处右击,添加一个(yīɡè)sourcefor文件,与前面相同,然后会看到如下对话框。

选择你所需要添加(tiānjiā)的核,注意filename的文件名必须是你所添加的核的文件名。

然后选择(xuǎnzé)next,会出现如下对话框。

选择你添加(tiānjiā)的核,点击next,直到出现如下对话框

在NemberofControlParts下选择所需要(xūyào)添加的核的个数,然后finish.

添加(tiānjiā)成功的核会显示(xiǎnshì)在Source框中,如下图所示

添加其他(qítā)核的步骤也是这样,不同的是改变NemberofControlParts选项中的数字。

5Constraints

1添加时钟(shízhōng),在Processes中选择UserConstraints下的“FloorplanIO”并双击。

在弹出的对话框中,然后将时钟CLK托动到“AJ15”然后关闭对话框保存就可以完成对时钟的添加了。

(如果是组合逻辑,就不需要时钟约束)

6synthesizeyourdesign

在ISE里进行(jìnxíng)综合,在processes窗口中双击Synthesize—XST,如果有错误(cuòwù)就按照报错点修改,直到没有错误。

7implementyourdesign

双击“ImplementDesign”实现(shíxiàn)设计。

8GenerateProgrammingFile

双击“GenerateProgrammingFile”生成(shēnɡchénɡ)bit文件

9AnalyzeDesignUsingChipscope

1试在Processes窗口(chuāngkǒu)中选择双击“AnalyzeDesignUsingChipscope”进入ChipScopeProAnalyzer窗口,点击

图标检查连接情况。

2然后下载bit文件(wénjiàn)到板子上,单击菜单栏中的“Device”,在下拉菜单中选择所用(suǒyònɡ)器件,在所用(suǒyònɡ)器件名上右击然后选“Configure”,在弹出的对话框中单击“SelectNewFile”,在工程(gōngchéng)目录中选择.bit文件,单击打开。

3双击VIOConsole,进入(jìnrù)VIOConsle窗口,进行观测调试,验证实验的准确性。

内容总结

(1)1新建工程

1双击ISE图标,打开ISE,进入主界面

2新建一个工程

会看到如下对话框

建立一个工程名,注意文件的存储路径必须是英文,不能含有汉字,选择next,进入下一个对话框

选择相应的FPGA的型号,选择next,一直选择next,直到finish,然后将会看到如下界面

3在工程suorcefor的下面的空白处单击,添加新的文件