七人表决器课程设计报告Word文档格式.docx

《七人表决器课程设计报告Word文档格式.docx》由会员分享,可在线阅读,更多相关《七人表决器课程设计报告Word文档格式.docx(7页珍藏版)》请在冰豆网上搜索。

3.编写各功能模块VHDL语言程序;

4.对各功能模块进展编译、综合、仿真和验证;

5.顶层文件设计,可用VHDL语言设计,也可以用原理图设计;

6.整个系统进展编译、综合、仿真和验证;

7.在CPLD/FPGA实验开发系统试验箱上进展硬件验证;

8.按所布置的题目要求,每一位学生独立完成全过程。

二、课程设计应完成的工作

1.所要求设计内容的全部工作;

2.按设计指导书要求提交一份报告书;

3.提交电子版的设计全部内容:

工程目录文件夹中的全部内容,报告书

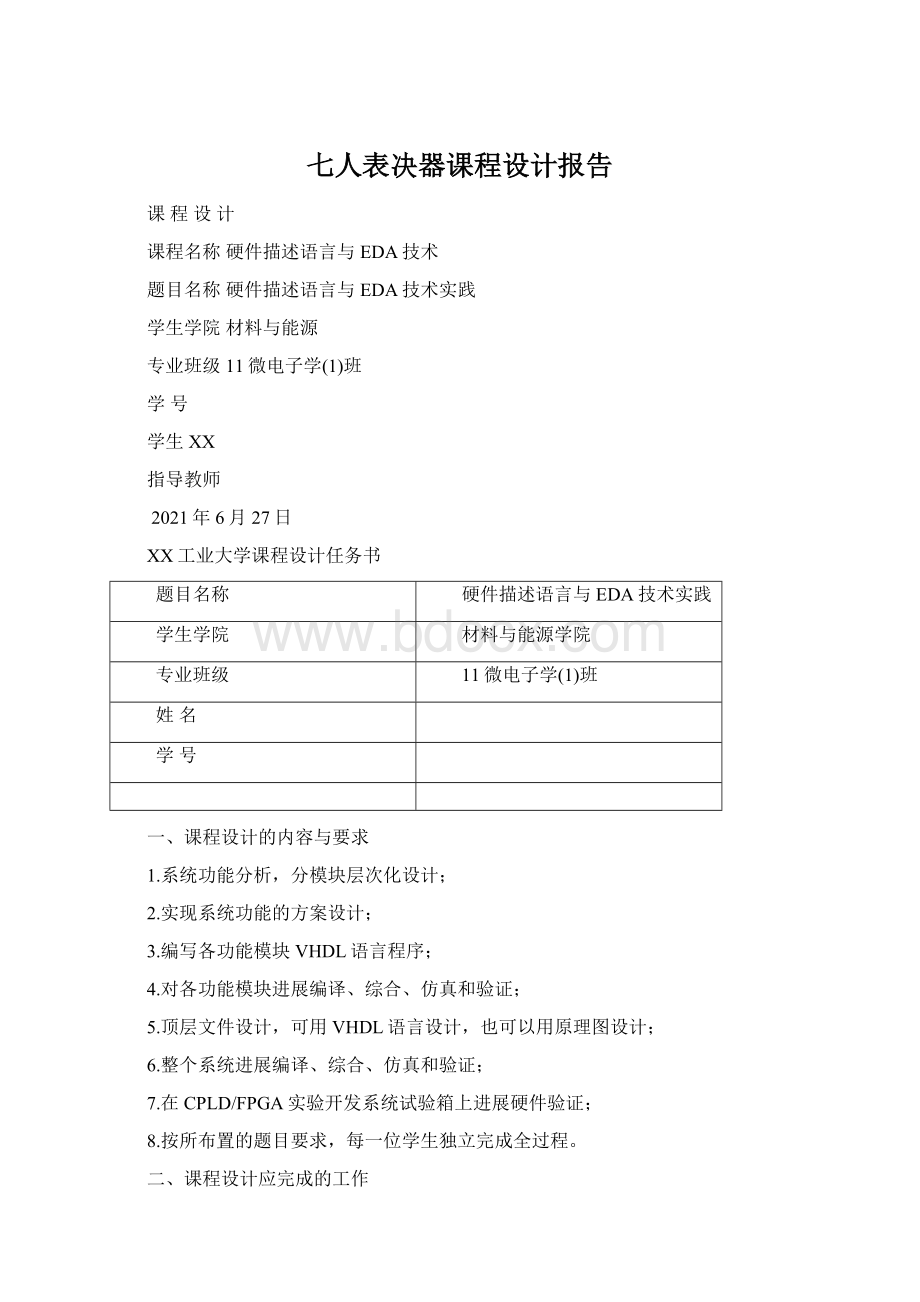

三、课程设计进程安排

序号

设计各阶段内容

地点

起止日期

1

布置设计题目和要求;

收集相关资料。

工3-317或宿舍

6.23

2

方案分析与确定;

编写VHDL源程序。

6.24

3

编写VHDL源程序;

编译、综合、仿真、定时分析、适配。

6.25

4

下载和硬件验证;

验收。

工3-317

6.26

5

验收;

撰写报告

6.27

6

7

8

四、应收集的资料及主要参考文献

1.陈先朝,硬件描述语言与EDA技术实践指导书,2021年3月

2.曹昕燕等编著,EDA技术实验与课程设计,清华大学,2006年5月

3.X欲晓等编著,EDA技术与VHDL电路开发应用实践,电子工业,2021年4月

4.X昌华等编著,数字逻辑EDA设计与实践:

MAX+plusⅡ与QuartusⅡ双剑合璧,国防工业,2021年

5.X江海主编,EDA技术课程设计,华中科技大学,2021年1月

发出任务书日期:

2021年6月23日指导教师签名:

方案完成日期:

2021年6月27日基层教学单位责任人签章:

主管院长签章:

七人表决器

1.设计目的

(1)学习和掌握QuartusII软件的根本操作;

(2)通过设计七人表决器,掌握基于可编程器件的VHDL硬件描述语言的设计方法;

(3)学习用CPLD/FPGA实践系统硬件验证电路设计的正确性

2.设计题目及要求

(1)题目:

表决器

(2)要求:

设计一个七人表决器,当赞成人数大于等于四时显示表决通过,同时分别将投票中赞成的人数和反对的人数在数码管上显示出来。

3.设计方案:

表决器的功能是将所投票者的结果综合起来,超过半数赞成那么表示结果通过,反之那么不通过。

而七人表决器由七个人来投票,当赞成的票数大于或者等于4人,那么认为通过;

当反对的票数大于或者等于4人时,那么认为不通过。

所以这次设计中我将用7个数据开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;

否那么假设拨挡开关输入为‘0’时,那么表示此人反对。

表决的结果用一个LED表示,假设表决的结果为同意,那么LED被点亮,;

否那么,如果表决的结果为反对,那么LED不会被点亮。

同时用七段显示数码管来显示赞成的人数和反对的人数。

4.实验箱使用说明

本次使用的实验箱为KHF-3型CPLD/FPGA实践开发系统

所用芯片:

ACEX1K系列的EP1K30QC208-3,引脚为208个,5980逻辑单元。

数据开关SW1至SW7分别代表7人。

当数据开关按下时输出为高电平‘1’,代表该投票者赞成,反之输出为低电平‘0’,代表该投票者反对。

数码管SEG1为赞成者人数,数码管SEG4为反对者人数

LED灯SEG5对应的P190为结果通过指示灯,当灯点亮,那么代表投票结果为通过,反之熄灭时代表投票结果不通过。

5.设计流程图

6.VHDL程序设计

LIBRARYIEEE;

--库的说明

ENTITYbjqIS--定义实体bjq

PORT--端口说明

(clk:

INSTD_LOGIC;

--时钟输入端口

vote:

INSTD_LOGIC_VECTOR(6DOWNTO0);

--七人投票端

LED_pass:

OUTSTD_LOGIC;

--结果LED灯

LED_approve,LED_object:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

--赞成人数及反对人数显示数码管

ENDENTITYbjq;

ARCHITECTUREbhvOFbjqIS--构造体说明

SIGNALq:

STD_LOGIC;

--内部信号说明

SIGNALq1,q2:

STD_LOGIC_VECTOR(6DOWNTO0);

BEGIN

PROCESS(vote)

VARIABLEA:

INTEGER;

--定义变量A用于统计赞成人数

BEGIN

A:

=0;

IFclk'

EVENTANDclk='

1'

THEN

IFvote(0)='

THENA:

=A+1;

ENDIF;

IFvote

(1)='

IFvote

(2)='

IFvote(3)='

IFvote(4)='

IFvote(5)='

IFvote(6)='

CASEAIS--通过CASE语句选择不同赞成人数下LED数码管的显示内容

WHEN0=>

q<

='

0'

;

q1<

="

1111110"

q2<

1110000"

WHEN1=>

0110000"

1011111"

WHEN2=>

1101101"

1011011"

WHEN3=>

1111001"

0110011"

WHEN4=>

WHEN5=>

WHEN6=>

WHEN7=>

WHENOTHERS=>

Z'

ZZZZZZZ"

ENDCASE;

LED_pass<

=q;

--将结果送到LED灯及数码管

LED_approve<

=q1;

LED_object<

=q2;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREbhv;

7.仿真

端口设置完毕后如以下列图所示:

仿真的最终结果:

8.仿真波形分析

(1)当输入vote为1100101时,表示有4人投于赞成票,LED_approve显示为0110011,即数码管显示为‘4’,LED_object显示为1111001,即数码管显示为‘3’,LED_pass为高电平即点亮;

(2)当输入vote为1100000时,表示有2人投于赞成票,LED_approve显示为1101101,即数码管显示为‘2’,LED_object显示为1011011,即数码管显示为‘5’,LED_pass为低电平即熄灭;

(3)当输入vote为1100001时,表示有3人投于赞成票,LED_approve显示为1111001,即数码管显示为‘3’,LED_object显示为0110011,即数码管显示为‘4’,LED_pass为低电平即熄灭;

(4)当输入vote为1100010时,表示有3人投于赞成票,LED_approve显示为1111001,即数码管显示为‘3’,LED_object显示为0110011,即数码管显示为‘4’,LED_pass为低电平即熄灭;

如此说明,仿真结果符合实际要求需要。

9.管脚分配

10.设计所遇到的问题

这次设计中所遇到的最大困难在于仿真。

由于对仿真的功能不够熟悉,一开场对于输入波形的设置就乱了阵脚。

最初时钟信号的输入设置并没有很大问题,但是我并没有考虑到仿真时的endtime。

由于endtime设置比拟小,使得仿真结果并不完善。

后来请教了同学后才发现了这问题。

由于输入为多通道输入,每一个vote信号我都使用了一个random波形,使得输入十分的紊乱,输出结果更是一塌糊涂。

后来将vote变成二进制类型输入,并且随机设置了初始值,解决了这个问题。

11.设计的收获和体会

通过这次EDA的课程设计使我对于QuartusII的了解更加深入。

不仅学到了如何通过VHDL硬件描述语音来实现可编程器件的运用,还学到了如何利用QuartusII的强大的仿真功能验证器件功能的正确性。

但更多的是能够自己动手,这样的实践会比光看书更为有用。

在实践中我们可以发现一般书上可能不会出现的问题,这样问题出现了我们便可以通过自己开掘的途径解决问题,加深我们对这问题的认识,所谓实践出真知。

12.参考文献

〔1〕陈先朝,硬件描述语言与EDA技术实践指导书,2021年3月

〔2〕曹昕燕等编著,EDA技术实验与课程设计,清华大学,2006年5月

〔3〕X欲晓等编著,EDA技术与VHDL电路开发应用实践,电子工业,2021年4月

〔4〕X昌华等编著,数字逻辑EDA设计与实践:

〔5〕X江海主编,EDA技术课程设计,华中科技大学,2021年1月