FPGA交通灯控制程序设计Word格式文档下载.docx

《FPGA交通灯控制程序设计Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《FPGA交通灯控制程序设计Word格式文档下载.docx(25页珍藏版)》请在冰豆网上搜索。

010100"

,再经过5秒,S变为B"

……如此循环下去。

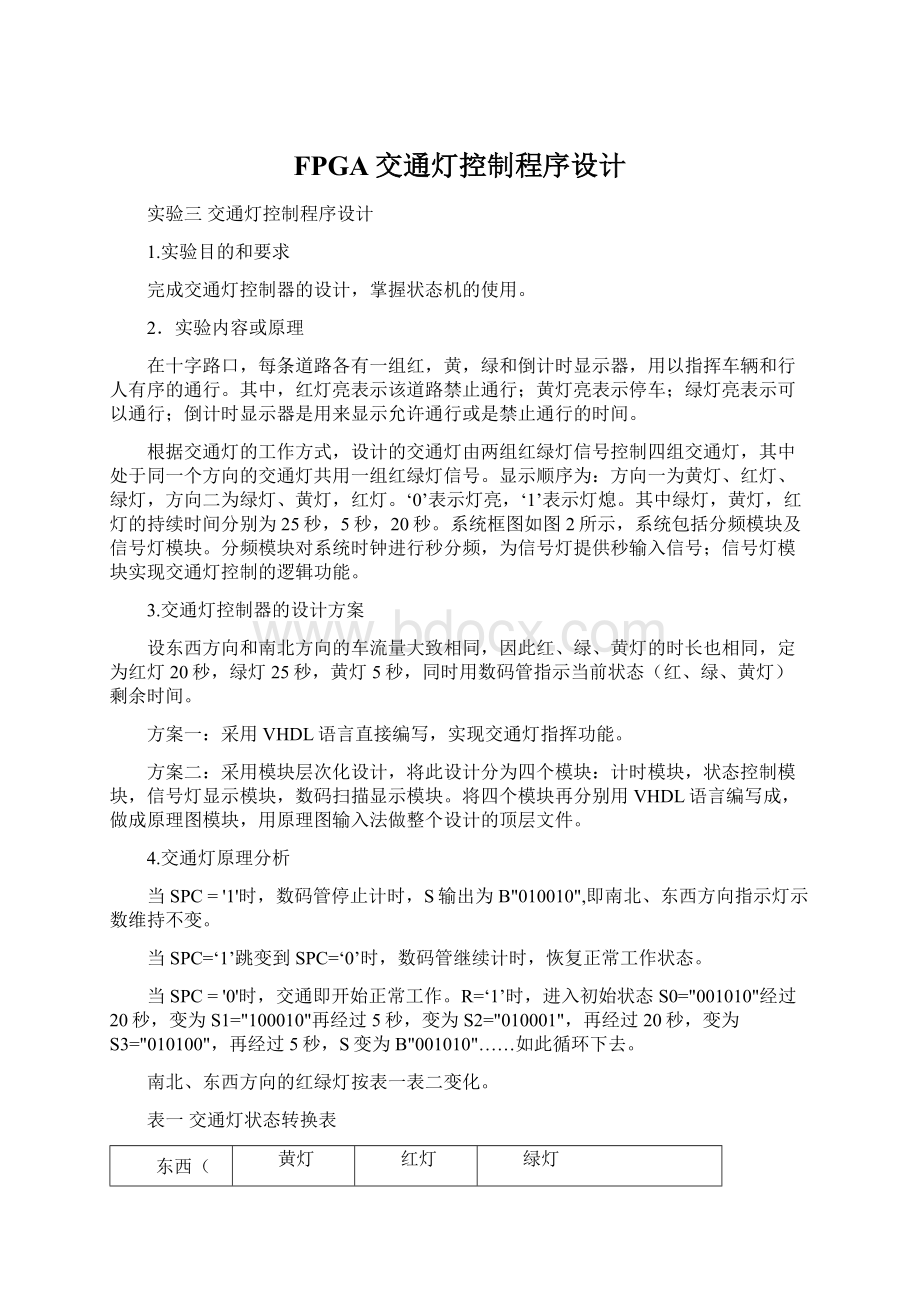

南北、东西方向的红绿灯按表一表二变化。

表一交通灯状态转换表

东西(A)方向

黄灯

红灯

绿灯

5秒

20秒

25秒

南北(B)方向

5

表二交通灯状态转换表

SPC

S

备注

1

010010

指示灯示数维持不变

S0:

001010

持续5秒,转到S1

S1:

100010

持续20秒,转到S2

S2:

010001

持续5秒,转到S3

S3:

010100

持续20秒,转到S0

注:

S的六位分别对应东西方向(A方向)的红绿黄和南北方向(B方向)的红绿黄。

‘1’表示亮,‘0’表示灭。

5.VHDL仿真实验

(1)为此工程新建一个文件夹。

启动QuartusII软件工作平台,新建工程设计文件名为traffic.vhd。

在新建的VHDL模型窗口下编写源程序代码如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

USEIEEE.STD_LOGIC_ARITH;

ENTITYtrafficIS

PORT(CLK,R,SPC:

INSTD_LOGIC;

LIGHT:

OUTSTD_LOGIC_VECTOR(5DOWNTO0);

Q1,Q2:

OUTINTEGERRANGE0TO25;

LED1,LED2,LED3,LED4:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));

ENDtraffic;

ARCHITECTUREbehavOFtrafficIS

TYPESTATESIS(S0,S1,S2,S3);

SIGNALSTATE:

STATES;

SIGNALT1,T2:

INTEGERRANGE0TO25;

SIGNALL1,L2,L3,L4:

INTEGERRANGE0TO9;

BEGIN

P1:

PROCESS(CLK,STATE)

BEGIN

IFR='

THENSTATE<

=S0;

T1<

=20;

T2<

=25;

ELSIFSPC='

THENLIGHT<

="

;

ELSIFCLK'

EVENTANDCLK='

THEN

CASESTATEIS

WHENS0=>

LIGHT<

T1<

=T1-1;

=T2-1;

Q1<

=T1;

Q2<

=T2;

IFT1=0THEN

STATE<

=S1;

=5;

ENDIF;

WHENS1=>

=S2;

WHENS2=>

IFT2=0THEN

=S3;

WHENS3=>

WHENOTHERS=>

STATE<

ENDCASE;

endPROCESS;

p2:

PROCESS(T1,T2)

begin

L1<

=T1/10;

L2<

=T1REM10;

L3<

=T2/10;

L4<

=T2REM10;

ENDPROCESS;

P3:

PROCESS(L1)

BEGIN

CASEL1IS

WHEN0=>

LED1<

0000"

WHEN1=>

0001"

WHEN2=>

0010"

WHEN3=>

0011"

WHEN4=>

0100"

WHEN5=>

0101"

WHEN6=>

0110"

WHEN7=>

0111"

WHEN8=>

1000"

WHEN9=>

1001"

LED1<

P4:

PROCESS(L2)

CASEL2IS

LED2<

LED2<

P5:

PROCESS(L3)

CASEL3IS

LED3<

LED3<

P6:

PROCESS(L4)

CASEL4IS

LED4<

LED4<

ENDbehav;

(2)创建工程及全程编译。

完成源代码输入后即可创建工程然后进入全程编译,检查设计是否正确。

选择Tools->

NetlistViewers->

RTLViewers命令,即HDL的RTL级图形观测器,选择好后即自动弹出计数器设计的RTL电路,如下图:

(3)仿真。

建立波形编辑文件进行时序仿真或时序仿真,仿真结果如下图所示,

时序仿真:

4)硬件测试。

完成仿真实验后,若仿真结果无误,则进行锁脚,然后下载到FPGA实验箱上进行硬件测试。

选择试验箱的模式为模式5,时钟CLK选择为CLOCK0(PIN_28脚),频率f=4Hz,LDE1[3..0]对应的引脚编号PIN-20,19,18,17,LDE2[3..0]对应的引脚编号PIN-16,15,14,13,LDE3[3..0]对应的引脚编号PIN-136,135,134,133,LDE4[3..0]对应的引脚编号PIN-132,128,41,21,LIGHT[5..0]对应的引脚编号PIN7,6,4,3,2,1,R对应的引脚编号PIN-233,SPC对应的引脚编号PIN-234.

6.实践教学报告要求

将实验原理、设计过程、编译仿真波形和分析结果、硬件测试实验结果写进实验报告。

本论文格式严格按照课程设计

要求格式,基本没有任何问题。

中国XXXXX学校

课程设计任务书

题目交通灯控制器的设计

专业学号姓名

主要内容、基本要求、主要参考资料等:

主要内容

1.学习ALTERA公司的FPGA/CPLD的结构、特点和性能。

2.学习集成开发软件MAX+plusII/QuartusII的使用及设计过程。

3.熟悉EDA工具设计数字电路设计方法,掌握VHDL硬件描述语言设计方法。

4.根据给定题目设计数字电路,来加深对可编程逻辑器件的理解和掌握。

技术要求

1.在所选择器件内完成交通灯控制器的设计,要求设计完成后芯片具有交通灯控制器的全部功能、包括显示和操作接口。

2.交通灯控制器要求控制十字路口两道路的交通灯,两道路交替通行,每次通行时间可设定20——60秒之间,每个路口要求有前行、禁止、人行灯。

(根据实际设计进度考虑可以增加左右转向灯,等待和通行时间显示等)。

主要参考资料

1.康华光主编,《电子技术基础-数字部分》,高等教育出版社,1998。

2.谭会生等主编,《EDA技术及应用》,西安电子科技大学出版社,2001

3.潘松等主编,《EDA技术实用教程》,科学出版社,2006

4.雷伏容主编,《VHDL电路设计》,清华大学出版社,2006

5.CharlesH.Roth等著,《数字系统设计与VHDL》,电子工业出版社,2008

完成期限:

2012年7月2日

指导教师签章:

专业负责人签章:

2012年6月25日

摘要

可编程逻辑器件,不仅速度快、集成度高,并且能随心所欲地完成用户定义的逻辑功能,还可以加密和重新编程,其编程次数最大可达1万次以上。

使用可编程逻辑器件可以大大简化硬件系统、降低成本、提高系统的可靠性、灵活性和保密性。

关键词:

可编程逻辑器件稳定可靠低成本

第一章EDA技术概述

第一节EDA技术及其发展

现代电子设计技术的核心是EDA(ElectronicDesignAutomation)技术。

EDA技术就是依赖功能强大的计算机,在EDA工具软件平台上,对以硬件描述语言HDL(HardwareDescriptionLanguage)为系统逻辑描述手段完成的设计文件,它能自动地完成逻辑编译、逻辑化简、逻辑分割、逻辑综合、结构综合(布局布线),以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

EDA技术使得设计者的工作仅限于利用软件的方式,即利用硬件描述语言和EDA软件来完成对系统硬件功能的实现。

EDA技术在进入21世纪后,得到了更大的发展。

在仿真和设计两方面支持标准硬件描述语言的功能越来越强大,软硬件技术也进一步得到了融合,在电子行业的产业领域、技术领域和设计应用领域得到了进一步的肯定,使得复杂电子系统的设计和验证趋于简单化。

第二节可编程逻辑器件概述

可编程逻辑器件(简称CPLD)是允许用户编程(配置)实现所需逻辑功能的电路,一般可利用计算机辅助设计,即用原理图、状态机、硬件描述语言(VHDL)等方法来表示设计思想,经过一系列编译或装换程序,生成相应的目标文件,再由编程器或下载电缆将设计文件配置到目标器件中,这时的可编程逻辑器件就可作为满足用户需求的专用集成电路使用了。

PLD的出现,打破了由中小规模通用型集成电路和大规模专用集成电路垄断的局面,在通信、数据处理、网络、仪器、工业控制、军事和航空航天等众多领域得到广泛应用,可以预见,不久的将来,PLD将在集成电路市场占统治地位。

第三节FPGA/CPLD概述

FPGA(现场可编程门阵列)和CPLD(复杂可编程逻辑器件)都是可编程逻辑器件,他们是在PAL,GAL等逻辑器件的基础上发展起来的。

同以往的PAL,GAL相比较,FPGA/CPLD的规模比较大,它可以替代几十甚至几千块通用IC芯片。

这样的FPGA/CPLD实际上就是一个子系统部件。

这种芯片受到世界范围内电子工程设计人员的广泛关注和普遍欢迎。

比较典型的就是Altera公司和Xilinx公司的CPLD器件系列和FPGA器件系列,他们开发较早,占用了较大的PLD市场。

对用户而言,虽然FPGA/CPLD的内部结构稍有不同,但其用法都一样,所以大多数情况下,不加以区分。

FPGA/CPLD芯片都是特殊的ASIC芯片,除了具有ASIC的特点外,还具有以下几个优点:

(1)随着VLSI(VeryLargeScaleIC,超大集成电路)工艺的不断提高单一芯片内部可以容纳上百万个晶体管,FPGA/CPLD芯片的规模也越来越大,其单片逻辑门数已达到上百万门,它所实现的功能也越来越强,同时也可以实现系统集成,即片上系统SOC.

(2)FPGA/CPLD芯片在出厂之前都做过百分之百的测试,不需要设计人员承担芯片风险和费用,设计人员只需在自己的实验室就可以通过相关的软硬件环境来完成芯片的最终功能设计。

所以,FPGA/CPLD的资金投入就小,减少了潜在的花费。

(3)用户可以反复地编程、擦除、使用或者在外围电路不动的情况下用不同软件就可实现不同的功能。

FPGA/CPLD软件包中有各种输入工具和仿真工具,及版图设计工具和编程器等全线产品,电路设计人员在很短的时间内就可完成电路的输入、编译、优化。

仿真,直至最后芯片的制作。

当电路有少量的改动,更能显示FPGA/CPLD的优势。

电路设计人员在使用FPGA/CPLD进行电路设计时,不需要具有专门的IC(集成电路)深层次的知识,FPGA/CPLD软件易学易用,能使设计人员更能集中精力进行电路设计,快速将产品推向市场。

(4)在线可编程技术(ISP)使得使用FPGA/CPLD的产品可以做到远程升级。

第二章设计思路

第一节设计思路

所设计的交通信号灯控制电路,主要适用于在两条干道汇合点形成的十字交叉路口,路口设计两组红绿灯分别对两个方向上的交通运行状态进行管理。

东西方向和南北方向各使用3个LED显示,红黄绿各代表红黄绿灯,绿灯亮同时是人行灯。

东西方向和南北方向计时均为2位数,共需要4个LED七段数码管显示。

Time信号输出显示的内容。

采用EPF10K10LC84-4实现控制

总体设计图,如下

Clk1r

Keyg

t

r1

g1

t1

time1[4..0]

time2[4..0]

c

图

(一)

东西向

交通灯

南北向

Main

数码管显示

25mhz有源晶振

第二节所实现功能说明

南北和东西方向各有一组绿,人行,红,黄灯,各自的持续时间分别为20s,20s,25s,5s;

用两组数码管,以倒计时方式显示两个方向允许通行或禁止通行的剩余时间;

绿灯也可看做人行灯;

第三章各模块的编程实现

第一节时基脉冲发生模块

在红绿灯交通信号系统中,大多数的情况是通过自动控制的方式指挥交通的。

因此,为了避免意外事件的发生,电路必须给出一个稳定的时钟才能让系统正常的工作。

因此时钟发生模块最主要的功能就是产生一些稳定的输出信号,并将其用做后面几个电路的使能控制与同步信号。

通过编程实现1Hz脉冲的产生,程序如下所示。

LibraryIEEE;

useIEEE.std_logic_1164.all;

ENTITYCLKGENIS

PORT(CLK1:

INSTD_LOGIC;

CLK:

OUTSTD_LOGIC);

ENDCLKGEN;

ARCHITECTUREbehavOFCLKGENIS

SIGNALCNTER:

INTEGERRANGE0TO25000000;

BEGIN

PROCESS(CLK)BEGIN

IFCLK'

THEN

IFCNTER=25000000THENCNTER<

=0;

ELSECNTER<

=CNTER+1;

PROCESS(CNTER)

IFCNTER=12500000THENCLK<

='

IFCNTER=25000000THENCLK<

第二节计数及红绿灯控制模块

南北向和东西向各有一组红黄绿灯,各自持续的时间为分别为25s、5s、20s。

通过编程可以实现控制各通道的计数控制且输出为二进制数,并且可以控制各灯的亮灭情况,高电平为亮,低电平为灭。

东西向模块程序为:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitydaolu1is

port(

clk:

instd_logic;

timel:

outstd_logic_vector(4downto0);

r,g,t:

outstd_logic);

enddaolu1;

architecturedaoduofdaolu1is

typecoloris(green,yellow,red);

process(clk)

variablereset:

std_logic:

variabletempr,tempg,tempt:

std_logic;

variabletemp_l:

std_logic_vector(4downto0);

variabletemp_color:

color:

=green;

begin

if(clk'

eventandclk='

)then

casetemp_coloris

whenyellow=>

tempr:

tempg:

tempt:

caseresetis

when'

=>

temp_l:

00100"

reset:

whenothers=>

casetemp_lis

when"

00000"

=>

temp_l:

11000"

temp_color:

=red;

whenothers=>

=temp_l-1;

endcase;

endcase;

whengreen=>

tempr:

tempg:

caseresetis

when'

10011"

reset:

whenothers=>

casetemp_lis

when"

temp_l:

temp_color:

=yellow;

whenothers=>

endcase;

whenred=>

endcase;

endif;

timel<

=temp_l;

r<

=tempr;

g<

=tempg;

t<

=tempt;

endprocess;

end;

南北向模块程序为:

useieee.std_lo