晶振的主要全参数及其对电路的影响Word下载.docx

《晶振的主要全参数及其对电路的影响Word下载.docx》由会员分享,可在线阅读,更多相关《晶振的主要全参数及其对电路的影响Word下载.docx(13页珍藏版)》请在冰豆网上搜索。

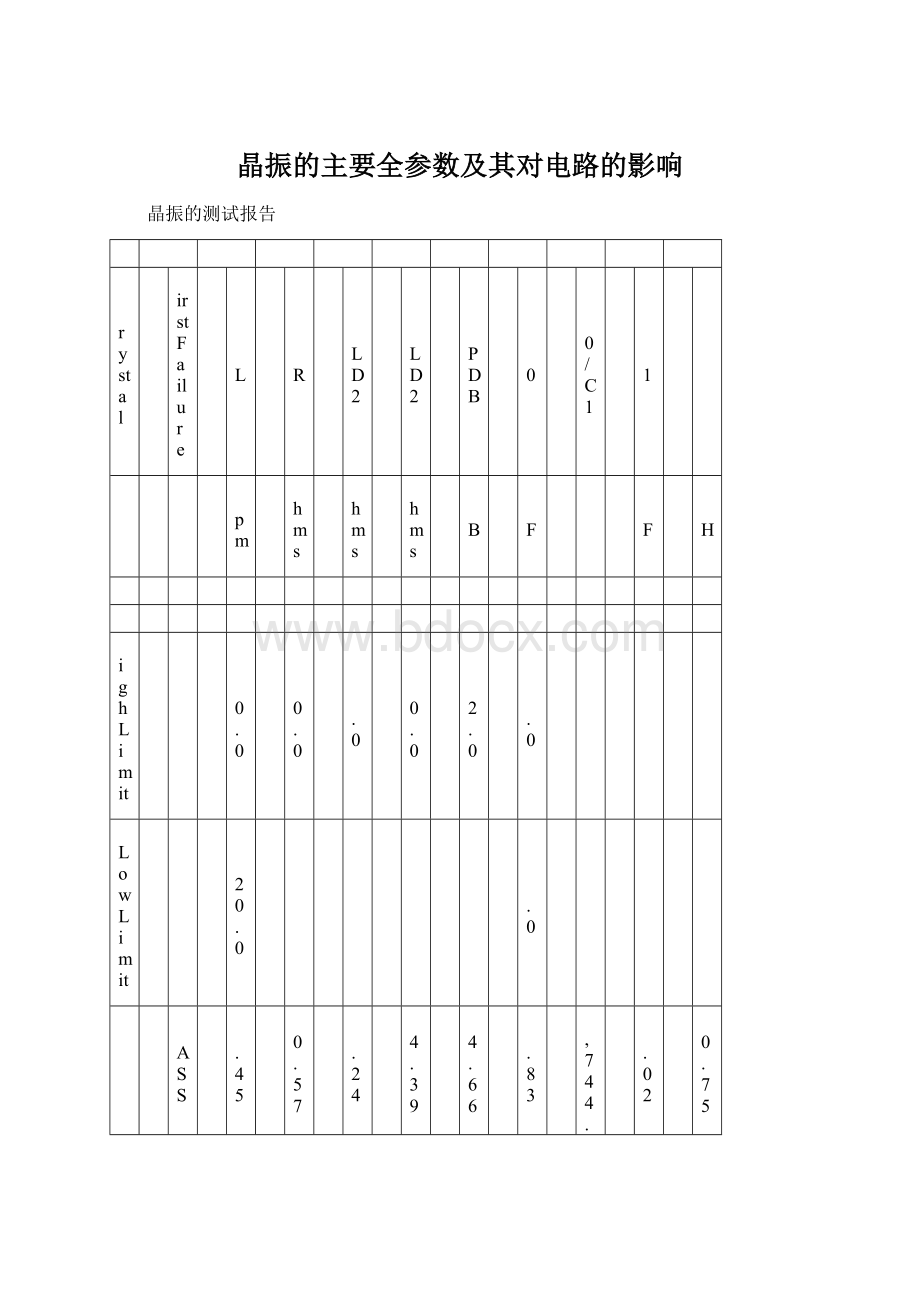

80.0

8.0

-2.0

7.0

LowLimit

-20.0

1.0

1

PASS

3.45

50.57

2.24

54.39

-4.66

3.83

3,744.84

1.02

10.75

2

-5.84

32.05

4.18

36.30

-6.96

3.86

4,113.29

0.94

11.70

3

FailDLD2High

0.44

73.86

27.81

108.17

-3.59

3.74

3,613.27

1.03

10.63

4

FailSPDBHigh

-8.97

33.67

2.06

37.55

-0.44

3.92

5,538.01

0.71

15.54

5

-1.27

40.11

1.65

42.75

-7.86

3.89

3,955.09

0.98

11.17

6

-6.74

30.12

4.38

34.23

-9.58

3.81

3,608.85

1.06

10.42

7

-3.52

41.97

1.52

42.86

-6.95

3.85

4,670.19

0.82

13.35

8

1.13

38.34

2.07

40.46

-4.15

3.88

5,017.95

0.77

14.23

9

-7.01

21.31

0.73

21.80

-9.89

3,018.17

1.27

8.67

10

-3.62

24.75

52.36

78.55

-10.30

2,943.39

1.31

8.37

晶振的等效电器模型

C0,是指以水晶为介质,由两个电极形成的电容。

也称为石英谐振器的并联电容,它相当于以石英片为介质、以两电极为极板的平板电容器的电容量和支架电容、引线电容的总和。

几~几十pF。

R1等效石英片产生机械形变时材料的能耗;

几百欧

C1反映其材料的刚性,10^(-3)~10^(-4)pF

L1大体反映石英片的质量.mH~H

晶振各种参数

晶振的一些参数并不是固定的大部分是会随温度、频率、负载电容、激励功率变化的

RR谐振电阻越小越好影响:

过大造成不易起振、电路不稳定

阻抗RR越小越容易起振,反之若ESR值較高則較不易起振。

所以好的Crystal設計應在ESR與Co值間取得平衡。

C1动态电容

L1动态电感

C0静电容影响:

不能太高,否則易产生较大的副波,影响频率稳定性

LRC影响:

LRC电路的Q值等于(L/C)^0.5/R因为而L较大,C与R很小,石英晶振的Q值可达几万到几百万。

Q值越大位于晶振的感性区间,电抗曲线陡峭,稳频性能极好。

FL特定负载电容以及激励功率下频偏越小越好

DLD2不同驱动功率下:

阻抗最大-阻抗最小越小越好影响:

导致时振时不振,造成睡眠晶体制造污染不良

DLD2(DriveLevelDependency2):

在不同的功率驅動Crystal時,所得之最大阻抗與最小阻抗之差。

DLD2越小越好,當Crystal製程受污染時,則DLD2值會偏高,導致時振與時不振現象,即(”CrystalSleeping”)。

好的Crystal不因驅動功率變化,而產生較高的阻抗差異,造成品質異常。

目前,許多水晶製造礙於製程管理控制及良率不佳,並不主動提供此重要指標參數給客戶。

备注:

测出来很好不代表此参数很好,因为是取点法测试的。

RLD2不同驱动功率下:

阻抗最大与DLD关系紧密

在指定的变化功率围所量测到的最大阻抗DriveLevelDependency

(maximumresistance–RR).

FDLD2不同驱动功率下:

F最大-F最小越小越好制造污染不良影响:

导致时振时不振,造成睡眠晶体

在不同的功率驅動Crystal時,所得之最大頻率與最小頻率之差,稱為FLD2。

FLD2越小越好。

當Crystal製程受污染,則FLD2值會偏高,導致時振與時不振現像,即「CrystalSleeping」。

好的Crystal不因驅動功率變化,而產生較高的頻率差異,造成品質異常。

SPDB寄生信号强度与主信号强度比值影响:

如果太大了就有可能造成直接启机频偏,并且修改负载电容不能改善。

或者烤机之后温度变化之后频偏,冷却或者重启又正常了。

绝对值越大越好制造污染不良

这个参数名字可以理解为SPDB其具体含义如下听我细细道来

SPDB(DifferenceindBbetweenAmplitudeofFRandHighestSpur):

Spurious以dB為單位時,SPDB的絕對值越大越好。

-3dB為最低的要求,以避免振盪出不想要的副波(Spur)頻率,造成系統頻率不正確。

“下图显示了石英谐振器的模态谱,包括基模,三阶泛音,5

阶泛音和一些乱真信号响应,即寄生模。

在振荡器应用上,振荡器总是选择最强的模式工作。

一些干扰模式有急剧升降的频率—温度特性。

有时候,当温度发生改变,在一定温度下,寄生模的频率与振荡频率一致,这导致了“活动性下降”。

在活动性下降时,寄生模的激励引起谐振器的额外能量的消耗,导致Q

值的减小,等效串联电阻增大及振荡器频率的改变。

当阻抗增加到相当大的时候,振荡器就会停止,即振荡器失效。

当温度改变远离活动性下降的温度时,振荡器又会重新工作。

寄生模能有适当的设计和封装方法控制。

不断修正电极与晶片的尺寸关系(即应用能陷原则),并保持晶片主平面平行,这样就能把寄生模最小化”

上面这段话看了是不是有点晕,说实话我也有点晕。

但是从上面我们可以总结出如下几个结论:

1.泛音晶振石英谐振器的模态谱,包括基模,三阶泛音,5

寄生模的存在。

2.在振荡器应用上,振荡器总是选择最强的模式工作。

寄生模会随温度频率变化,并且影响振荡。

3.寄生模的缺陷是由于晶振的制造工艺造成。

下来就很明确了,SPDB是一个衡量主频强度与寄生模强度差值的量(主频幅度/寄生频率取对数吧)。

这个值越小越好,代表寄生模越小。

TS负载电容变化对频率的影响率影响频偏对负载电容变化敏感造成电路不稳定越小越好

TS(TrimSensitivityofLoadMeasurement):

負載電容變化時,對晶體頻率變化量的影響,單位為ppm/pF。

影响:

此值過大時,很容易在不同的負載電容作用下,產生極大的頻率飄移。

温度频差制造工艺不合格会使曲线严重偏离超出图二阴影部分影响:

频率随温度变化

不同切割角度对曲线的影响

石英晶体结构

实例问题:

进入杂质或者有银屑、镀银偏了、镀银部裂痕

微调银镀偏

灰尘、银屑、晶片缺角