EDA设计报告 任亮Word文件下载.docx

《EDA设计报告 任亮Word文件下载.docx》由会员分享,可在线阅读,更多相关《EDA设计报告 任亮Word文件下载.docx(19页珍藏版)》请在冰豆网上搜索。

(3)、秒表清零功能:

clr为清零键,高电平时实现清零功能,低电平时正常计数。

可以在任意时刻进行清零。

由于时钟清零无意义,所以未设置时钟清零键。

(4)、闹钟功能:

手动设置闹钟时间,当时间和闹钟时间相同时,闹铃响即数码管显示1。

可以通过实验板上的键7、8、3、2和1进行任意的调整。

3按键为设置闹钟使能位,高电平时可设置闹钟时间,低电平时显示闹钟时间;

2按键为设置闹钟时间的位选键,1按键为设置的时间输入键。

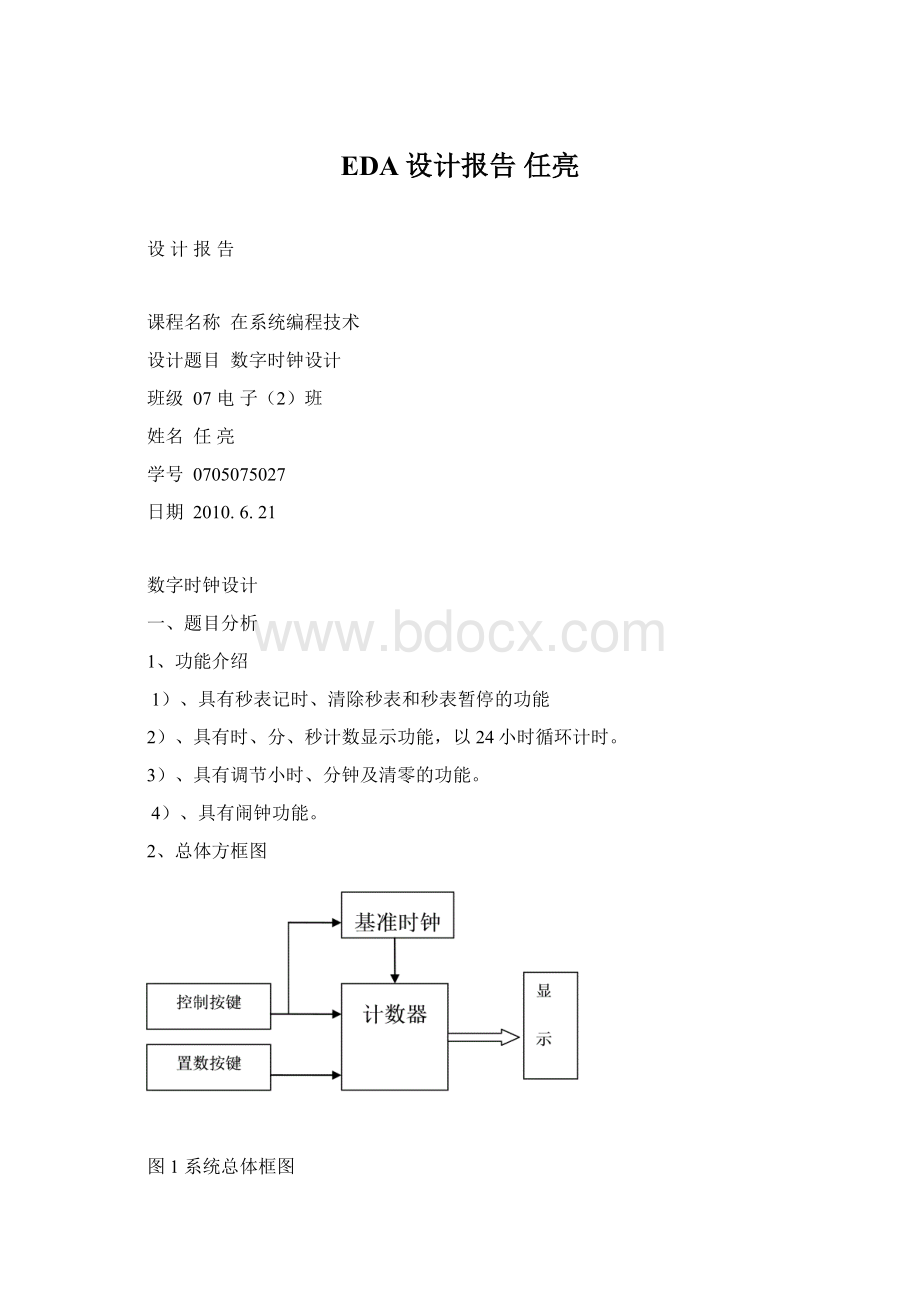

二、选择方案

1、系统分析

时钟由时、分、秒组成,分、秒都为60进制。

由于需要使用LED显示时间,

所以采用的计数器应该是10进制的,从而方便译码模块的通用。

而60进制计数器可以由10进制计数器和6进制计数器组成。

要组成一个可预置的60进制计数器,还需要一个6进制的计数器,使用10进制的进位作为6进制的计数器的时钟信号可以组成一个60进制的计数器。

时钟的小时是24进制的,所以必须设计一个24进制的可预置计数器。

显然,

24进制计数器不可以使用6进制计数器和4进制计数器组成,因为这样做的24进制计数器将给译码带来麻烦。

一共有7个LED需要显示,其中有一个是闹钟响的显示位,为1时表示闹钟响,为一时表示闹钟不响,所以需要7个译码模块。

2、方案选择

方案一:

根据上述分析和系统功能可知,本系统可以由时钟分频器、秒计数器、分钟计数器、小时计数器、分的调整以及小时的调整和闹铃功能构成。

采用自顶向下的设计方法,全部利用VHDL语言设计设计方法。

不易实现。

方案二:

根据上述分析和系统功能可知,本系统可以由时钟分频器、秒计数器、分钟计数器、小时计数器、分的调整以及小时的调整和一个顶层文件构成。

采用自顶向下的设计方法,子模块利用VHDL语言设计,顶层文件用原理图的设计方法。

显示:

小时采用24进制,而分钟和秒均60进制,毫秒用100进制。

综上所述,考虑到试验时的简单性,故我选择了方案二。

三、细化框图

本系统包含四个子模块和一个顶层文件,显示部分为六个时、分、秒的十位与个位的显示模块组成的,将送出的四位二进制通过译码器显示。

图2系统细化框

(1)秒表模块time。

秒表模块中的毫秒模块是一个10000分频的计数器和两个10进制计数器组成,秒模块是由一个十进制和一个6进制计数器组成。

分时由一个十进制和一个6进制计数器组成。

在ENA端为1的情况下,输入30MK的时钟信号作为计数脉冲,分别输出位的四位BCD码。

(2)时钟显示模块shi。

时钟显示模块是在秒表模块的基础上做成的,毫秒位不显示,加一个24进制的小时位。

同时加一个设置时钟的使能位tiao,当其为高电平时为调时。

图3时钟模块的内部结构图

(3)译码器模块mux21。

由于试验箱上的按键有限,所以设置了译码器模块。

当b口输入1时,选通a[3..0],b口输入为2时选通b[3..0],b口输入3时选通c[3..0],b口输入4时选通d[3..0]。

图4译码模块内部结构图

(4)3选1模块mux14

当s、s1为00时选通秒表通道a[23..0],当s、s1为10时选通时钟通道b[23..0],当s、s1为01时选通闹钟通道c[23..0],

图53选1模块内部结果图

(5)锁存模块mux41

当c为高电平时,将a[3..0]、b[3..0]、c[3..0]和d[3..0]中的数据锁存在mux41中

图6锁存模块内部结果图

(6)下图为顶层实体原理图:

图7顶层实体原理图

图2顶层实体原理图

四、全局联调

由于本系统采用3MHZ的时钟信号,如果要产生1/100秒,需要29999个时钟脉冲,如果在仿真时给周期为1ns的时钟则299.99us时才能产生一个进位。

所以在仿真时只仿真了他的毫秒位。

他的仿真结果如下图所示:

图8系统仿真波形图

五、硬件测试

本实验的硬件实现是基于Cyclone电子实验仪,使用模式0接口说明如下:

使用模式8,键7为通道选择按键按键,为00时选通秒表通道,为10时选通时钟通道,为01时选通闹钟通道;

按键6为清零按键;

按键5为使能按键只有其为高电平时,此数字秒表数字时钟才能工作;

按键4为设置时钟的使能按键,当其为高电平,设置时钟;

按键3为设置闹钟使能端,当其为高电平时,设置闹钟时间;

按键2为设置时钟时间和闹钟时间的位选按键;

按键1为设置的时间输入端;

clk接3MHZ的时钟信号。

图9引脚锁定

本次设计的VHDL语言程序在QUARTUSⅡ工具软件上进行了编译、仿真和调试,并通过编程器下载到了Cyclone芯片上。

经过实践验证,本设计是正确的,仿真数据与实际波形发生器的试验箱运行结果完全一致,达到预期目的,设计成功。

六、设计总结

经过这一次的设计,使我进一步认识到了VHDL语言和图形输入法在系统设计中所起到的重要做用,同时也加深了我对VHDL语言和图形输入法的了解和认识。

在平时学习过程中我们大多数时间都是在理论课的教学中进行问题研究和论证的,很少有机会像实习这样用到QUARTUSⅡ工具软件以及为其而专门设计的实验箱,进行仿真、编译、下载等一系列实践工作,而这次实习使我进一步掌握了QUARTUSⅡ工具软件在使用过程中应该注意的问题和使用方法。

在EDA设计时可以单独使用VHDL语言进行设计、单独使用图形输入法进行设计,也可以将这两种方法结合起来进行设计。

这大大增加了设计的灵活性。

比如在本次设计中就使用了两者结合的设计方法。

先用VHDL语言描述出一个一个单模块,然后用VHDL语言的顶层文件的方法将一部分单模块组合成一些简单的功能模块,而后再用图形输入法将简单的的功能模块组合成功能复杂的功能模块(器件)。

用EDA进行设计,摆脱了硬件固定功能的束缚,可以根据设计者的需求自行设计出满足自己要求的功能模块,从而实现设计者的需求。

同时方便产品后期的升级。

在设计的过程中会出现许多错误,在每次发现错误和改错误中都是一次提高,学习就是由未知到知道的过程。

在解决这些问题的同时我也学到了许多在理论课上无法学到的知识,出现错误并解决错误这才是最宝贵的。

因为这次设计,使我学到了许多,他对我后期的学习和工作都将有着重要的意义。

七、参考文献

【1】《CPLD/FPGA常用模块与综合系统设计实例精讲》罗苑棠—北京:

电子工业出版社,2007.11

【2】《EDA技术实用教程》—3版潘松,黄继业—北京:

科学出版社,2006.9

八、附录

源程序:

1、产生1/100秒c_clck

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYc_clckIS

PORT(CLK:

INSTD_LOGIC;

--3MHz信号输入

NEWCLK:

OUTSTD_LOGIC);

--100Hz计时时钟信号输出

ENDENTITYc_clck;

ARCHITECTUREARTOFc_clckIS

SIGNALCNTER:

INTEGERRANGE0TO10#29999#;

--十进制计数预制数

BEGIN

p1:

PROCESS(CLK)--分频计数器,由3MHz时钟产生100Hz信号

BEGIN

IFCLK'

EVENTANDCLK='

1'

THEN

IFCNTER=10#29999#THENCNTER<

=0;

--3MHz信号变为100Hz,计数常数为15000

ELSECNTER<

=CNTER+1;

ENDIF;

ENDIF;

ENDPROCESSp1;

P2:

PROCESS(CNTER)IS--计数溢出信号控制

BEGIN

IFCNTER=10#29999#THENNEWCLK<

='

;

ELSENEWCLK<

0'

ENDPROCESSP2;

ENDARCHITECTUREART;

2、十进制模块cn10

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcn10IS

PORT(CLK:

CLR:

ENA:

tiao:

INSTD_LOGIC;

she:

INSTD_LOGIC_VECTOR(3DOWNTO0);

CQ:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

CARRY_OUT:

OUTSTD_LOGIC);

ENDENTITYcn10;

ARCHITECTUREARTOFcn10IS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

p3:

PROCESS(CLK,CLR,ENA,CQI)

BEGIN

IFtiao='

THENCQI<

=she;

ELSIFCLR='

="

0000"

--清零

ELSIFCLK'

IFENA='

IFCQI="

1001"

--到十时清零

ELSECQI<

=CQI+'

--未到十时加1

ENDIF;

ENDPROCESSp3;

p4:

PROCESS(CQI)IS

THENCARRY_OUT<

--如果有进位位出1

ELSECARRY_OUT<

--无进位位出0

ENDPROCESSp4;

CQ<

=CQI;

3、六进制模块cn6

ENTITYcn6IS

ENDENTITYcn6;

ARCHITECTUREARTOFcn6IS

SIGNALCUN:

STD_LOGIC;

PROCESS(CLK,CLR,CQI,ENA)

IFtiao='

--调时使能位

ELSIFCLR='

--清零位

ELSIFCLK'

IFENA='

IFCQI="

0101"

--十进制

ELSECQI<

--未到十加1

ENDIF;

--ENDIF;

ENDPROCESSp3;

IFCQI="

--到十向前一位进1

ELSECARRY_OUT<

--未到十不向前一位进1

CQ<

ENDARCHITECTUREART;

4、24进制模块cn2

ENTITYcn2IS

INSTD_LOGIC_VECTOR(7DOWNTO0);

OUTSTD_LOGIC_VECTOR(7DOWNTO0);

ENDENTITYcn2;

ARCHITECTUREARTOFcn2IS

STD_LOGIC_VECTOR(7DOWNTO0);

PROCESS(CLK,CLR,CQI,ENA)

IFCQI(3DOWNTO0)="

THEN--到十向前进一位

CQI(3DOWNTO0)<

CQI(7DOWNTO4)<

=CQI(7DOWNTO4)+1;

ELSE

CQI(3DOWNTO0)<

=CQI(3DOWNTO0)+1;

--未到十不向前进位

IFCQI="

00100011"

THEN--到二十四清零

CQI<

00000000"

5、秒表模块time

ENTITYtimeIS

PORT(CLR:

CLK:

ENA:

DOUT:

OUTSTD_LOGIC_VECTOR(23DOWNTO0));

ENDENTITYtime;

ARCHITECTUREARTOFtimeIS

COMPONENTc_clckIS

PORT(CLK:

ENDCOMPONENTc_clck;

COMPONENTcn10IS

PORT(CLK,CLR,ENA:

ENDCOMPONENTcn10;

COMPONENTcn6IS

PORT(CLK,CLR,ENA:

ENDCOMPONENTcn6;

SIGNALS0:

STD_LOGIC;

SIGNALS1,S2,S3,S4,S5,S6:

U0:

c_clckPORTMAP(CLK=>

CLK,NEWCLK=>

S0);

U1:

cn10PORTMAP(CLK=>

S0,CLR=>

CLR,ENA=>

ENA,CQ=>

DOUT(3DOWNTO0),CARRY_OUT=>

S1);

U2:

S1,CLR=>

CLR,ENA=>

DOUT(7DOWNTO4),CARRY_OUT=>

S2);

U3:

S2,CLR=>

DOUT(11DOWNTO8),CARRY_OUT=>

S3);

U4:

cn6PORTMAP(CLK=>

S3,CLR=>

DOUT(15DOWNTO12),CARRY_OUT=>

S4);

U5:

S4,CLR=>

DOUT(19DOWNTO16),CARRY_OUT=>

S5);

U6:

S5,CLR=>

DOUT(23DOWNTO20));

6、时钟模块shi

ENTITYshiIS

tiao:

she2:

INSTD_LOGIC_VECTOR(15DOWNTO0);

she11:

she12:

INSTD_LOGIC_VECTOR(7DOWNTO4);

she13:

INSTD_LOGIC_VECTOR(11DOWNTO8);

she14:

INSTD_LOGIC_VECTOR(15DOWNTO12);

ENDENTITYshi;

ARCHITECTUREARTOFshiIS

INSTD_LOGIC_VECTOR(3DOWNTO0);

COMPONENTcn2IS

ENDCOMPONENTcn2;

S0,CLR=>

CLR,tiao=>

tiao,she=>

she2(3DOWNTO0),ENA=>

ENA,CARRY_OUT=>

she2(7DOWNTO4),ENA=>

S2,CLR=>

she2(11DOWNTO8),ENA=>

she2(15DOWNTO12),ENA=>

S4,CLR=>

she11(3DOWNTO0),ENA=>

DOUT(11DOWNTO8