通信电子线路锁相环项目设计终期报告Word下载.docx

《通信电子线路锁相环项目设计终期报告Word下载.docx》由会员分享,可在线阅读,更多相关《通信电子线路锁相环项目设计终期报告Word下载.docx(16页珍藏版)》请在冰豆网上搜索。

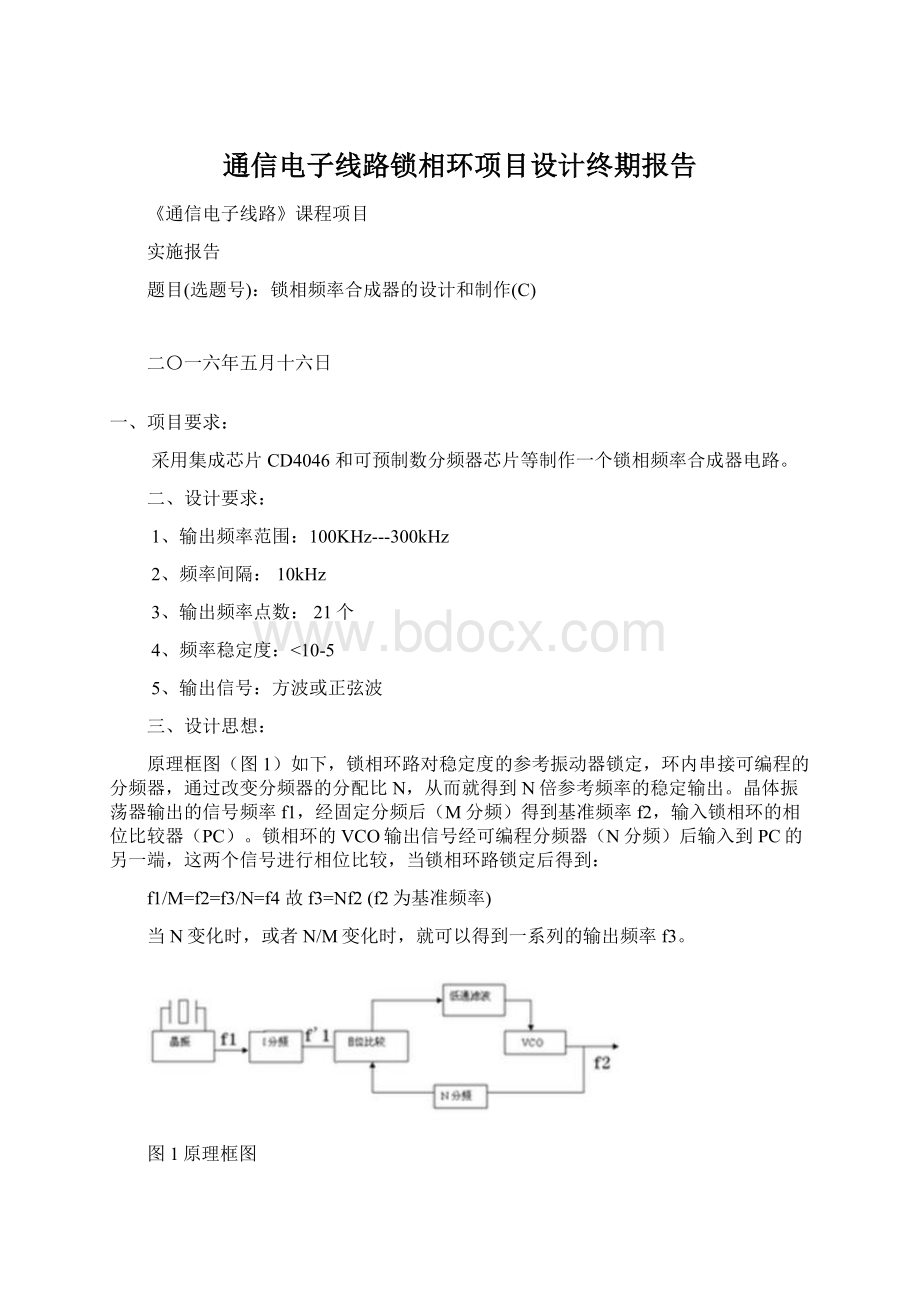

三、设计思想:

原理框图(图1)如下,锁相环路对稳定度的参考振动器锁定,环内串接可编程的分频器,通过改变分频器的分配比N,从而就得到N倍参考频率的稳定输出。

晶体振荡器输出的信号频率f1,经固定分频后(M分频)得到基准频率f2,输入锁相环的相位比较器(PC)。

锁相环的VCO输出信号经可编程分频器(N分频)后输入到PC的另一端,这两个信号进行相位比较,当锁相环路锁定后得到:

f1/M=f2=f3/N=f4故f3=Nf2(f2为基准频率)

当N变化时,或者N/M变化时,就可以得到一系列的输出频率f3。

图1原理框图

(一)、标准信号源的设计

方法一:

采用无源晶振起振

CD4049引脚图>

:

<

信号源发生器电路图>

采用CMOSCD4049:

六反相缓冲器转换器和1M晶振以及电容电阻组成1MHz振荡器。

工作原理:

1M晶振等效为电感,与C1,C2组成电容三点式振荡电路;

非门和R1实现一个NPN的三极管。

5404非门必需要一个电阻,不然它处于饱和截止区,而不是放大区,R1相当于三极管的偏置作用,让5404处于放大区域,那么5404就是一个反相器,这个就实现了NPN三极管的作用,NPN三极管在共发射极接法时也是一个反相器。

如下图所示:

一个正弦振荡电路要振荡的条件,起振系统放大倍数大于1,这个容易实现,相位满足2nπ,与晶振振荡频率相同的很小的振荡就被放大了。

接下来主要讲解这个相位问题:

5404因为是反相器,也就是说实现了180°

移相,那么就需要C1,C2和Y1实现180°

移相就可以,而当C1,C2,Y1形成谐振时,能够实现180移相。

方法二:

直接采用有源晶振起振

无源晶振是有2个引脚的无极性元件,需要借助于时钟电路才能产生振荡信号,自身无法振荡起来,所以“无源晶振”这个说法并不准确;

有源晶振有4只引脚,是一个完整的振荡器,其中除了石英晶体外,还有晶体管和阻容元件,因此体积较大。

有源晶振实物图>

有源晶振引脚图>

注:

有个点标记的为1脚,按逆时针(管脚向下)分别为2、3、4。

有源晶振通常的用法:

一脚悬空,二脚接地,三脚接输出,四脚接电压。

(二)、M分频的设计

CD4518引脚图>

:

实验原理图>

本次课程设计采用的是1M的晶振,最终需要的是10KHZ的标准信号,因此中间需要设计个100分频的分频器,即M=100.

CD4518是一个双BCD同步加计数器,由两个相同的同步4级计数器组成。

CD4518引脚功能(如上图):

1CP、2CP:

时钟输入端。

1CR、2CR:

清除端。

1EN、2EN:

计数允许控制端。

1Q1~1Q4:

计数器输出端。

2Q1~2Q4:

Vdd:

正电源。

Vss:

地。

该CD4518计数器是单路系列脉冲输入(1脚或2脚;

9脚或10脚),4路BCD码信号输出(3脚~6脚;

{11}脚~{14}脚)。

CD4518控制功能:

CD4518有两个时钟输入端CP和EN,若用时钟上升沿触发,信号由CP输入,此时EN端为高电平

(1),若用时钟下降沿触发,信号由EN输入,此时CP端为低吨平(0),同时复位端Reset也保持低电平(0),只有满足了这些条件时,电路才会处于计数状态.否则没办法工作。

每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。

CD4518工作方式:

采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;

当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;

当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;

当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。

这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态。

分析实验原理图:

按上图所连接,因为1MHZ从CP端输入,reset1脚接地,EN=0,则1QA~4QA采用的是上升沿触发的;

因为2CP接地,reset2脚接地,EN2接1Q4,则1QB~4QB采用的是下升沿触发的:

Q时钟脉冲

Q4

Q3

Q2

Q1

1

2

1

3

4

5

6

7

8

9

10

11

分析可知,1Mhz的信号由CP1接入,1QA~4QA进行着周期为T=10Tcp的循环加法计数,Q4A由CP2接入,每T=10Tcp有一个下降沿,1QB~4QB进行着周期为10T的循环加法计数,计数规律如上图所示。

这样就可把1MHz的晶振信号变成10KHz的标准信号。

所得波形:

(三)、N分频的设计

根据本次项目的要求,需设计一个N=10-30的分频计。

CD4522引脚图>

单个设计原理图>

CD4522是可预置BCD同步1/N减计数器。

其引脚见上图。

其中ABCD是预置端,Q0—Q3是计数器输出端,其余控制端的功能如下:

一旦PE(3)=1时,A/B/C/D值置进计数器;

当使能端(4)=0时,且CLK(6)上升沿触发时,计数器(Q0—Q3)减1计数;

CF(13)=1且计数器(Q0—Q3)减到0时,QC(12)=1;

若Cr(10)=1时,计数器清零。

如上右图为单片4522分频器,拨盘开关为BCD码开关。

4个100K电阻用来保证当拨盘开关为某脚不和A相连,也就是悬空时,为低电平。

工作过程是这样的:

设拨盘开关拨到N,当某时刻PE(3)=1,则N置到IC内的计数器中,下一个CP来时,计数器减计数变为N-1,……,一直到第N个CP来时,计数器为0。

这时由于CF(13)=1,所以QC(12)=1,也即PE(3)=1又恢复到开始状态,开始一个新的循环。

很显然,每来N个CP,QC(12)就会出现一个高电平,也就是QC(12)应是CP的N分频信号。

用两片4522组成可变分频器,最大分频可达到99倍,满足N=10~30的要求。

下图为本实验的设计图:

左边CD4522作为N分频的十位,右边CD4522作为N分频的个位,个位CP(6)接压控振荡器VCO的输出f3,个位的12脚作为输出f4=f3/N;

假设置数N为=15(BCD码为00010101),则

f3↑时钟脉冲

十位Q3

十位Q2

十位Q1

十位Q0

个位Q3

个位Q2

个位Q1

个位Q0

特殊位变化

十位CLK(6)↑;

个位CF(13)=1

12

13

14

(15)

瞬间态

个位十位PE(3)=1

15

置数

(四)、锁相环的设计

CD4046引脚图>

本实验原理图>

如图是CD4046内部电原理框图,主要由相位比较Ⅰ、Ⅱ、压控振荡器(VCO)、线性放大器、源跟随器、整形电路等部分构成。

比较器Ⅰ采用异或门结构,当两个输人端信号Ui、Uo的电平状态相异时(即一个高电平,一个为低电平),输出端信号UΨ为高电平;

反之,Ui、Uo电平状态相同时(即两个均为高,或均为低电平),UΨ输出为低电平。

当Ui、Uo的相位差Δφ在0°

-180°

范围内变化时,UΨ的脉冲宽度m亦随之改变,即占空比亦在改变。

从比较器Ⅰ的输入和输出信号的波形(如图3-6所示)可知,其输出信号的频率等于输入信号频率的两倍,并且与两个输入信号之间的中心频率保持90°

相移。

从图中还可知,fout不一定是对称波形。

对相位比较器Ⅰ,它要求Ui、Uo的占空比均为50%(即方波),这样才能使锁定范围为最大。

CD4046内部框图

图3-6输入输出波形

相位比较器Ⅱ是一个由信号的上升沿控制的数字存储网络。

它对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。

它提供数字误差信号和锁定信号(相位脉冲)两种输出,当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°

对相位比较器Ⅱ而言,当14脚的输入信号比3脚的比较信号频率低时,输出为逻辑“0”;

反之则输出逻辑“1”。

如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。

在这两种情况下,从1脚都有与上述正、负脉冲宽度相同的负脉冲产生。

从相位比较器Ⅱ输出的正、负脉冲的宽度均等于两个输入脉冲上升沿之间的相位差。

而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态,则1脚输出高电平。

上述波形如图5所示。

由此可见,从1脚输出信号是负脉冲还是固定高电平就可以判断两个输入信号的情况了

CD4046锁相环采用的是RC型压控振荡器,必须外接电容C1和电阻R1作为充放电元件。

当PLL对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2。

由于VCO是一个电流控制振荡器,对定时电容C1的充电电流与从9脚输入的控制电压成正比,使VCO的振荡频率亦正比于该控制电压。

当VCO控制电压为0时,其输出频率最低;

当输入控制电压等于电源电压VDD时,输出频率则线性地增大到最高输出频率。

VCO振荡频率的范围由R1、R2和C1决定。

由于它的充电和放电都由同一个电容C1完成,故它的输出波形是对称方波。

压控振荡器的输出波形是50%的方波。

一般规定CD4046的最高频率为1.2MHz(VDD=15V),若VDD<

15V,则fmax要降低一些。

CD4046内部还有线性放大器和整形电路,可将14脚输入的100mV左右的微弱输入信号变成方波或脉冲信号送至两相位比较器。

源跟踪器是增益为1的放大器,VCO的输出电压经源跟踪器至10脚作FM解调用。

齐纳二极管可单独使用,其稳压值为5V,若与TTL电路匹配时,可用作辅助电源。

所以我们这次的CD4046工作原理如下:

输入信号Ui从14脚输入后,经放大器A1进行放大、整形后加到相位比较器Ⅰ、Ⅱ的输入端,开关K拨至2脚,则比较器Ⅰ将从3脚输入的比较信号Uo与输入信号Ui作相位比较,从相位比较器输出的误差电压UΨ则反映出两者的相位差。

UΨ经R3、R4及C2滤波后得到一控制电压Ud加至压控振荡器VCO的输入端9脚,调整VCO的振荡频率f3,使f3迅速逼近信号频率f2。

VCO的输出又经除法器f4=f3/N再进入相位比较器Ⅰ,继续与Ui进行相位比较,最后使得f2=f4,两者的相位差为一定值,实现了相位锁定。

最后当N=20时,波形图为:

N=30时,波形图为:

(5)、锁相频率合成器电路图

四、实验过程中遇到的问题以及解决方法

在这次的锁相环制作中,我们通过各个元器件分开组合调试,第一个振荡器调试结果成功产生1MHz的方波,经过100分频出现10KHz的方波。

我们直接用信号源接N分频部分,但是经过N分频无论如何都产生300KHz的方波,于是我们首先怀疑芯片坏了,去换了新的芯片,但是还是没有成功于是我们决定单独测试N分频,我们再次直接接信号发生器至分频器,发现并不能按照预想要求产生分频。

但是当我们增大信号峰峰值到5伏以上时,发现可以产生分频了。

于是我们将信号源调至6VPP发现N分频部分工作正常了。

我们将振荡源接入电路,上电调试,发现调至24KHZ以上之后频率不变了,我想可能是4046的参数设置不当,锁相环无法实现锁定工作。

于是我们重新计算工作参数,重置电容和电阻值,更换器件之后,再次调试,发现终于可以正常工作了。

五、组员分工

六、心得体会

通过本次实验,使自己对锁相环的工作原理及其应用有了较深的理解,锁相环应用愈广,锁相环是在无线电发射中使频率较为稳定的一种方法。

例如为相干解调提取参考载波、建立位同步等,也可以用于改善电视接收机的行同步和帧同步,以提高抗干扰能力。

很重要的一点是,通过实验提高了发现问题,运用理论知识解决实际问题的能力。

通过调试来发现自己的错误并分析及排除这些故障,结合自己在实验过程中碰到的问题,我觉得在调试过程中应该注意以下几点:

1、调试时应该分模块进行调试,每个模块都测试成功之后再测试整体,这样可以更好的检查出问题所在。

就比如这次实验,刚开始时,晶振不起振,这时我就用函发直接输入一个1MHz的频率作为频率源,检测M分频的输出是否正常,同样的做法来判断N分频是否正常。

2、要学会从检测结果中分析出是那些出来问题。

比如在检测M分频过程中,发现第二片的4518输入为10KHz,但是输出没有信号,由此可以看出问题出在第二片的4518,我先检查了这块芯片的连线图是否正确,发现没有错误,可能是芯片出了问题,更换芯片后发现M分频正常工作,输出为1KHz