北邮计算机系统结构实验报告实验一到五WINDLX模拟器Word文件下载.docx

《北邮计算机系统结构实验报告实验一到五WINDLX模拟器Word文件下载.docx》由会员分享,可在线阅读,更多相关《北邮计算机系统结构实验报告实验一到五WINDLX模拟器Word文件下载.docx(41页珍藏版)》请在冰豆网上搜索。

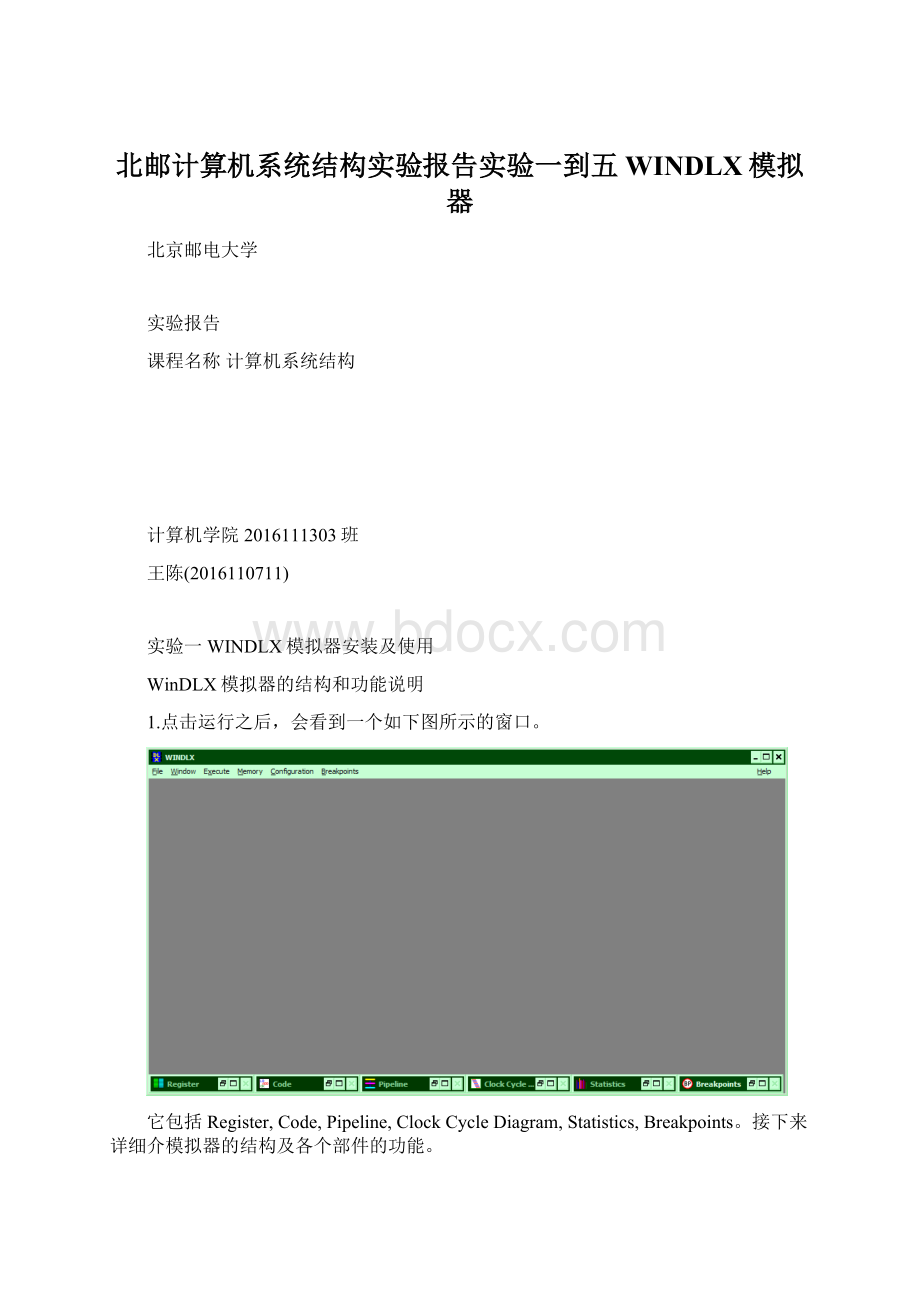

窗口用下图标识DLX五段流水。

当然,如同Code窗口介绍讲述的那样,不同的颜色显示了指令处于哪段流水线。

使用快捷键F7单步执行,可以明显的看出,不同时候流水段执行的不同指令。

如下图。

图片反映的正式与Code中所处的时刻相同的指令流水。

可以清晰看到不同流水段执行的是哪条指令。

4.ClockCycleDiagram窗口

实验准备中我们已经知道,该窗口显示的是流水线的时空图。

时空图反映的是不同时隙内的运行情况。

在我看来,时空图是最好理解的。

因为它反映的就是流水段的并行程度。

在这个DLX模拟器中,并不存在一些数据或者控制上的冲突问题。

所以可以依靠上图很清晰的看到指令所处的不同流水段,及指令执行情况。

该时空图同样也是和前面的Code等相对应。

也可以通过快捷键F7来进一步执行指令,可以看到流水线时空图的扩展情况。

任意双击指令的一行,可以详细看到不同流水段的情况。

如下图所示。

5.Statistics窗口介绍

该窗口是对运行程序中的数据进行分析。

主要包括模拟器中硬件配置情况,在该窗口中,我们可以比较不同配置对于该模拟器的不同影响。

1)整体指令执行情况

2)硬件配置情况

3)暂停次数和百分比及原因分析

4)分支次数和百分比

5)Load/Store指令执行情况

6)浮点指令执行次数和百分比

7)trap发生的次数和百分比

6.Breakpoints窗口介绍

该窗口使用来观察代码运行情况。

先打开Breakpoints窗口,点击窗口上方的

来设置breakpoint,也就是设置指令运行到流水线的哪个阶段程勋停止执行。

如上图,如果选择EX阶段,在Code窗口中相应的行会出现BEX,即指令执行到译码结束执行开始的时候,程序将中止。

·

实验总结

通过本次试验,由于是第一次接触DLX模拟器,该试验能够帮助我对这个模拟器大致的功能及使用做个大致的了解。

对于日后的实验打下好的基础。

我觉得WinDLX模拟器小而精悍,它有不同颜色的标记,不同寄存器及存储器的反映。

通过使用它,可以对5步流水的过程及不同阶段很清楚明白的看到。

也可以看到不同指令分析走到了哪一步,到了哪一步流水段。

实验二指令流水线相关性分析

实验目的

通过使用WINDLX模拟器,对程序中的三种相关现象进行观察,并对使用专用通路,增加运算部件等技术对性能的影响进行考察,加深对流水线和RISC处理器的特点的理解。

实验环境

WindowsXP操作系统

WinDLX模拟器

实验步骤

1.观察程序中出现的数据/控制/结构相关。

指出程序中出现上述现象的指令组合。

2.考察增加浮点运算部件对性能的影响。

3.考察增加forward部件对性能的影响。

4.观察转移指令在转移成功和转移不成功时候的流水线开销。

1.观察程序中出现的数据/控制/结构相关;

1)数据相关

如下图所示,在ClockCycleDiagram窗口所想是的时空图中和Pipeline窗口中的流图中,第一次出现了R-Stall。

接下来可以点击上图中的橘色窗口,则屏幕显示

lbur3,0×

0(r2)

要在WB周期写回r3中的数据;

而下一条指令

seqir5,r3,0×

a

要在intEX周期中读取r3中的数据。

上述过程发生了WR冲突,即写读相关。

为了避免此类冲突,

seqr5,r4,0×

a的intEX指令延迟了一个周期进行。

由此,相关指令为:

2)控制相关

由上图可以看出,在第4时钟周期:

第一条指令处于MEM段;

第二条命令处于intEX段;

第三条指令出于aborted状态;

第四条命令处于IF段。

原因分析:

jalInputUnsigned是无条件分支指令,但当第三个周期开始的时候,也就是jal这条指令被译码后才知道。

此时,movi2fp已经执行,且将要执行的下一条命令在另外一个地址处,所以这条指令不会执行,这个时候就会发生控制相关。

由此,发生控制相关的指令为:

3)结构相关

首先,我们先来看一下执行过控制相关的时空图和Pipeline,如下图。

当我们点击Pipeline中IF所对应的框框可以看到详细的该指令执行情况,如下图:

上图表明了addir2,r2,0×

1的详细信息。

该指令与它前一条指令addr1,r1,r3发生了结构相关。

并且由于此处的冲突,需要暂停2个周期。

在ID段暂停后,则开始进图intEX段。

所以这条指令(addir2,r2,0×

1)你不能进入ID流水段,译码部分占用,发生了结构相关。

该部分的指令为:

2.考察增加浮点运算部件对性能的影响。

该实验取N=6

首先通过

,点击FloatingPointStageConfiguration来设置浮点运算部件的配置。

由于实验手册上面要求Delay=4,所以我们将Delay这一栏改成4,而Count可以任意,为了对比,我们第一次浮点运算部件取全部为2,第二次浮点运算部件取全部为3。

如下图所示:

运行50个cycles之后,可以看到他们数据的对比:

由此可见,浮点运算部件的增减对效率无影响。

比较各个数据,发现没有变化。

无论怎么增加浮点运算部件,统计结果都一样。

原因在于此程序中浮点计算指令没有重叠,所以并行度没有增加,性能没有提高。

为了对比有无forward部件的性能。

需要在

中勾选enableforwarding,以及不勾选enableconfiguration来看性能数据的对比。

不使用forward部件:

使用forward部件:

从上面的数据我们可以看出增加forwardi部件后RAW由原来占总时钟周期的26%减少至18%,RAW个数由原来的13减少至9。

增加forward部件使得控制相关比例增加了。

即,使用forward部件后,总的时钟周期减少,数据相关减少,流水线的性能得到一定的改善。

3.观察转移指令在转移成功和转移不成功时候的流水线开销。

我们假设,浮点部件设置Count=3,Delay=4;

N=6。

执行完毕后,查看条件转移分支,如下图所示:

由上图可知,转移指令一共8条,成功转移2条(占25%),不成功为6条。

所以,静态指令调度算法只能解决数据相关,条件转移结果与原来相比没有变化。

即,若转移不成功,对流水线的执行无影响,流水线的吞吐率和效率没有降低;

若转移成功,则要废弃预先读入的指令,重新从转移成功处读入指令,执行效率会下降。

本次试验中,主要遇见一个问题,就是在当初文件加载时没有成功,后来通过查询资料和自己的尝试,发现,在选择文件的顺序很关键,它决定了文件在存储器中出现的顺序。

本次实验,主要通过对于三中相关的观察,分析出现相关时的指令,分析浮点运算部件和forward部件对性能的影响,观察转移指令在转移成功和不成功时的流水线开销,这些实验一步一步,通过WinDLX形象生动的表示,使我在实践中更加深入的认识了流水线。

实验三DLX处理器程序设计

学习使用DLX汇编语言编程,进一步分析相关现象

实验过程

A.向量加法代码及性能分析

首先给据题目要求,需要熟练掌握DLX编程语言,然后根据规范格式编写向量的代码。

1)向量声明

VectorLength:

.word

16

//声明向量长度

Vector1:

1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16

//声明两个向量

Vector1和Vector2

Vector2:

Result:

.space

4

//声明一个空间来存放打印的数据

Loop:

//循环体

ld

f10,Vector1(r2)

f12,Vector2(r2)

//读入两个提前声明的向量

add

f4,f2,f0//加法运算

trap

5

//系统中断

2)源代码

运行结果分析

当运行到如下图所示的时候,则表示运行结束。

运行结果为

接下来我们可以查看Statistics可以看到运行结果的数据显示,如下图所示。

1)程序相关性分析结果

数据相关

由上图的

可以看出,该程序产生了11.31%的数据相关。

所以当对当前指令的操作数寄存器进行操作(EX)的时候,前几条指令的运算结

果还未写回(WB)结果寄存器,由此产生数据相关。

结构相关

由于程序只简单的做了一次加法,所以没有结构相关产生。

控制相关

查看pipeline中可以看到,当执行到如下情况时,发生了控制相关。

由Statistics中的

可以看出,其控制相关发生了5.3%。

分析可知,由于系统按照预测成功来执行指令,所以执行bnez后马上将其下一条指令trap

读进来。

2)浮点运算部件带来的影响

当我们通过设置浮点部件的个数,并将程序运行完毕,查看Statistics中的数据作对比。

将浮点加法器由1个增加为4个后(左图为4个),可以由上图看出,程序执行的性能未得到提升。

分析原因我们知道,由于该程序为产生浮点加法器的结构相关,所以增加浮点加法器的数量对程序执行的性能提升没有帮助。

3)forward部件的影响

由上图的对比可以看到,当不勾选enableforwarding时,运行时间由283增加到381。

所以forwarding技术为该程序带来的加速比为

381/282=1.35

4)转移成功和不成功

查看statistics中的ConditionalBranches选项,两者的下述相同,如下图所示。

可以发现,由于系统按照预测成功来执行指令,所以执行

bnez后马上将其下一条指令trap读进来判断出是转移不成功时,系统对trap指令进行的操作被全部作废,转而去执行跳转到的指令id。

B.双精度浮点加法求和代码及结果分析

按照题目要求,自行又编写了一套程序来实现双精度浮点加法求和

结果分析

当运行到如下图所示时,运行结束,可以看到运行结果如下图所示。

产看Statistics可以看到具体数据情况和产生相关的比例等。

1)程序中出现的数据/控制/结构相关

控制相关:

知道,发生了55.48%的数据相关。

产看代码可以发现,产生的相关都为RW读写相关。

它们分别为:

addi

r1,r0,0

subi

r2,r1,20

beqz

r2,finish

multu

r3,r1,r4

f0,a(r3)

f2,b(r3)

addd

f4,f0,f2

sd

r(r3),f4

可以看到,发生了4.43%的控制相关。

系统按照预测成功来执行指令,执行一条指令后马上将其下一条指令trap读进来。

2)增加浮点运算部件对性能的影响。

下图分别为浮点运算部件为1和4的时候数据情况对比。

由上图的对比可知,当浮点运算部件个数给边后统计结果均相同,也就是其数量对该函数没有任何性能方面的改进。

分期其原因为,这主要是因为函数中没有连续的浮点加指令,乘、

除指令。

3)增加forward部件对性能的影响。

下图左侧为没有勾选enableforwarding时的运行数据结果,右侧为使用了forwarding技术。

由上图的对比可以看出,增加forwarding技术后,流水线的加速比为:

474/352=1.347

流水线性能有明显改善。

4)转移指令在转移成功和转移不成功时候的流水线开销。

由ConditionalBranches的数据可以看出,该转移指令“not

taken”的情况占绝大多数(95.24%)。

在一共的21中,发生了仅为1次,所以预测顺序取对流水线的性能是有利的。

转移不成功时:

顺序预取的下条指令可以直接在流水线中执行,保证流水线不断流;

转移成功时:

顺序预取的下条指令作废,需要转到转移地址处重新取指,流水线发生了断流现象。

在实验中,我主要遇到的问题是WinDLX所加载的.s文件不要出现中文格式,不然会导致加载失败(开始好几次为了方便我直接起名为“双精度浮点向量加.s”却怎么样也导入不成功);

在编写双精度浮点数运算时有些对于指令掌握不熟练,并且双精度double型运算指令,其所有的运算指令名称上面都要加上“d”才ok。

而如果是单精度的,则需要添加字母“f”;

其次,对于浮点数的相关设置,包括状态寄存器和浮点寄存器都需要在实验之前查资料了解透彻,不然在试验中就会有语法错误。

通过此次实验我对实验二所进行的数据相关、控制相关、结构相关的性能分析做了更深入的了解,以及对于功能部件对流水线的影响,forwarding技术对流水线的影响,还有就是静态指令调度等。

通过自行编写向量矢量算法,在代码中初始化两个向量,按照分量顺序进行运算。

当然,如果想要改变源向量,直接处理代码中的相关数据即可。

总之,该实验主要着重对浮点运算以及对于流水线的相关影响及性能分析,使我受益匪浅。

实验四代码优化

学习简单编译优化方法,观察采用编译优化方法所带来的性能的提高。

实验原理

采用静态调度方法重排指令序列,减少相关,优化程序

选择上一个实验的向量加法运算作为优化对象。

优化后的代码如下图所示。

当如下图所示的时候证明已经执行完毕。

执行完毕后,我们点击Statistics查看运行结果数据分析。

1)程序相关性分析结果

优化之后其中断数据显示为:

优化前为:

由上述两图对比可以看出,

数据相关:

其RAW相关由优化前的34.12%减少为20.57%,性能改善很多;

结构相关没有发生改变;

由原来的3.94%变为4.75%,没有改善。

因此,可以看出,我所进行的代码优化对性能方面改善并不是很强烈,主要影响还是在数据相关方面。

上图左图为4个浮点部件执行结果,右图为原始默认1个浮点部件执行结果。

由此可以看出,其部件个数对统计结果并无影响。

原因为该运算过程中不存在结构相关,因此并行度没有增加,程序影响不大,部件增加对于系统的性能并没有改善。

左图为使用forwading技术的统计结果。

通过对比可以看出,使用forwarding技术之后执行周期少了316-283=33个时钟周期,在这些时钟周期中,forwarding技术主要在于消除了执行过程中的数据相关(由65个中断减少至32个)。

因此,代码执行效率改善很多。

5)转移指令在转移成功和转移不成功时候的流水线开销。

由统计结果中的ConditionalBranches(如下图)可以看出,

优化前和优化后的ConditionalBranches都为上图显示,优化对于转移指令并无影响。

在本代码运行过程中,成功几率为93.75%,在进行一共16次转移中,taken一共15次。

分析原因可以知道,预测成功执行指令,当判断转移不成功是,系统对trap指令不再执行,进行跳转。

实验总结+实习体会

本次试验主要是对上一个实验中的代码进行优化,使我在做实验的过程中掌握了进行代码优化的方法,以及相关性的分析。

而相关性分析在我看来是重点,它关系到能否进行优化以及怎么优化。

首先需要分析程序中产生的相关性,代码优化的目的就是减少相关性的发生,提高流水线的效率。

通过上述的实验报告和数据对比,可以看到,代码优化我做到了。

实习体会:

其实总的来说这几次试验难度不大,主要还是将课上老师所讲的融入实验当中。

其中forwarding技术和预测技术都是课上老师详细讲过的,所以对于实验的理解起来更容易一些。

理解之后,通过实验结果的统计数据可以客观的看到这些技术对于流水线性能的影响。

这对于我来说收获颇多。

实验五循环展开

进一步学习DLX汇编语言编程方法,学习循环展开编译优化方法,观察采用循环展开编译优化方法所带来的性能的提高。

对循环程序采用循环展开(loopunrolling)方法进行优化,减少相关。

矩阵乘程序代码清单及注释说明

1)输入部分声明

2)输出部分声明

3)初始化矩阵A和矩阵B,包括初始化他们的行数、列数(因为是矩阵相乘,A的列数=B的行数;

并且要将A元素个数保存下来)。

并最终指向A的首地址。

4)循环嵌套,读入矩阵A的元素值。

5)接下来,需要读出A元素,并指向A首地址。

6)对矩阵A做行数变换

7)对矩阵B做变换

8)按照数学的方法对两个矩阵做乘法

9)矩阵相乘计算完毕后,询问是否需要循环重复本次操作

当编写好代码之后载入后,我遇到了一些问题。

报错信息为:

相关性分析结果

增加浮点运算部件对性能的影响

增加forward部件对性能的影响

转移指令在转移成功和转移不成功时候的流水线开销

实验总结+实习体会+课程建议

本次试验主要难点在于矩阵相乘代码的编写。

其实说难也不难,因为只要掌握了原理记忆WinDLX的语法规则即可顺利编写。

编写完后,我在执行的时候遇到了很多困难。

最终和同学讨论之后,也没有得到解决。

不过我查找了大量的资料,明白了报错原因以及我实际操作的问题。

本次试验重点是循环优化后与之前的性能比较。

虽然我没有得到结果,但我认真去做了之前的每次试验,收获颇多。

不仅如此,我觉得WinDLX我能够熟练应用,它的图像显示以及数据比例显示都能体现出软件的优越。

其实总的来说前4次试验难度不大,而最后一次是综合性的实验,不但要熟练掌握指令和代码,还要能够优化后分析优化的效果,以及循环展开之后的性能的对比。

其实主要还是将课上老师所讲的融入实验当中。

课程建议:

整体来说,实验课会占用平时理论课的课时也足以见得实验的重要。

由于每个人的能力不同,实验完成的程度也不一样。

但我觉得我能够认真按序按时间完成实验,本身对自己就是一种提高。

建议老师在第三次实验之后的“可研究与探索的问题”可以多加一些,这样在做实验的时候能够做一些研究,对于熟练掌握以及优化有所提升。