毕业设计---DDR的PCB设计文档格式.doc

《毕业设计---DDR的PCB设计文档格式.doc》由会员分享,可在线阅读,更多相关《毕业设计---DDR的PCB设计文档格式.doc(46页珍藏版)》请在冰豆网上搜索。

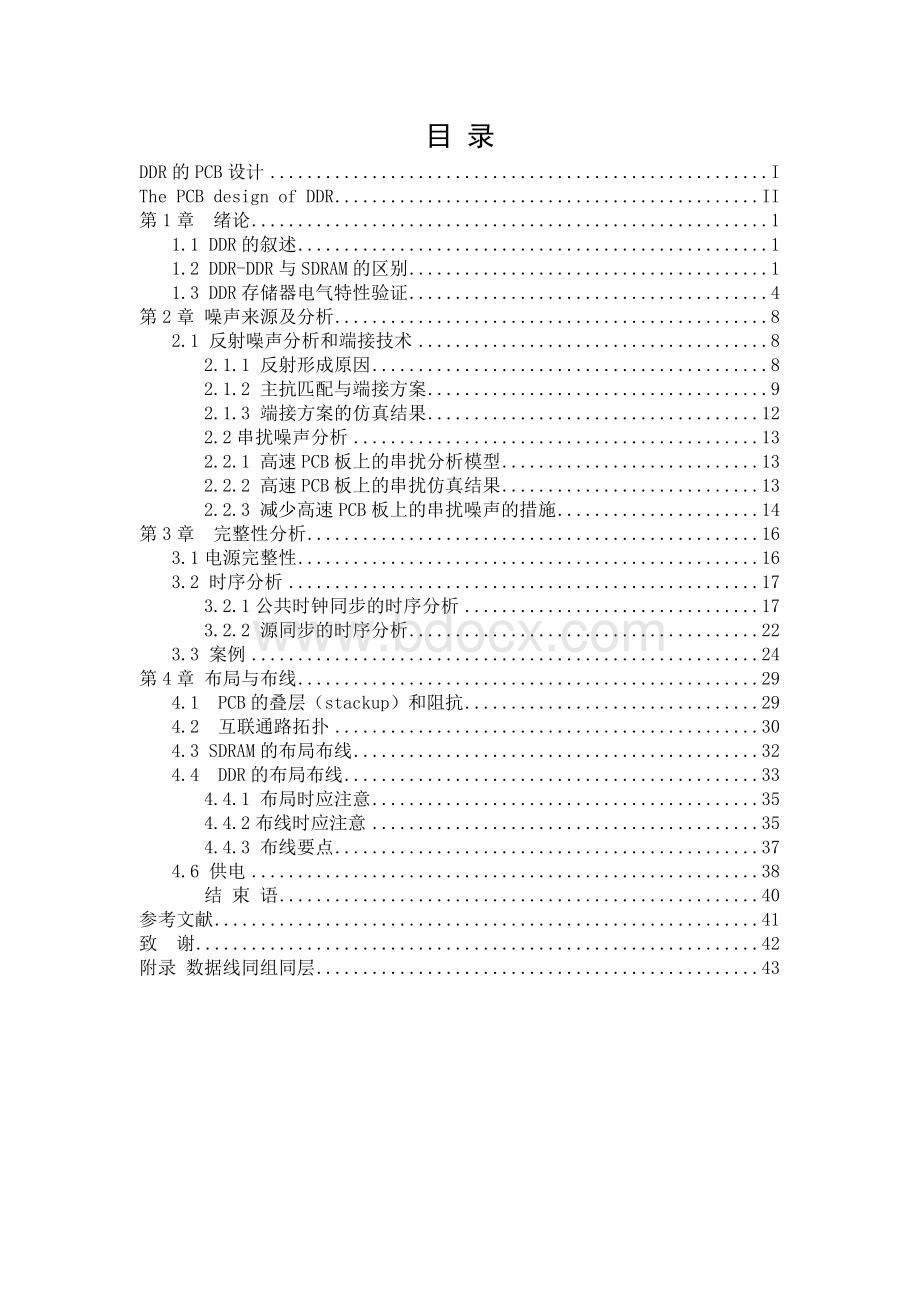

2.1.3端接方案的仿真结果 12

2.2串扰噪声分析 13

2.2.1高速PCB板上的串扰分析模型 13

2.2.2高速PCB板上的串扰仿真结果 13

2.2.3减少高速PCB板上的串扰噪声的措施 14

第3章完整性分析 16

3.1电源完整性 16

3.2时序分析 17

3.2.1公共时钟同步的时序分析 17

3.2.2源同步的时序分析 22

3.3案例 24

第4章布局与布线 29

4.1PCB的叠层(stackup)和阻抗 29

4.2互联通路拓扑 30

4.3SDRAM的布局布线 32

4.4DDR的布局布线 33

4.4.1布局时应注意 35

4.4.2布线时应注意 35

4.4.3布线要点 37

4.6供电 38

结束语 40

参考文献 41

致谢 42

附录数据线同组同层 43

43

DDR的PCB设计

摘要:

随着微电子技术和计算机技术的不断发展,DDR双通道同步动态随机存储器在通信系统中的应用越来越显得重要,而随着电子产品的集成化,对DDR在PCB中的设计要求也越来越高。

为了更好的能理解DDR,本文还与SDRAM一并做了介绍与设计。

本设计为基于DDR双通道同步动态随机存储器的PCB设计。

本文主要介绍了在对DDR的PCB设计时,所面临的信号完整性。

详尽的阐述了影响信号完整性的反射、串扰和信号完整性中的时序分析的相关理论并提出了减小反射和串扰得有效措施。

对布线与布局的一些注意事项及要点也做了详细的叙述。

关键字:

反射;

SDRAM;

串扰;

信号完整性;

时序

ThePCBdesignofDDR

Abstract:

Withmicroelectronicstechnologyanddevelopmentofcomputertechnology,DDRsynchronousdynamicrandomaccessmemorydoublechannelincommunicationsystem,theapplicationappearsmoreandmoreimportant,andastheelectronicproductofintegrationofthePCBdesignrequirementsoftheDDRmoreandmoreisalsohigh.InordertobetterunderstandDDR,thispaperalsointroducedtogetherwithSDRAManddesign.

BasedonthedesignofdoublechannelDDRsynchronousdynamicrandomaccessmemoryofPCBdesign.ThisarticlemainlyintroducedinPCBdesignforDDRfacedwhenthesignalintegrity.Detailedelaboratedtheinfluencesignalintegrityofthereflectionandcrosstalkandsignalintegrityoftiminganalysisandputforwardtherelevanttheoryofreflectionandreducecrosstalkeffectivemeasures.Forsomeofthelayoutandwiringmattersneedingattentionandpointstodothedetailednarration.

Keywords:

Reflex;

SDRAM;

Crosstalk;

Signalintegrity;

Timing

第1章绪论

1.1DDR的叙述

双通道同步动态随机存储器(双信道同步动态随机存取内存)即DDRSDRAM(DoubleDateRteSynchronousDynamicRandomAccessMemory)为具有双倍数据传输率之SDRAM,其数据传输速度为系统频率之两倍,由于速度增加,其传输效能优于传统的SDRAM。

如图1.1:

图1.1DDR

DDR是一种继SDRAM后产生的内存技术,DDR,英文原意为“DoubleDataRate”,顾名思义,就是双数据传输模式。

之所以称其为“双”,也就意味着有“单”,我们日常所使用的SDRAM都是“单数据传输模式”。

DDRSDRAM最早是由三星公司于1996年提出,由日本电气、三菱、富士通、东芝、日立、德州仪器、三星及现代等八家公司协议订立的内存规格,并得到了AMD、VIA与SiS等主要芯片组厂商的支持。

DDR这种内存的特性是在一个内存时钟周期中,在一个方波上升沿时进行一次操作(读或写),而DDR则引用了一种新的设计,其在一个内存时钟周期中,在方波上升沿时进行一次操作,在方波的下降沿时也做一次操作,之所以在一个时钟周期中,DDR则可以完成SDRAM两个周期才能完成的任务,所以理论上同速率的DDR内存与SDRAM内存相比,性能要超出一倍,可以简单理解为100MHZDDR=200MHZSDRAM。

1.2DDR-DDR与SDRAM的区别

DDRSDRAM与SDRAM的不同主要体现在以下几个方面:

1)DDRSDRAM与SDRAM一样,在开机时也要进行MRS,不过由于操作功能的增多,DDRSDRAM在MRS之前还多了一EMRS阶段(ExtendedModeRegisterSet,扩展模式寄存器设置),这个扩展模式寄存器控制着DLL的有效/禁止、输出驱动强度、QFC有效/无等。

由于EMRS与MRS的操作方法与SDRAM的MRS大同小异,在此就不再列出具体的模式表了,有兴趣的话可查看相关的DDR内存资料。

下面我们就着重说说DDRSDRAM的新设计与新功能。

差分时钟(参见上文“DDRSDRAM读操作时序图”)是DDR的一个必要设计,但CK#的作用,并不能理解为第二个触发时钟,而是起到触发时钟校准的作用。

由于数据是在CK的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求CK的上下沿间距要有精确的控制。

但因为温度、电阻性能的改变等原因,CK上下沿间距可能发生变化,此时与其反相的CK#就起到纠正的作用(CK上升快下降慢,CK#则是上升慢下降快)。

而由于上下沿触发的原因,也使CL=1.5和2.5成为可能,并容易实现。

2)数据选取脉冲(DQS)

DQS是DDRSDRAM中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。

每一颗芯片都有一个DQS信号线,它是双向的,在写入时它用来传送由北桥发来的DQS信号,读取时,则由芯片生成DQS向北桥发送。

完全可以说,它就是数据的同步信号。

在读取时,DQS与数据信号同时生成(也是在CK与CK#的交叉点)。

而DDR内存中的CL也就是从CAS发出到DQS生成的间隔,数据真正出现在数据I/O总线上相对于DQS触发的时间间隔被称为tAC。

注意,这与SDRAM中的tAC的不同。

实际上,DQS生成时,芯片内部的预取已经完毕了,tAC是指上文结构图中灰色部分的数据输出时间,由于预取的原因,实际的数据传出可能会提前于DQS发生(数据提前于DQS传出)。

由于是并行传输,DDR内存对tAC也有一定的要求,对于DDR266,tAC的允许范围是±

0.75ns,对于DDR333,则是±

0.7ns,其中CL里包含了一段DQS的导入期。

3)写入延迟

在上面的DQS写入时序图中,可以发现写入延迟已经不是0了,在发出写入命令后,DQS与写入数据要等一段时间才会送达。

这个周期被称为DQS相对于写入命令的延迟时间(tDQSS,WRITECommandtothefirstcorrespondingrisingedgeofDQS),对于这个时间大家应该很好理解了。

为什么要有这样的延迟设计呢?

原因也在于同步,毕竟一个时钟周期两次传送,需要很高的控制精度,它必须要等接收方做好充分的准备才行。

tDQSS是DDR内存写入操作的一个重要参数,太短的话恐怕接受有误,太长则会造成总线空闲。

tDQSS最短不能小于0.75个时钟周期,最长不能超过1.25个时钟周期。

有人可能会说,如果这样,DQS不就与芯片内的时钟不同步了吗?

对,正常情况下,tDQSS是一个时钟周期,但写入时接受方的时钟只用来控制命令信号的同步,而数据的接受则完全依靠DQS进行同步,所以DQS与时钟不同步也无所谓。

不过,tDQSS产生了一个不利影响——读后写操作延迟的增加,如果CL=2.5,还要在tDQSS基础上加入半个时钟周期,因为命令都要在CK的上升沿发出。

另外,DDR内存的数据真正写入由于要经过更多步骤的处理,所以写回时间(tWR)也明显延长,一般在3个时钟周期左右,而在DDR-Ⅱ规范中更是将tWR列为模式寄存器的一项,可见它的重要性。

4)突发长度与写入掩码

在DDRSDRAM中,突发长度只有2、4、8三种选择,没有了随机存取的操作(突发长度为1)和全页式突发。

这是为什么呢?

因为L-Bank一次就存取两倍于芯片位宽的数据,所以芯片至少也要进行两次传输才可以,否则内部多出来的数据怎么处理?

而全页式突发事实证明在PC内存中是很难用得上的,所以被取消也不希奇。

另外,DDR内存的数据真正写入由于要经过更多步骤的处理,所以写回时间(tWR)也明显延长,一般在3个时钟周期左右,而在DDR-Ⅱ规范中更是将tWR列为模式寄存器的一项,可见它的重要性。

但是,突发长度的定义也与SDRAM的不一样了,它不再指所连续寻址的存储单元数量,而是指连续的传输周期数,每次是一个芯片位宽的数据。

对于突发写入,如果其中有不想存入的数据,仍可以运用DM信号进行屏蔽。

DM信号和数据信号同时发出,接收方在DQS的上升与下降沿来判断DM的状态,如果DM为高电平,那么之前从DQS中部选取的数据就被屏蔽了。

有人可能会觉得,DM是输入信号,意味着芯片不能发出DM信号给北桥作为屏蔽读取数据的参考。

其实,该读哪个数据也是由北桥芯片决定的,所以芯片也无需参与北桥的工作,哪个数据是有用的就留给北桥自己去选吧。

5)延迟锁定回路(DLL)

DDRSDRAM对时钟的精确性有着很高的要求,而DDRSDRAM有两个时钟,一个是外部的总线时钟,一个是内部的工作时钟,在理论上DDRSDRAM这两个时钟应该是同步的,但由于种种原因,如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身也有不稳定的情况(SDRAM也内部时钟,不过因为它的工作/传输频率较低,所以内外同步问题并不突出)。

DDRSDRAM的tAC就是因为内部时钟与外部时钟有偏差而引起的,它很可能造成因数据不同步而产生错误的恶果。

实际上,不同步就是一种正/负延迟,如果延迟不可避免,那么若是设定