DDS信号发生器原理Word格式文档下载.docx

《DDS信号发生器原理Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《DDS信号发生器原理Word格式文档下载.docx(12页珍藏版)》请在冰豆网上搜索。

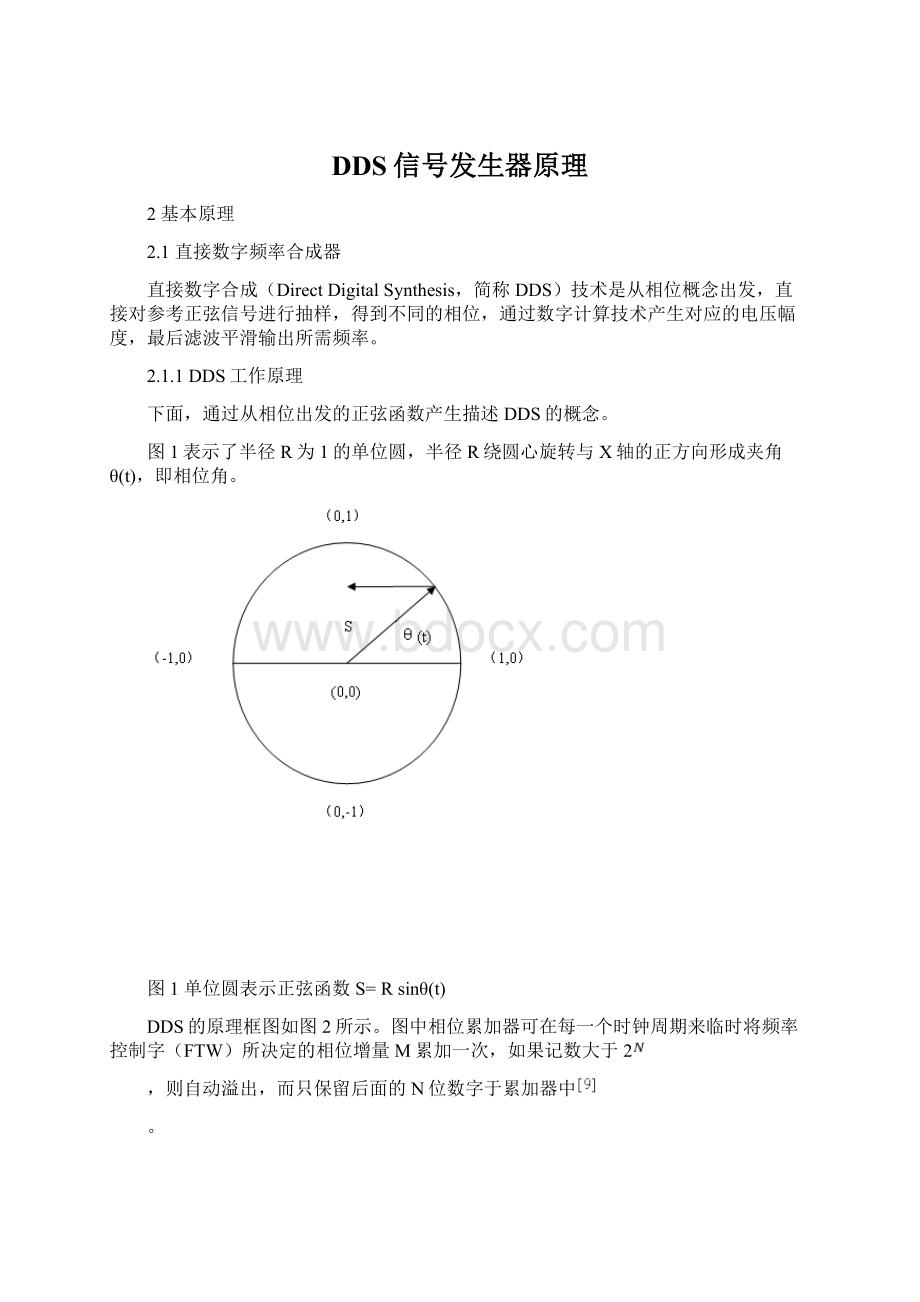

取模运算,得到的和(以N位二进制数表示)作为相位值,以二进制代码的形式去查询正弦函数表ROM,将相位信息转变成相应的数字量化正弦幅度值,ROM输出的数字正弦波序列再经数模转换器转变为阶梯模拟信号,最后通过低通滤波器平滑后得到一个纯净的正弦模拟信号。

由于ROM表的规模有限,相位累加器一般仅取高位作为寻址地址送入正弦查询表获得波形幅度值。

正弦查询表中以二进制数形式存入用系统时钟对正弦信号进行采样所得的样值点,可见只需改变查询表内容就可实现不同的波形输出。

2.1.2DDS的结构

DDS的基本结构包括相位累加器、正弦查询表(ROM)、数模转换器(DAC)和低通滤波器(LPF),其中从频率控制字到波形查询表实现由数字频率值输入生成相应频率的数字波形,其工作过程为:

⑴确定频率控制字M;

⑵在时钟脉冲f

的控制下,该频率控制字累加至相位累加器生成实时数字相位值;

⑶将相位值寻址ROM转换成正弦表中相应的数字幅码。

模块DAC实现将数字幅度值高速且线性地转变为模拟幅度值,DDS产生的混叠干扰由DAC之后的低通滤波器滤除

㈠相位累加器

相位累加器是DDS最基本的组成部分,用于实现相位的累加并存储其累加结果。

若当前相位累加器的值为Σ

,经过一个时钟周期后变为Σ

,则满足

Σ

=Σ

+M

为一等差数列,不难得出:

=nM+Σ

其中Σ

为相位累加器的初始相位值。

㈡正弦查询表(ROM)

DDS查询表所存储的数据是每一个相位所对应的二进制数字正弦幅值,在每一个时钟周期内,相位累加器输出序列的高m位对其进行寻址,最后的输出为该相位相对应的二进制正弦幅值序列。

㈢数模转换器(DAC)

数模转换器的作用是将数字形式的波形幅值转换成所要求合成频率的模拟形式信号。

DAC有电压和电流输出两种,其输出的信号并不能真正连续可变,而是以其绝对分辨率为最小单位的,所以其输出实际上是一个阶梯模拟信号。

2.1.3DDS的优点

正由于DDS采用全数字技术,从概念到结构都有很大的突破,所以它具有其他频率合成所无法比拟的优越性。

①频率分辨率高。

若时钟频率不变,DDS频率分辨率仅由相位累加器位数来决定,也就是理论上的值越大,就可以得到足够高的频率分辨率。

目前,大多数DDS的分辨率在1Hz数量级,许多都小于1mHz甚至更小,这是其他频率合成器很难做到的。

②工作频带较宽。

根据Nyquist定律,只要输出信号的最高频率分辨率分量小于或等于f

/2就可以实现。

而实际当中由于受到低通滤波器设计以及杂散分布的影响限制,仅能做到40%f

左右。

③超高速频率转换时间。

DDS是一个开环系统,无任何反馈环节,这种结构使得DDS的频率转换时间极短。

DDS的频率转换时间可达到纳秒数量级,比使用其它的频率合成方法都要小几个数量级。

④相位变化连续。

改变DDS输出频率,实际上改变的是每一个时钟周期的相位增量,相位函数的曲线是连续的,只是在改变频率的瞬间其频率发生了突变,因而保持了信号相位的连续性

⑤具有任意输出波形的能力。

只要ROM中所存的幅值满足并且严格遵守Nyquist定律,即可得到输出波形。

例如三角波、正弦波和矩形波。

⑥具有调制能力。

由于DDS是相位控制系统,这样也就有利于各种调制功能。

2.2波形产生分析

图3正弦波产生框图

相位累加器为32位累加器,输出为0~(2

-1),作为正弦查询表的地址输入端。

正弦表中存放一个周期的正弦波内的2

个点的数据,输出f

为一正弦波,其频率由频率控制字进行调节,输出频率:

f

=f

/2

FTW

最小频率分辨率:

其中N为相位累加器的位数,FTW为频率步进控制字,f

为时钟频率,输出信号频率主要取决于频率控制字FTW。

当FTW增大时,f

可以不断增加,综合考虑Nyquist采样定理,最高输出频率应小于f

/2。

根据实验所得,实际工作频率应小于f

/3

由于本论文只要求设计出最高为1MHz的信号,根据DA及FPAG的速度,可以很容易地满足设计需要。

本例中选用32M的CLK时钟,在输出最高1MHz的信号时,波形在一个周期内仍有32个点,能够完整描述出波形。

=32×

10

=0.00745058

所以可以实现1Hz步进,当输出1Hz时,频率控制字FTW=1/f

=134.217728。

由于频率控制字是由NIOS系统提供的,考虑到浮点运算所占资源太多,所以把浮点运算改为定点运算。

则当输出其他任意频率f

时Nios内部算法为:

FTW=f

×

134+f

21/100+f

77/10000+f

28/1000000

3总体设计

近年来现场可编程门阵列(FPGA)得到了迅速的发展和广泛的应用,其资源容量、工作频率以及集成度都得到了极大的提高,使得利用FPGA实现某些专用数字集成电路得到了大家的关注,而基于FPGA实现的DDS信号发生器则更有发展前途和研究的意义

3.1设计的要求

根据我们所学的知识储备,对本次信号发生器的设计提出了以下要求:

①信号发生器能产生正弦波、方波和三角波三种周期性波形;

②输出信号频率在10Hz~1MHz范围内可调,输出信号频率稳定度优于10

;

③在1k负载条件下,输出正弦波信号的电压峰-峰值Vopp在0~5V范围内可调;

④输出信号波形无明显失真;

3.2方案比较及选择

方案一:

采用模拟锁相环实现。

模拟锁相环技术是一项比较成熟的技术。

应用模拟锁相环,可将基准频率倍频,或分频得到所需的频率,且调节精度可以做到相当高、稳定性也比较好。

但模拟锁相环模拟电路复杂,不易调节,成本较高,并且频率调节不便且调节范围小,输出波形的毛刺较多,得不到满意的效果

方案二:

采用直接数字频率合成,用单片机作为核心控制部件,能达到较高的要求,实现各种波形输出,但受限于运算位数和运算速度,产生的波形往往达不到满意效果,并且频率可调范围小,很难得到较高频率,并且单片机的引脚少,存储容量少,这就导致了外围电路复杂

方案三:

采用直接数字频率合成,用FPGA器件作为核心控制部件,精度高稳定性好,得到波形平滑,特别是由于FPGA的高速度,能实现较高频率的波形。

控制上更方便,可得到较宽频率范围的波形输出,步进小,外围电路简单易实现。

因此采用方案三。

4DDS信号发生器的实现

4.1硬件电路的制作

根据设计要求,本论文选用EDA比赛套件中:

EDA-SOPC核心板、LCD1602、RS232&

PS2及DDS_BOARD四个模块。

电源采用5V直流电源及±

5V电源供电。

各模块连接如图4所示:

图4各模块连接示意图

各模块功能如下:

一、由EDA-SOPC核心板提供的FPGA及SDRAM为本系统的核心器件。

主要完成功能:

1、采用DDS技术基于FPGA设计信号发生模块,产生要求的信号序列;

2、利用SDRAM配合FPGA构成片上系统,建立NIOS控制系统,完成任务调度及人机交互控制。

核心板分别通过相关接口与其它三个功能模块相连。

二、RS232&

PS2模块通过8-PIN双排线与核心板的PORT2CP接口相连。

将PS2接口的数字小键盘连接到该模块的PS/2接口上,实现按键输入功能。

三、LCD1602模块通过16-PIN双排线与核心板的PORT12-LCD接口相连。

将液晶LCD1602连接到该模块的液晶接口上,实现人机交互的显示功能

四、DDS模块分别通过14-PIN双排线与核心板的PORT14-DA接口相连及通过16-PIN双排线与核心板的PORT16-IO接口相连。

该模块实现两路D/A,其中一路产生信号,另一路实现信号幅度的调整,模块的BNC接头直接输出信号。

4.2硬件模块的介绍

4.2.1EDA-SOPC核心板

EDA-SOPC核心板主芯片使用了CycloneII系列芯片EP2C8Q208C8,具有8256个逻辑单元(LE),可以满足更多、更大的系统需求;

18个18*18位乘法器,可以实现数字信号处理(DSP功能);

2个增强型锁相环(PLLs),能够提供先进的时钟管理能力,如频率合成、可编程移相、外部时钟输出、可编程占空比、锁定检测、可编程带宽、输入时钟扩频和支持高速差分输入输出时钟信号;

具有138个用户I/O,能够满足大多数系统需求。

使用了1个16位SDRAM内存,组建成一个片外8Mbytes系统内存电路;

配备了4Mbytes的Flash,用来保存用户数据、系统工程等;

使用EPCS4作为配置芯片;

丰富的外围设备,供用户进行高级设计

选用大功率电源芯片来保障系统稳定工作。

在此硬件平台上SOPC系统频率达到110MHz,但建议使用的系统频率为85MHz,这样会使系统能更稳定的运行。

4.2.2LCD1602模块

LCD1602模块是由液晶LCD1602为核心,提供16×

2字符显示的电路模块。

该模块可通过16针接口连接到EDA-SOPC核心板上,使用方便。

该模块电路指底板电路,主要提供EDA-SOPC核心板与LCD1602液晶接口及液晶所需的负压调节及背光控制电路。

该接口采用16针接口与核心板PORT12-LCD接口相连。

具体如下:

图5与EDA-SOPC核心板接口

4.2.3RS232&

PS2模块

RS232&

PS2模块由RS232电平转换电路和PS2键盘接口电路两部分组成,用于完成RS232串口通信和PS2接口通信,可实现与计算机串口通信、PS键盘扩展等功能。

该模块可通过8针接口连接到EDA-SOPC核心板上。

4.2.4DDS_BOARD模块

DDS_BOARD模块包括DA转换、驱动等电路组成。

该模块输入端有两组DA数据,一路数据经DA转换后成作为信号输出,另一路数据经DA转换后成作为输出信号的幅度调节。

经合EDA-SOPC核心板的DDS技术可实现任意波形,一定频率、一定幅度范围的信号输出

该模块可分别通过14针和16针两条数据线连接到EDA-SOPC核心板上。

与EDA-SOPC核心板接口,该接口采用14针和16针两条数据线分别与核心板PORT10-DA和PORT12-IO接口相连。

图6与EDA-SOPC核心板接口

5软件设计

5.1设计的原理图

信号发生器的原理图如附录所示,图中涉及到相位累加器、正弦波查询、波形输出等模块的设计,并由各个模块之间的连接构成满足产生正弦波的信号发生器。

通过选择波形输出模块的波形选择端sel就可实现方波和三角波的产生,改变频率控制字的大小就可实现调频,在时钟频率一定时,相位累加器的位数越大,频率调节就越精细

相位累加器的输出端与波形输出模块的10位地址输入端(addr[9..0])相连,正弦波查询表的输出端与波形输出模块