数字逻辑电路设计实验教案赵蕙Word文档下载推荐.docx

《数字逻辑电路设计实验教案赵蕙Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《数字逻辑电路设计实验教案赵蕙Word文档下载推荐.docx(43页珍藏版)》请在冰豆网上搜索。

实验步骤

1.设计

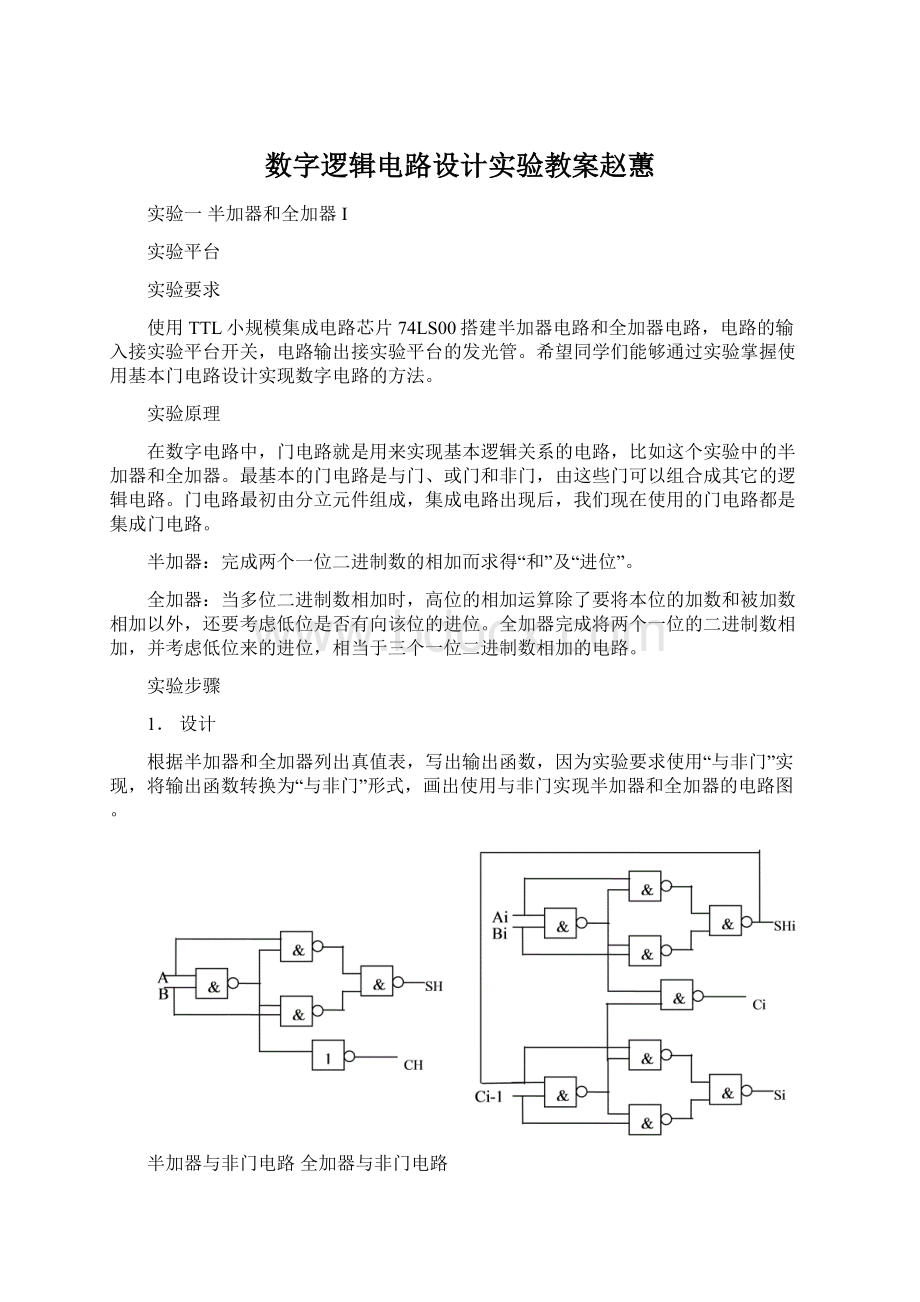

根据半加器和全加器列出真值表,写出输出函数,因为实验要求使用“与非门”实现,将输出函数转换为“与非门”形式,画出使用与非门实现半加器和全加器的电路图。

半加器与非门电路全加器与非门电路

2.连线

请特别注意VCC和GND的连接,不要接错,以免芯片烧毁!

所用芯片的Vcc连起来接+5V;

所用芯片的GND连起来接地(GND)。

电路的输入接实验平台开关,电路的输出接实验平台的发光管。

实验提供的74LS00芯片逻辑与引脚图如下。

每块芯片中有四组2输入端与非门(正逻辑),根据步骤1设计的电路图,搭建半加器电路需要5个与非门(可使用2块74LS00芯片),搭建全加器电路需要9个与非门(可使用3块74LS00芯片)。

双列直插封装74LS00芯片逻辑图和引脚图

3.验证

开关向上拨为“1”,向下拨为“0”;

发光管为“1”时点亮,为“0”时熄灭。

根据真值表,检验你所搭建的半加器和全加器电路,是否满足设计要求。

教你一招:

实验平台上可能有个别开关、发光管故障,可以将导线一端接开关,一端接发光管,如果开关向上拨时,发光管点亮;

开关向下拨时,发光管熄灭,说明开关、发光管、导线都是好的。

完成连线后的电路可能有误,在没有万用表的情况下,此法也可帮你检查电路故障。

实验报告要求

1.填妥姓名、班级外,必须填写完成报告的日期(年月日),以后的实验报告要求里不再冗述。

2.写出使用TTL小规模集成电路芯片74LS00完成半加器的设计和实现的完整过程(根据功能要求列真值表->

写输出函数->

将输出函数变换成“与非门”形式->

画出电路图->

根据芯片引脚连线->

验证结果)

3.结合实验中接触和使用的小规模集成电路,请说说什么是集成电路?

常用的中小规模集成电路产品有哪些?

4.实验过程中你遇到了哪些问题?

实验刚开始时,你觉得计算机硬件课程的实验最难理解的地方在哪里?

5.实验一和实验二使用两种不同的方式(小规模集成电路,可编程器件)实现全加器电路,就两种方式谈谈你实验的体会。

实验二FPGA设计流程——全加器II

EDA/SOPC实验开发平台,实验二以后的所有实验都使用此开发平台。

根据实验平台提供的Altera公司可编程器件FPGA(现场可编程门阵列),使用Altera公司的EDA设计开发工具QuartusII,用原理图方式设计实现全加器电路,电路的输入接实验平台开关,电路输出接实验平台的发光管。

希望同学们能够通过实验掌握使用可编程器件设计实现数字电路的方法。

使用可编程器件进行数字电路设计,将传统的“设计硬件搭试焊接”过程变为“设计编译下载”的过程,其主要工作都在计算机内完成,先将设计输入计算机,再由开发系统将其转换成编程文件下载到可编程器件中。

全加器电路图的设计同实验一。

1.新建工程

实验室机器安装的设计环境为:

QuartusIIVersion9.0。

双击桌面图标,运行QuartusII软件。

用NewProjectWizard工具选项创建此设计的工程,并设计相关信息。

点击菜单项File->

newprojectwizard…,出现introduction对话框,如图1。

图1

单击next,进入Directory,name,Top-LevelEntity设置对话框,选择工程存放路径(请在E盘或F盘新建一个工程相文件夹,实验室的C盘、D盘及桌面被保护)、工程名称和顶层模块名称(本例工程名和顶层模块名均设为fadder。

)注意:

所有的名称和路径均不能包含空格和汉字。

如图2。

图2

跳过图3所示AddFiles对话框,该对话框设置用来将已存在的设计文件加入到工程中。

图3

点击next,进入Family&

devicessettings对话框,指定FPGA器件为Cyclone系列的EP1C12F324C8,如图4。

Cyclone

系列FPGA是Altera公司最初(20XX年)的低成本FPGA。

20XX年和20XX年,Altera公司又推出了更新的,密度更高的CycloneII和CycloneIII系列

FPGA,进一步巩固它在大批量、低成本应用解决方案中的地位。

图4

图5

图5对话框用来设置第三方EDA工具,包括综合工具,仿真工具和时序分析工具,这里我们点击Next跳过。

图6

信息显示区

编译状态区

资源管理区

工程工作区

标题栏

菜单栏

工具栏

图7

最后,新建工程向导会根据你之前一步一步的设置,给出一个工程设置概述页如图6,单击finish完成工程创建。

完成后,QuartusII界面如图7所示。

所有在新建工程向导中进行的设置,在工程建立完成后,都可以通过QuartusII菜单项进行修改。

2.设计输入

new…,出现新建源文件对话框如图8,数字电路的设计文件总的来说有两种方式,原理图方式和硬件描述语言方式,这次实验我们使用原理图方式设计电路,所以选择新建一个“BlockDiagram/SchematicFile”文件,图8,点击“OK”按钮,打开原理图编辑器。

图8

原理图编辑器的工具栏如图10所示,工具栏上的按钮作用依次分别是“分离窗口切换”、“选择”,“添加文字”、“符号工具”、“块工具”、“正交结点工具”、“正交总线工具”、“正交管道工具”、“橡皮筋工具”、“部分线选择工具”、“放大缩小工具”、“全屏”、“查找工具”、“水平翻转”、“垂直翻转”、“逆时针90度翻转”、“矩形工具”、“椭圆工具”、“直线工具”、“弧线工具”。

图9

QuartusII提供了许多基本库元件给用户使用,根据实验一全加器的设计,共需要9个“2输入与非门电路”模块。

在原理图编辑区的空白处双击鼠标,或点击符号工具打开Symbol对话框如图9。

在Symbol对话框中,设计全加器电路需要的“与非门”可以通过选择“Primitives->

logic”基本原件库中的“nand2”模块,点击“OK”,将该模块加入原理图中。

重复该过程,或在原理图编辑区选中已经添加好的nand2模块,使用Ctrl+C和Ctrl+V继续添加。

全加器电路的输出端口和输入端口,在Symbol对话框中,使用“Primitives->

pin”库中的“input”模块和“output”模块,添加到原理图中。

添加完成后,可以在原理图中双击各个输入输出模块,为它们改名,尽量让端口名称具有可读性,本例可改为Ai、Bi、Ci-1、SHi、Si、Ci如图11。

与非门、输入端口、输出端口之间的连接使用“正交结点工具”完成。

完成后的原理图如图11。

图10

图11

设计输入完成后,保存文件,将模块名命名为顶层模块名,即新建工程时指定的顶层模块名,本例为:

fadder.bdf。

新建的文件默认情况下会自动加入到工程中。

3.逻辑综合

为工程添加好设计文件以后,下一步就是对工程设计进行综合,本例使用QuartusII软件内嵌的分析综合工具Analysis&

Synthesis进行。

点击工具栏中按钮,对设计进行综合。

Analysis&

Synthesis将检查工程的逻辑完整性和一致性。

设计如果综合通过,编译状态显示区中Analysis&

Synthesis步骤前面会显示绿色的勾,如果设计有错误,会显示红色的叉,如图12,出错行号及错误原因会显示在信息显示区中,如图13。

图12

图13

根据错误原因提示修改设计,完成修改后,重新综合,直到综合通过,资源管理区中可以点击顶层模块名称前的+号,显示模块间的树形结构,编译状态显示区的Analysis&

Synthesis步骤前显示绿色的勾,如图14。

图14

初学者往往不习惯阅读错误信息。

实际上学会读懂错误信息是很有用的!

4.功能仿真

在综合通过以后,只能够说明设计符合语法规范,但并不能保证设计满足功能要求,需要通过功能仿真,来验证电路功能是否符合设计要求,功能仿真的考察是的电路在理想环境下的行为,不考虑电路门延迟与线延迟。

这里使用QuartusII自带的波形图仿真工具进行。

1)新建仿真波形图文件

要使用QuartusII自带的波形图仿真工具进行仿真,首先要新建一个波形图文件。

在File菜单中选择New,出现如图8中所示对话框,在Verification/DebuggingFiles页中选择VectorWaveformFile,点击OK按钮,出现一个空的波形图文件,如图15。

图15

2)添加观察信号结点

用菜单Edit->

Insert->

InsertNodeorBus…,打开如图16所示对话框。

可以直接在Name文本框中直接输入信号名称,也可以通过点击按钮NodeFinder…,打开结点查询对话框来如图17,来添加需要观察的信号。

图16

本例在NodeFinder对话框的Filter选项下拉菜单中选择Pins:

all,然后点击List按钮,在NodesFound列表中,选中Ai、Bi、Ci-1、SHi、Si、Ci信号,双击或使用按钮,将它们添加到观察信号中。

最后点击“OK”按钮,完成观察信号的添加。

图17

3)编辑输入波形

在Name栏中选中输入信号的名称,这组输入信号所在的行将被高亮,如图18。

通过菜单Edit->

Value,或者直接使用工具栏按钮对输入信号的波形进行设定。

图18

如图19工具栏上的按钮作用分别是“分离窗口切换”、“选择”,“添加文字”、“编辑波形”、“放大缩小”、“全屏幕切换”、“查找”、“替换”、“设置为Unknown”、“置0”、“置1”、“设置为高阻”、“设置为WeakUnknown”、“设置为WeakLow”、“设置为WeakHigh”、“设置为Don’tCare”、“设置为取反”、“设置计数值”、“设置时钟”、“设置为任意值”、“设置随机值”、“贴齐网格线”、“排序”。

图19

信号添加完成并且编辑好波形后,保存文件,本例为fadder.vwf。

4)在QuartusII中指定仿真文件

用菜单Assignment->

Setting…在SimulatorSettings中,设置Simulationmode为“Functional”,设置fadder.vwf为仿真输入文件,仿真结束的条件可以根据需要在SimulationPeriod项中选择,如图20选择仿真运行80ns结束。

点击“OK”按钮完成设置。

图20

5)生成功能仿真网表

用菜单Processing->

GenerateFunctionalSimulationNetlist。

如果缺少这一步,在仿真运