数电重点章节典型例题完整Word下载.docx

《数电重点章节典型例题完整Word下载.docx》由会员分享,可在线阅读,更多相关《数电重点章节典型例题完整Word下载.docx(23页珍藏版)》请在冰豆网上搜索。

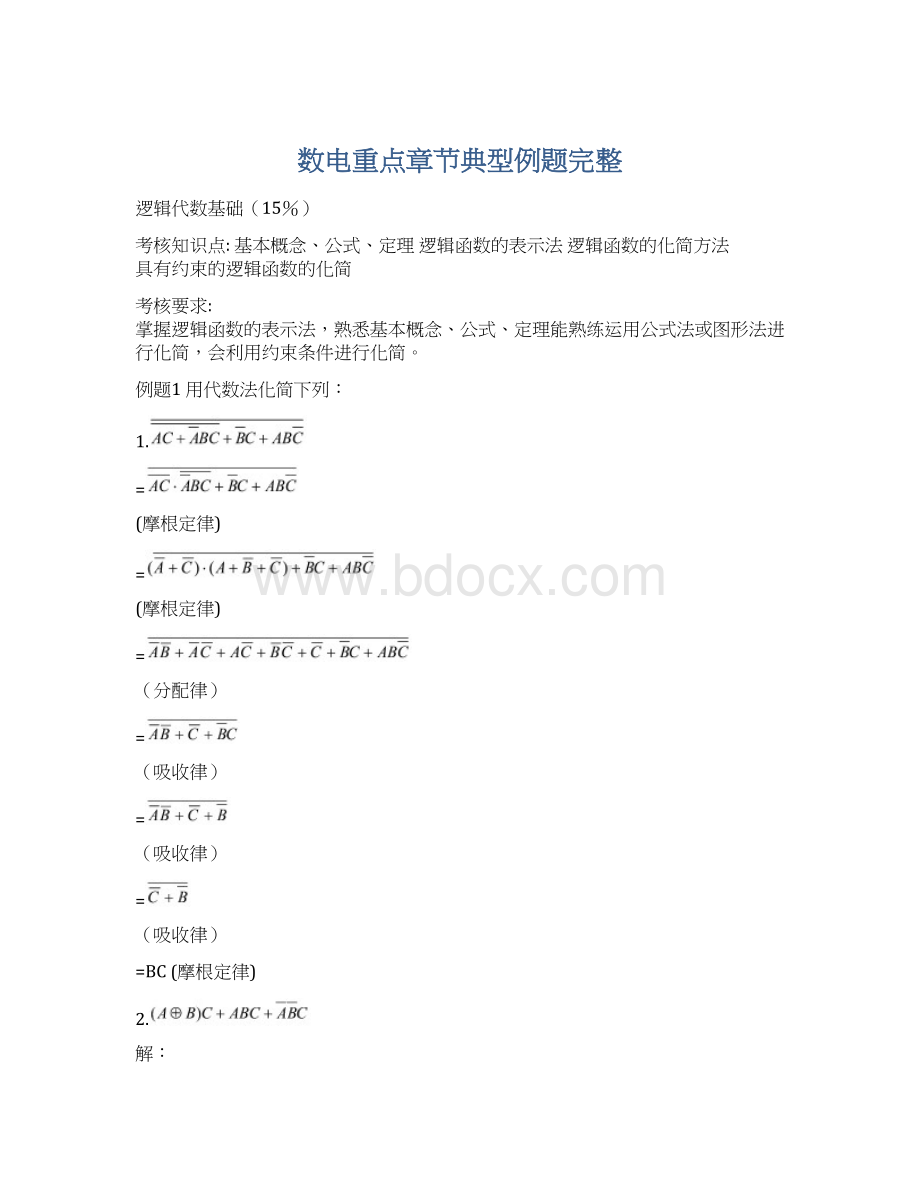

2、L(A,B,C,D)=∑m(1,4,6,9,13)+∑d(0,3,5,7,11,15)

(1)L(A,B,C,D)=∑m(3,4,5,6,9,10,12,13,14,15)

将逻辑函数填入卡诺图并圈“1”,如图解(a)所示。

对应写出最简逻辑表达式:

(a)(b)

(2)L(A,B,C,D)=∑m(1,4,6,9,13)+∑d(0,3,5,7,11,15)

将逻辑函数填入卡诺图并圈“1”,如图解3.6(b)所示。

对应写出逻辑表达式:

*讨论:

在对逻辑函数进行卡诺图化简时,要注意下列几个问题:

1.在卡诺图的左上角标出函数及变量,变量的顺序是:

从左至右对应变量的最高位到最低位。

2.圈“1”时注意对边的格相邻、四角的格也相邻。

不要漏掉有“1”的格,当只有一个独立的“1”时,也要把它圈起来。

3.当函数中存在无关项时,无关项的值可以任取(用“×

”表示)。

化简时究竟如何圈是以将函数化为最简为原则。

若圈起来,则认为是“1”,若不圈,则认为是“0”,但有“1”的格,不能漏掉。

例题3、已知逻辑函数Y=

求:

(1)标准“与或”表达式,Y=

(2)反函数“与或”表达式,

(3)对偶式Y’=

2.组合逻辑电路(20%)

组合电路的分析与设计方法编码器译码器比较器全加器多路选择器只读存储器

了解组合电路结构、功能上的特点及消除竞争冒险的方法,熟练掌握组合电路的分析方法,并能根据要求设计组合逻辑电路。

例题用3线—8线译码器74LS138实现下列函数:

(要求写出变换过程)

.

例题.与或非门组成的电路如图所示:

(1)

写出输出函数的表达式

(2)列出其真值表

(1)

(2)真值表

ABC

F

000

001

010

011

100

101

110

111

1

例题、已知逻辑函数F=f(A,B,C,D)其卡诺图的表示形式如图所示。

(1)写出其最简与或式;

(2)写出其反函数的最小项表示式;

(3)写出其对偶函数的最小项表示式;

(4)用8选1数据选择器实现该函数;

(用降维法)

或

(1):

)

或

(2)

(3)

(4)降维后的卡诺图(用扩展法将两片8选1扩展为16选1)

例题、用8选1数据选择器设计一函数信号发生器电路,它的功能表如表所示。

电路功能表

例题写出如下图2(a)所示组合逻辑电路的表达式和真值表,然后用图2(b)所示的四选一数据选择器实现。

图2(a)图2(b)

3.时序逻辑电路(25%)

时序电路的结构特点和逻辑功能特点时序电路的分析和设计方法用集成计数器构成任意进制计数器

熟悉时序逻辑电路在逻辑功能和电路结构方面的特点,熟悉时序电路逻辑功能的描述方法。

熟练掌握时序电路逻辑功能的一般分析方法。

掌握用集成计数器构成任意进制计数器的方法。

例题、在图中所示的时序电路中,X为控制信号,Q1、Q2为输出信号,CP为一连续脉冲。

(1)画出其状态转换图。

说明电路的功能。

(2)说明电路的功能。

(1)状态方程为

(2)当X=0时,按二进制加法计数。

当X=1时,按二进制减法计数。

状态转换图:

例题画出下图所示时序电路在一系列CP信号作用下,Q1、Q2、Q3的输出电压波形。

触发器采用下降沿触发,初始状态为Q=0。

(20分)

例题、电路如图题5.19所示,已知CP和A的波形,画出触发器Q0、Q1及输出VO的波形。

设触发器的初始状态均为0。

图题

Q0、Q1及输出VO的波形见图解。

图解

例题、图示电路是可变模值计数器。

试分析当控制变量X为1和为0时电路分别是几进制计数器。

X=1时:

当Q3Q2Q1Q0=1011

是11进制计数器

X=0时:

当Q3Q2Q1Q0=1001

是9进制计数器

例题试用4位同步二进制计数74LS161接成九进制计数器,可以加必要的门电路,74LS161的功能表如下:

附表174161功能表

CP

EP

ET

D3

D2

D1

D0

Q3Q2Q1Q0

×

0000

↑

A

B

C

D

ABCD

保持

1×

×

计数

例题由集成四位二进制同步步计数器74161和8选1数据选择器74LS151组成的电路如图所示。

试按要求回答:

(1)74161组成几进制计数器电路;

(2)画出计数状态转换图;

(3)写出输出Y的序列信号的一个周期;

(1)74161组成十进制计数器电路

(2)计数状态转换图如下

(3)F的序列周期取决于计数器高三位Q3Q2Q1的周期,

所以010*******,0101111101

例题用集成计数器160和8选1数据选择器设计信号发生器,使之在一系例CLK信号作用下周期性输出序列信号“0010110111”的系列信号。

例题、用D触发器和门电路设计一个11进制计数器,并检查能否自启动

用四个维持阻塞型D触发器设计

(用下降沿触发的JK触发器,设计一个按自然序进行计数的同步七进制加法计数器)

例题、用下降沿触发的D触发器设计同步时序电路,电路状态图如下图所示。

(要求写出设计过程)

000001011

100110111

状态方程:

驱动方程:

输出方程:

4.脉冲产生、整形电路(10%)

多谐振荡器施密特触发器单稳态触发器555定时器

了解555内部结构,熟悉其功能表及外部特性,并会用555构成施密特触发器、多谐振荡器和单稳态触发器。

熟悉多谐振荡器的结构、工作原理,会估算输出脉冲的周期、频率。

熟悉单稳触发器的结构、工作原理,会估算输出脉冲的宽度。

熟悉施密特触发器的回差特性。

会估算上、下限触发电平回差电压数值。

例题下图是用CMOS与非门组成的脉冲电路,输入vI为窄脉冲。

要求:

(1)说明这是一个什么电路?

(2)指出稳态时a,b,d,e,f各点的电平高低;

(3)说明暂稳态维持时间tpo与电路中哪些参数有关?

(1)单稳态触发器

(2)a.高电平b.低电平d.低电平e.高电平f.低电平

(3)tpo与RC参数有关及门电路阀值电压有关。

例题集成定时器CC7555的电路如图所示。

1.用该集成定时器及在规格为100kΩ,200kΩ,500kΩ的电阻,0.01μF,0.1μF,1μF电容器中选择合适的电阻和电容,设计一个满足图(b)所求波形的单稳态触发器。

2.

用该集成定时器设计一个斯密特触发器,画出斯密特触发器的电路图。

当输入UI为的波形时,画出斯密特触发器的输出u0波形

(a)(b)

图

解

1).要实现的单稳态触发器用框图表示如下:

2).斯密特触发器如图,波形如右图

例题.由555定时器,三位二进制加计数器,理想运算放大器A构成如图所示电路。

设计数器初始状态为000,且输出低电平VOL=0V,输出高电平VOH=3.2V,Rd为异步清零端,高电平有效。

1.说明:

虚框

(1)、

(2)部分各构成什么功能电路?

2.虚框(3)构成几进制计器?

3.对应CP画出VO波形,并标出电压值。

1).本电路由555定时器组成多谐振荡器产生CP脉冲,作为计数脉冲。

计数器二进制数作为倒T型电阻网络D/A转换器输入数字量。

因此,虚框1为多谐振荡器,虚框2为倒T型D/A转换器

2).虚框3为4进制计数器

3)、倒T型D/A转换器

D/A输出波形如下图所示

例题、如图所示电路是用十位集成R-2R倒T型数模转换器CB7520和74LS161组成的波形发生器电路。

已知CB7520参考电压VREF=-10V,请求出vo的值。

(8分).