合肥学院微机习题集.docx

《合肥学院微机习题集.docx》由会员分享,可在线阅读,更多相关《合肥学院微机习题集.docx(47页珍藏版)》请在冰豆网上搜索。

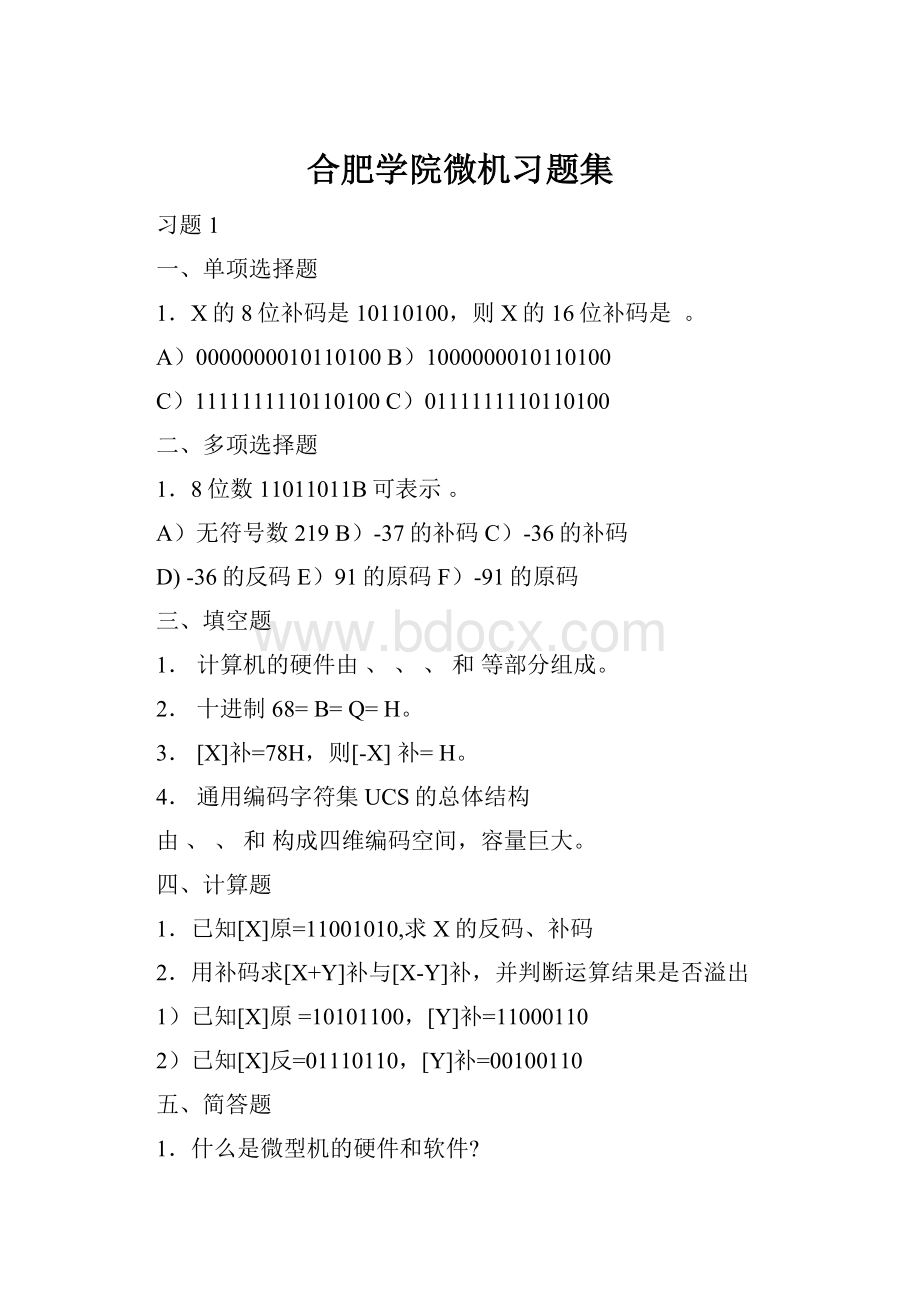

合肥学院微机习题集

习题1

一、单项选择题

1.X的8位补码是10110100,则X的16位补码是。

A)0000000010110100B)1000000010110100

C)1111111110110100C)0111111110110100

二、多项选择题

1.8位数11011011B可表示。

A)无符号数219B)-37的补码C)-36的补码

D)-36的反码E)91的原码F)-91的原码

三、填空题

1.计算机的硬件由、、、和等部分组成。

2.十进制68=B=Q=H。

3.[X]补=78H,则[-X]补=H。

4.通用编码字符集UCS的总体结构

由、、和构成四维编码空间,容量巨大。

四、计算题

1.已知[X]原=11001010,求X的反码、补码

2.用补码求[X+Y]补与[X-Y]补,并判断运算结果是否溢出

1)已知[X]原=10101100,[Y]补=11000110

2)已知[X]反=01110110,[Y]补=00100110

五、简答题

1.什么是微型机的硬件和软件?

2.什么是系统软件和应用软件?

习题2

一、判断题

1.CPU芯片中集成了运算器、寄存器和控制器。

()

2.存储单元的地址和存储单元的内容是一回事。

()

3.在执行指令期间,EU能直接访问存储器。

()

4.8086CPU从内存中读取一个字(16位)必须用两个总线周期。

()

5.8086CPU的一个总线周期一般由4个状态组成。

()

二、单项选择题

1.8086CPU的40根引脚中,有个是分时复用的。

A)21B)1C)2D)24

2.8086CPU工作在最大模式还是最小模式取决于信号。

A)

B)NMIC)MN/

D)ALE

3.8086CPU中EU和BIU的并行操作是级的并行。

A)操作B)运算C)指令D)处理器

4.8086CPU用信号的下降沿在T1结束时将地址信息锁存在地址锁存器中。

A)

B)

C)ALED)READY

三、多项选择题

1.微型计算机的基本结构包括。

A)运算器B)寄存器C)存储器D)CPUE)控制器

F)外设及接口G)总线

2.8086标志寄存器中控制为。

A)CFB)IFC)DFD)SFE)TFF)OFG)ZF

3.若AL=00H,BL=0FEH,执行ADDAL,BL后,为0的标志位有。

A)CFB)PFC)AFD)SFE)TFF)OF

G)ZFH)DFI)IF

4.8086CPU复位后,内容为0的寄存器有。

A)IPB)FRC)CSD)ESE)DSF)SS

5.当CPU读存储器时,为0电平的引脚有。

A)ALEB)

C)

D)

E)

F)

6.8086与8088相比,具有。

A)相同的内部寄存器B)相同的指令系统C)相同的指令队列

D)相同宽度的数据总线E)相同宽度的地址总线F)相同的寻址方式

四、填空题

1.和集成在一块芯片上,被称作CPU。

2.总线按其功能可分、和三种不同类型的总线。

3.存储器操作有和两种。

4.CPU访问存储器进行读写操作时,通常在状态去检测READY,一旦检测到READY无效,就在其后插入一个周期。

5.8086/8088CPU中的指令队列的长度分别为和字节。

6.当8086CPU的MN/MX引脚接电平,CPU处于最大模式,这时对存储器和外设端口的读写控制信号由芯片发出。

五、简答题

1.8086/8088CPU中有几个段寄存器?

其功能是什么?

2.什么是逻辑地址、物理地址、物理地址是如何求得的?

3.何谓8086/8088CPU最大模式和最小模式?

其关键区别是什么?

4.在最小模式时CPU访问内存储器,哪些信号有效?

5.在最小模式时,CPU访问I/O接口,哪些信号有效?

习题3

一、判断题

1.MOVAX,[BP]的源操作数物理地址为16d×(DS)+(BP)()

2.OUTDX,AL指令的输出是16位操作数。

()

3.不能用立即数给段寄存器赋值。

()

4.所有传送指令都不影响FR寄存器的标志位。

()

5.堆栈指令的操作数均为字。

()

6.段内转移指令执行结果要改变IP、CS的值。

()

7.REPE/REPZ是相等/为零时重复操作,其退出条件是:

(CX)=0或ZF=0。

()

二、单项选择题

1.寄存器间接寻址方式中,操作数在中。

A)通用寄存器B)堆栈C)存储单元D)段寄存器

2.寻址方式的跨段前缀不可省略。

A)DS:

[BP]B)DS:

[SI]C)DS:

[DI]D)SS:

[BP]

3.假设(SS)=2000H,(SP)=0012H,(AX)=1234H,执行PUSHAX后,=12H

A)20014B)20011HC)20010HD)2000FH

4.若要检查BX寄存器中的D12位是否为1,应该用指令。

A)ORBX,1000HB)TESTBX,1000H

JNZNOJNZYES

C)XORBX,1000HD)ANDBX,1000H

JZYESJNZYES

5.用BP作基址变址寻址时,操作数所在的段是当前。

A)数据段B)代码段C)堆栈段D)附加段

6.含有立即数的指令中,该立即数被存放在。

A)累加器中B)指令操作码后的内存单元中

C)指令操作码前的内存单元中C)由该立即数所指定的内存单元中

7.已知AL=56H,BL=34H,都是压缩BCD码,要执行二数相加,正确的指令是。

A)ADDAL,BLB)ADCAL,BLC)ADDBL,ALD)ADCBL,AL

DAADAADAADAA

8.执行下列指令后:

MOVAX,1234H

MOVCL,4

ROLAX,CL

DECAX

MOVCX,4

MULCX

HLT

(AX)=

A)8D00HB)9260HC)8CAOHD)0123H

9.下列程序:

NEXT:

MOVAL,[SI]

MOVES:

[DI],AL

INCSI

INCDI

LOOPNEXT

可用指令来完成该功能。

A)REPLODSBB)REPSTOSBC)REPESCASBD)REPMOVSB

10.设(AL)=-68,(BL)=86,执行SUBAL,BL指令后,正确的结果是。

A)CF=1B)SF=1C)OF=1D)ZF=1

三、多项选择题

1.下列指令中源操作数使用寄存器寻址方式的有。

A)MOVBX,BUF[SI]B)ADD[SI+50],BXC)SUBAX,2

D)CMPAX,DISP[DI]E)MULVAR[BX]F)PUSHCX

2.将累加器AX的内容清零的正确指令是。

A)CMPAX,AXB)SUBAX,AXC)ANDAX,0D)XORAX,AX

3.正确将字变量WORDVARR偏移地址送寄存器AX的指令是。

A)MOVAX,WORDVARRB)LESAX,WORDVARR

C)LEAAX,WORDVARRD)MOVAX,OFFSETWORDVARR

4.调用CALL指令可有。

A)段内直接B)段内间接C)短距离(SHORT)

D)段间直接E)段间间接

5.将AL中带符号数乘10送AL,正确的程序是。

A)ADDAL,ALB)ADDAL,AL

ADDAL,ALMOVBL,AL

ADDAL,ALADDAL,AL

ADDAL,ALADDAL,AL

ADDAL,ALADDAL,BL

C)MOVCL,4D)SALAL,1

MOVBL,ALMOVBL,AL

SAL,AL,CLSALAL,1

ADDAL,BLSALAL,1

ADDAL,BLADDAL,BL

6.在下列指令中,隐含使用AL寄存器的指令有。

A)SCASBB)XLATC)MOVSBD)DAAE)NOPF)MULBH

7.指令操作数可来自于。

A)存储器B)时序电路C)寄存器D)立即数E)控制器F)I/O接口

四、填空题

假设(DS)=3000H,(BX)=0808H,(30808H)=012AAH,(3080A)=0BBCCH,当执行指令

“LESDI,[BX]”后,(DI)=,(ES)=。

2.假设(BX)=0449H,(BP)=0200H,(SI)=0046H,(SS)=2F00H,(2F246H)=7230H则执行XCHGBX,[BP+SI]指令后,(BX)=。

3.执行下列指令序列后,完成的功能是将(DX,AX)的值。

MOVCX,4

NEXT:

SHRDX,1

RCRAX,1

LOOPNEXT

4.下列指令执行后,BX=。

MOVCL,3

MOVBX,4DABH

ROLBX,1

RORBX,CL

5.执行下列指令序列

MOVAL,80H

MOVBL,08H

CBW

IDIVBL

则AH=AL=。

五、阅读程序并回答问题:

START:

INAL,20H

MOVBL,AL

INAL,30H

MOVCL,AL

MOVAX,0

MOVCH,AL

L1:

ADDAL,BL

ADCAH,0

LOOPL1

HLT

问

(1)本程序实现什么功能?

(2)结果在哪里?

(3)用乘法指令MULBL编程并使结果不变。

(假设20H、30H端口输入的数据均为无符号数)。

六、编程题

1.编程检测50H端口输入的字节数据,若为正,将BL清0;若为负,将BL置为FFH。

2.寄存器DX和AX的内容构成32位数,DX内容为高16位,AX内容为低16位,编写程序段:

1)将该32位数左移两位,并将移出的高位保存在CL的低两位中;

2)将该32位数右移两位,并将移出的低位保存在BL的低两位中。

数据段中以变址寄存器SI为偏移地址的内存单元中连续存放着十个字节压缩型BCD码,编程求它们的BCD和,要求结果存放到AX中。

习题4

一、单项选择题

1.若主程序段中数据段名为DATA,对数据段的初始化操作应为。

A)MOVAX,DATAB)MOVAX,DATA

MOVES,AXMOVDS,AX

C)PUSHDSD)MOVDS,DATA

2..EXE文件产生在之后。

A)汇编B)编辑C)用软件转换D)连接

3.下列存储器操作数的跨段前缀可省略的是。

A)DS:

[BP]B)SS:

[BP]C)ES:

[BX]D)ES:

[SI]

4.执行下列指令:

STR1DW‘AB’

STR2DB16DUP(?

)

CONTEQU$-STR1

MOVCX,CONT

MOVAX,STR1

HLT

后寄存器CL的值是。

A)0FHB)0EHC)12HD)10H

5.把若干个模块连接起来成为可执行文件的系统程序是()

A)汇编程序B)连接程序C)机器语言程序D)源代码程序

6.使汇编程序执行某种操作的命令是()

A)变量B)指令C)伪指令D)宏指令

二、填空题

1.MOVAX,((VARLT6)AND40)OR((VARGE6)AND50),当VAR﹤6时,汇编结果源操作数为。

2.程序段VAR1DB?

VAR2DW20DUP(58H,2DUP(?

))

VAR3DB‘ABCD’

.

.

.

MOVAX,TYPEVAR1

MOVBX,TYPEVAR2

MOVCX,LENGTHVAR2

MOVDX,SIZEVAR2

MOVSI,LENGTHVAR3

AX=,BX=,CX=,DX=,SI=。

3.段定义伪指令语句用语句表示开始,以语句表示结束。

4.ARRAYDW10DUP(5DUP(4DUP(20H,40H,60H)))语句执行后共占字节存储单元。

5.汇编语句中,一个过程有NEAR和FAR两种属性。

NEAR属性表示主程序和子程序,FAR属性表示主程序和子程序。

6.DOS系统功能号应放在寄存器中。

7.子程序又称,它可以由语句定义,由语句结束,属性可以是或。

8.与指令MOVBX,OFFSETBUF功能相同的指令是。

9.MOVAX,9090H

SUBAX,4AE0H

JCL1

JOL2

JMPL3

上述程序执行后AX=,程序转向。

10.假设寄存器AX=1234H,DX=0A000H

MOVBX,0

MOVCX,BX

SUBCX,AX

SBBBX,DX

MOVAX,CX

MOVDX,BX

上述程序执行后AX=,DX=,程序功能是。

11.BUFDB45H,68H,7AH,35H,39H

┇

MOVDI,OFFSETBUF

MOVCX,5

MOVAL,’A’

CLD

RETSTOSB

该程序段执行后,BUF中的内容是,方向标志DF=

12.假设寄存器AX=5AH,CX=23H

┇

MOVDL,0

LOP:

SUBAX,CX

JCNEXT

JNCDL

JMPSHORTLOP

NEXT:

ADDAX,CX

HLT

上述程序段执行后AX=,DL=,用数学表达式指明程序功能:

。

三、程序填空题(每空只填一条指令)

下列程序段求数组FLD的平均值,结果在AL中。

请将程序填写完整(不考虑溢出)

FLDDW10,-20,30,-60,-71,80,79,56

MOVCX,8

XORAX,AX

R1:

ADDSI,2

LOOPR1

MOVCL,8

IDIVCL

HLT

已知数据段DAT单元存放某一数N(-6≦N≦6)下面的程序段用查表法求数N的平方值,结果送SQR单元,请将程序填写完整。

TABLEDB0,1,4,9,16,25

DATDBN

SQRDB?

LEABX,TABLE

MOVAL,DAT

JGENEXT

NEXT:

XLAT

MOVSQR,AL

HLT

四、编程题

1.从BUF开始的10个字单元中存放着10个4位压缩型BCD数,求BCD和,结果存放在RES开始的3个字节单元中,低位存放在前,高位存放在后。

要求子程序完成两个4位压缩型BCD数相加。

2.定义一条宏指令,它可以实现任一数据块的传送,只要给出源和目的数据块的首地址以及数据块的长度即可。

然后采用宏调用把BUF1开始的100个字节单元中的数据依次传送到BUF2开始的100个字节单元中。

3.在BUF开始的内存中存有100个字节数,要求奇数在前、偶数在后仍存放在BUF开始的100个字节单元中。

4.假设DATAX和DATAX+2单元存放双字P,DATAY和DATAY+2单元中存放双字Q,编程计算2P-Q,差在DX,AX中。

若OF=1,程序转OVERFLOW,否则转NOOVER。

(只写与要求有关的指令语句)

5.已知在数据区BUF1和BUF2分别存放20个字节数据。

编程检查两数据区中的数据是否相同。

若完全一致,则将标志单元FLAG置FFH,否则置0,并将第一次出现的不同数据的地址分别存放在ADDR1和ADDR2单元中。

(要求:

源程序格式完整)

习题5

一、判断题

1.存储容量1GB表示10的10次幂个存储单元。

()

2.CPU内部的高速缓存是一级Cache,CPU外部的高速缓存是二级Cache。

()

3.由DRAM构成的存储器所存储的信息不需要定时刷新。

()

4.8086系统的存储器中各段的大小固定为64KB,同时各段之间可以重叠。

()

5.堆栈操作所访问的段是由SS和ES所指定。

()

二、单项选择题

1.下列不是半导体存储器芯片的性能指标。

A)存储容量B)存储结构C)集成度D)最大存储时间

2.高速缓存由构成。

A)SRAMB)DRAMC)EPROMD)硬磁盘

3.堆栈操作时,段地址由寄存器指出,段内偏移量由寄存器指出。

A)CSB)DSC)SSD)ES

E)DIF)SIG)SPH)BP

4.由2K×1bit的芯片组成容量为4K×8bit的存储器需要个存储芯片。

A)2B)8C)32D)16

5.由2732芯片组成64KB的存储器,则需要块芯片和根片内地址线。

A)12B)24C)16D)14

6.安排2764芯片内第一个单元的地址是1000H,则该芯片的最末单元的地址是。

A)1FFFHB)17FFHC)27FFH4)2FFFH

7.读取一个非规则字,8086CPU需个总线周期。

A)1B)2C)4D)8

8.对内存单元进行写操作后,该单元的内容。

A)变反B)不变C)随机D)被修改

9.8086CPU向52H单元写入一个字,写入过程中

和A0的逻辑电平是。

A)0和0B)0和1C)1和0D)1和1

三、多项选择题

1.当8086CPU从偶地址字单元读/写一个字数据时,需要的总线周期数和选通信号是。

A)1个总线周期B)2个总线周期C)A0=0

D)BHE=0E)A0=0∨BHE=0F)A0=0∧BHE=0

2.外存储器包括。

A)软磁盘B)磁带C)SRAMD)BIOSE)硬磁盘F)光盘

3.读写存储器操作数时数据所在的段可由寄存器指出。

A)CSB)DSC)ESD)SS

4.若当前DS的内容为2000H,则偏移量为1000H单元的地址可表示为。

A)2000H.1000HB)21000HC)2000H∶1000HD)3000H

四、填空题

1.在分层次的存储系统中,存取速度最快、靠CPU最近且打交道最多的是存储器,它是由类型的芯片构成,而主存储器则是由类型的芯片构成。

2.逻辑地址为2000H:

1234H的存储单元的物理地址是。

3.取指令时,段地址由寄存器提供,偏移地址由寄存器提供。

4.8086CPU写入一个规则字,数据线的高8位写入存储体,低8位写入存储体。

5.8088可直接寻址的存储空间为KB,地址编码从H到H。

6.将存储器与系统相连的译码片选方式有法和法。

7.若存储空间的首地址为1000H,存储容量为1K×8、2K×8、4K×8H和8K×8的存储器所对应的末地址分别为、、和。

8.对6116进行读操作,6116引脚

=,

=,

=。

五、应用题

试用4K×8位的EPROM2732和2K×8位的静态RAM6116以及LS138译码器,构成一个8KB.的ROM、4KB的RAM存储器系统(8086工作于最小模式),ROM地址范围为:

FE000H~FFFFFH,RAM地址范围为:

00000H~00FFFH。

六、简答题

1.静态存储器和动态存储器的最大区别是什么?

它们各有什么优缺点?

2.以图5.8所示的存储器系统为例,设DS=0000H,试述CPU执行

MOVAX,[2000H]

MOVBX,[2001H]

两条指令的操作过程。

习题6

一、单项选择题

1.在给接口编址的过程中,如果有5根没有参加译码,则可能产生个重叠地址。

A)5B)5的2次幂C)2的5次幂D)10

2.8086CPU工作在总线请求方式时,会让出。

A)地址总线B)数据总线C)地址和数据总线D)地址、数据和控制总线

3.8086CPU在执行INAL,DX指令时,DX寄存器的内容输出到上。

A)地址总线B)数据总线C)存储器D)寄存器

二、多项选择题

1.外部设备的端口包括。

A)数据端口B)状态端口C)控制端口D)写保护口

2.CPU在数据线上传输的信息可能是。

A)数据B)状态C)命令D)模拟量

三、填空题

1.对I/O端口的编址一般有方式和方式。

PC机采用的是方式。

2.在PC系列微机中,I/O指令采用直接寻址方式的I/O端口有个。

采用DX间接寻址方式可寻址的I/O端口有个。

3.一个称为一个端口,8086共有个端口。

4.接口的基本功能是和。

5.数据的输入/输出指的是CPU与进行数据交换。

6.数据输入/输出的三种方式是、和。

7.CPU在执行OUTDX,AL指令时,寄存器的内容送到地址总线上,寄存器的内容送到数据总线上。

8.当CPU执行INAL,DX指令时,

引脚为电平,

为,

为。

四、应用题

1.有一个CRT终端,其输入/输出数据端口地址为01H,状态端口地址为00H,其中D7状态位为TBE,若其为1,则表示缓冲区为空,CPU可向数据端口输出新的数据,D6状态位为RDA,若其为1,则表示输入数据有效,CPU可从数据端口输入数据。

1)编程从CRT终端输入100个字符,送到RES开始的内存单元中;

2)编程从BUF开始的100个字节单元中的数据,送到CRT终端。

2.利用8237通道2,由磁盘输入32KB的一个数据块,传送至内存4000H开始的区域,采用块连续传送,不自动预置,外设的DREQ和DACK都为低电平有效,假设8237的地址为60H~6FH,写出初始化程序。

3.若时钟为5MHZ,8237采用压缩时序方式,试估计上题DMA传送32KB数据块在最理想情况下需要多少时间?

习题7

一、判断题

1.内部中断的优先权总是高于外部中断。

()

2.两片8259A级连后可管理16级中断。

()

3.8259A所管理的中断源中,优先级低的中断源不可能中断优先级高的中断服务子程序。

()

4.若8259A中断屏蔽字OCW1为00H,则8259A所管理的8级中断全被屏蔽.()

5.只要8259A所管理的中断源没有被屏蔽,则任何中断源的中断请求都能得到CPU的响应和服务。

()

6.在8259A特殊完全嵌套方式中,同级的中断可实现嵌套。

()

二、单项选择题

1.CPU响应INTR引脚上来的中断请求的条件之一是。

A)IF=0B)IF=1C)TF=0D)TF=1

2.断点中断的中断类型码是。

A)1B)2C)3D)4

3.在PC/XT机中键盘的中断类型码是09H,则键盘中断矢量存储在。

A)36H~39HB)24H~27HC)18H~21HD)18H~1BH

4.3片8259A级联起来,可管理级中断。

A)24B)23C)22D)20E)16F)15

5.若8259A工作在优先级自动循环方式,则IRQ4的中断请求被响应并且服务完毕后,优先权最高的中断源是。

A)IRQ3B)IRQ5C)IRQ0D)IRQ4

6.PC/XT机中若对从片8259A写入的ICW2是70H,则该8259A芯片的IRQ6的中断类型码是。

7.PC/XT机中若对从片8259A写入的ICW2是70H,