电子钟的课程设计.docx

《电子钟的课程设计.docx》由会员分享,可在线阅读,更多相关《电子钟的课程设计.docx(7页珍藏版)》请在冰豆网上搜索。

电子钟的课程设计

1电路总设计

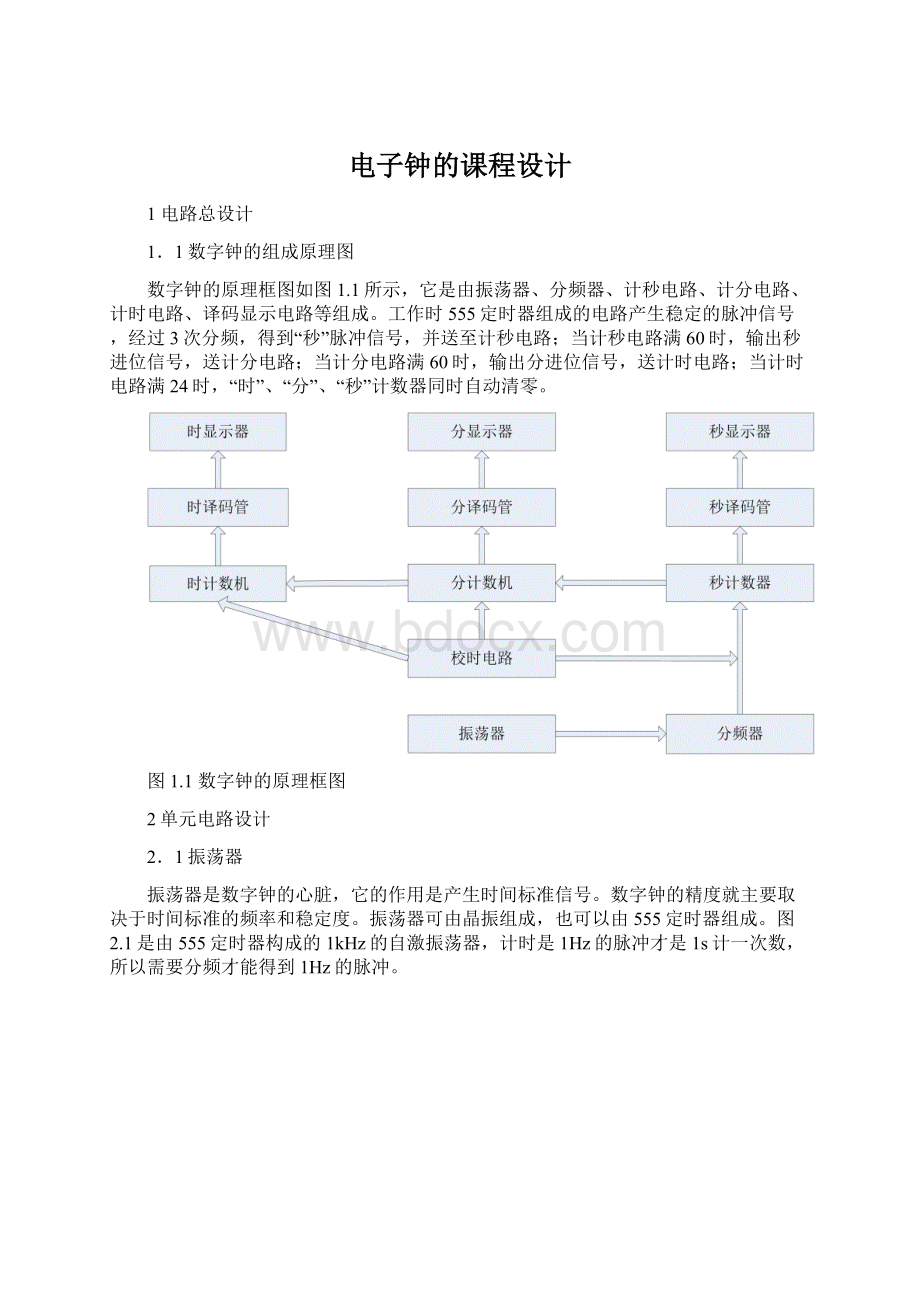

1.1数字钟的组成原理图

数字钟的原理框图如图1.1所示,它是由振荡器、分频器、计秒电路、计分电路、计时电路、译码显示电路等组成。

工作时555定时器组成的电路产生稳定的脉冲信号,经过3次分频,得到“秒”脉冲信号,并送至计秒电路;当计秒电路满60时,输出秒进位信号,送计分电路;当计分电路满60时,输出分进位信号,送计时电路;当计时电路满24时,“时”、“分”、“秒”计数器同时自动清零。

图1.1数字钟的原理框图

2单元电路设计

2.1振荡器

振荡器是数字钟的心脏,它的作用是产生时间标准信号。

数字钟的精度就主要取决于时间标准的频率和稳定度。

振荡器可由晶振组成,也可以由555定时器组成。

图2.1是由555定时器构成的1kHz的自激振荡器,计时是1Hz的脉冲才是1s计一次数,所以需要分频才能得到1Hz的脉冲。

图2.1振荡器

2.2分频器

分频器将7490接成10进制计数器,这样每过一级频率会变为原来的1/10。

如图2.2所示,经过3级分频后能得到1HZ的秒信号。

图2.2分频器

2.3计数器

(1)秒计数器:

秒信号发生器的精度和稳定度决定了时信号发生器和分信号发生器的精度。

“秒”计数器为60进制计数器。

60进制可通过十进制和六进制串联而成,从而完成数码显示。

可将两片7490接成60进制计数器,分(秒)个位片为10进制,十位片为6进制,如图2.3所示。

(2)分计数器

“分”计数器也是60进制计数器。

同“秒”计数器一样是由7490计数器设计构成。

图2.3秒、分计数器

(3)时计数器

先将两片7490接成30进制计数器,分(秒)个位片为10进制,十位片为2进制。

再用十位2进制(既0010)和个位4进制(既0100)通过与门联级起来反馈置0,则符合24进制计数,如图2.4所示。

图2.4时计数器

2.4校时电路

当时钟指示不准或停摆时,就需要校准时间。

校准的方法很多,但对校时电路的要求是,在进行小时校正时不影响“分”和“秒”计数器的正常计数,同理,进行校“分”位和校“秒”位的方法一样。

校时电路如图2.5所示。

图2.5.1校时方案一

图2.5.2校时方案二

3安装调试

3.1安装调试时采用的方法

(1)振荡器的安装和调试

按图电路连线,输出接发光二极管,观察发光二极管的显示情况。

(2)计数器的安装和调试

按图连线,分、秒计数器输出可接发光二极管,验证是否为六十进制计数器,如图3.1所示。

同理,可以验证二十四进制计数器,如图3.2所示。

图3.1秒、分计数器的仿真图

图3.2时计数器的仿真图

(3)校时电路的安装和调试

按图电路连线。

将电路输出接发光二极管。

推动开关,观察在CP作用下,输出端发光二极管的显示情况。

开关的不同状态,输出端输出频率比为1:

60。

3.2出现的问题及解决方法

(1)将校时电路接入后出现每到50就进位的现象,后用开关控制校时状态与时钟状态,分别进行忽布干扰,则电路正常工作。

(2)进行计数器仿真时,未到相应的时间就跳变,后改变线的连接,则电路正常。

4附图

5课程设计的总结与体会

在课程设计中,我们学习到了很多的东西:

首先,怎么样去查阅资料,收集与课设要用的有关的知识。

其次,要完成一件工作,还得专心致志才行,细心耐心。

第三,遇到困难要冷静,要多想解决办法,多尝试。

通过这次实验,我进一步熟悉数字电路的设计与特点,同时也基本上掌握了用555振荡器和74系列的集成对秒、分、时及其进位的实现。

而且让我了解了电路设计的基本思路,增强了实践动手能力,理论结合实际的能力加强。

数字钟的组成部分多,电路连接有些复杂,出现问题后分析起来比较困难,所以我们养成了完成一个部分就调试检验一个部分,确保正确才进行下一步工作,出现了问题只要在未检验的部分查寻就可以很快找出,效果很不错。

学生签名:

数字电子钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

此次设计与制作数字钟是为了了解数字电子钟的原理,从而学会制作数字电子钟。

而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。

在设计过程中,要灵活地运用到组合逻辑电路和时序逻辑电路的分析和设计,通过本次课程设计,我进一步学习和掌握各种组合逻辑电路与时序电路的原理与使用方法。

通过课程设计,使我加巩固和加深对电子电路基本知识的理解,学会查寻资料、方案设计、方案比较,以及单元电路设计计算等环节,进一步提高我综合运用所学知识的能力,提高分析解决实际问题的能力。

锻炼分析、解决电子电路问题的实际本领,通过此综合训练,为以后毕业设计打下一定的基础。

学生签名:

在本次综合电子课程设计中,我很荣幸和裴婧、喻扬帆分在一起,不仅仅是她们两学习好,这更激发了我的学习。

大家的互相配合的非常好,不仅了大家沟通交往,更是体现了各自的团队合作能力。

我们本次的课题是数字电子钟,它是一种典型的数字电路,何老师在指导设计时,提到我们这个课题需要从供电、显示、误差这三方面的技术参数来考虑,这正是给了我们各自的任务,相互协作。

在此次的数字电子钟设计过程中,更进一步地熟悉了芯片的结构及掌握了毕业设计的许多软件的使用方法。

同时在此次设计中,发现了很多要注意的地方和需改正的错误,例如:

在连接六十进制、二十四进制的进位及七进制的接法中,要求熟悉逻辑电路及其芯片各引脚的功能,那么在电路出错时便能准确地找出错误所在并及时纠正了。

在设计电路中,往往是先仿真后连接实物图,但有时候仿真和电路连接并不是完全一致的,例如仿真的连接示意图中,往往没有接高电平的脚以及接低电平的脚,因此在实际的电路连接中往往容易遗漏。

在设计电路的连接图中出错的主要原因都是接线和芯片的接触不良以及接线的错误所引起的。

因此仿真图和电路连接图还是有一定区别的。

学生签名:

参考文献资料

[1]毛期俭.数字电路与逻辑设计实验及应用.北京:

人民邮电出版社,2005

[2]吕思忠,施齐云.数字电路实验与课程设计.哈尔滨:

哈尔滨工程大学出版社,2003

[3]邓勇,周铎,邓斌.数字电路设计完全手册.北京:

国防科技大学出版社,2004.6

[4]赵淑范.数字电子钟的设计.长春大学学报,2004.8,14,4:

26-40

致谢

在此我们非常要感谢的是我的指导老师何海浪,感谢何老师的细心认真的辅导,和为我们提出了宝贵的意见和对数字电子钟设计中的一些修改。

这次课程设计能够顺利的完成,当然有我们的努力,但同时也离不开指导老师的答疑解惑。