实验四硬件电子琴电路设计.docx

《实验四硬件电子琴电路设计.docx》由会员分享,可在线阅读,更多相关《实验四硬件电子琴电路设计.docx(21页珍藏版)》请在冰豆网上搜索。

实验四硬件电子琴电路设计

《FPGA》课程报告设计题目:

学生班级:

学生学号:

学生姓名:

指导教师:

时间:

成绩:

硬件电子琴电路设计

一、实验目的:

学习利用数控分频器设计硬件电子琴实验。

二、实验原理:

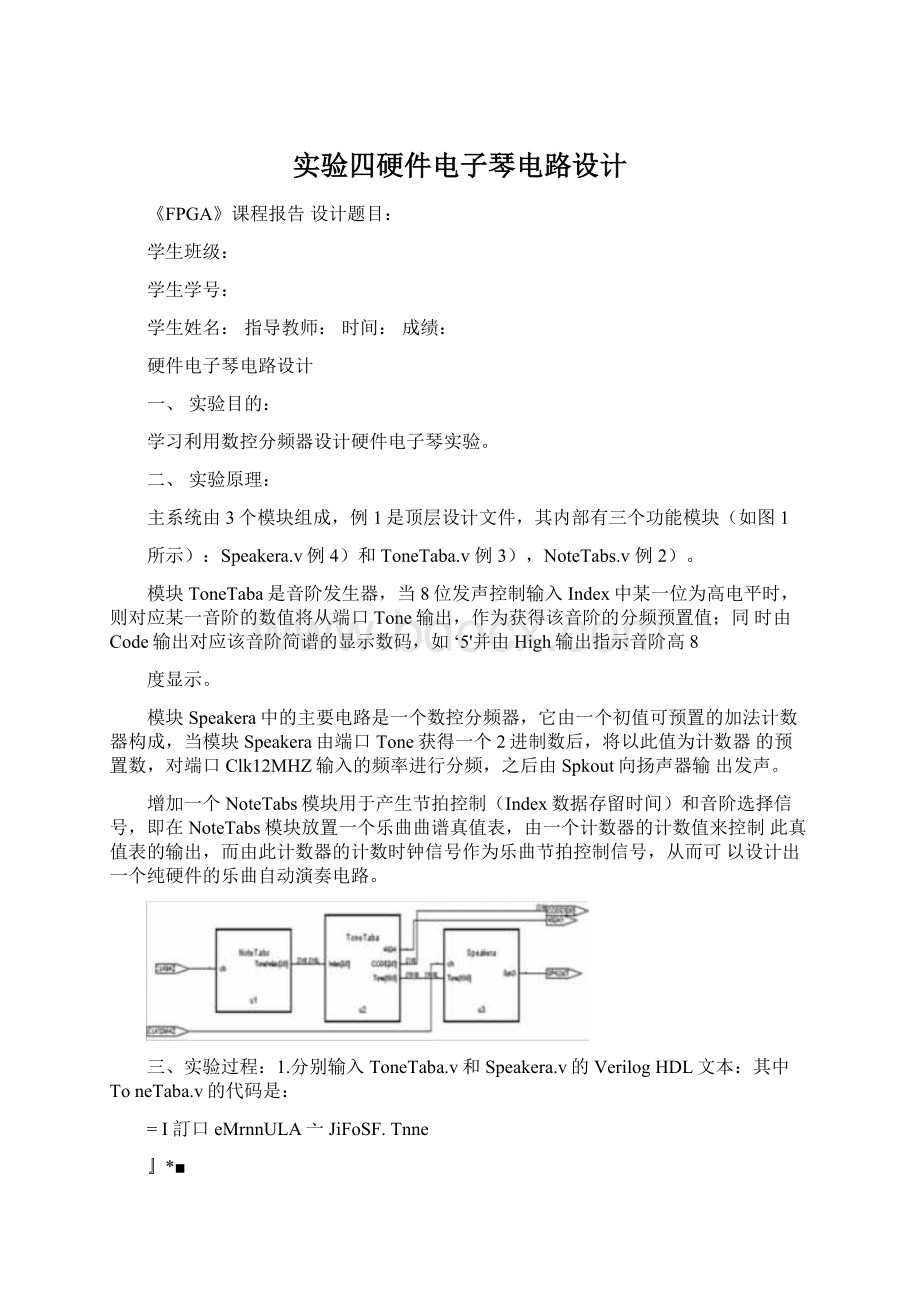

主系统由3个模块组成,例1是顶层设计文件,其内部有三个功能模块(如图1

所示):

Speakera.v例4)和ToneTaba.v例3),NoteTabs.v例2)。

模块ToneTaba是音阶发生器,当8位发声控制输入Index中某一位为高电平时,则对应某一音阶的数值将从端口Tone输出,作为获得该音阶的分频预置值;同时由Code输出对应该音阶简谱的显示数码,如‘5'并由High输出指示音阶高8

度显示。

模块Speakera中的主要电路是一个数控分频器,它由一个初值可预置的加法计数器构成,当模块Speakera由端口Tone获得一个2进制数后,将以此值为计数器的预置数,对端口Clk12MHZ输入的频率进行分频,之后由Spkout向扬声器输出发声。

增加一个NoteTabs模块用于产生节拍控制(Index数据存留时间)和音阶选择信号,即在NoteTabs模块放置一个乐曲曲谱真值表,由一个计数器的计数值来控制此真值表的输出,而由此计数器的计数时钟信号作为乐曲节拍控制信号,从而可以设计出一个纯硬件的乐曲自动演奏电路。

三、实验过程:

1.分别输入ToneTaba.v和Speakera.v的VerilogHDL文本:

其中ToneTaba.v的代码是:

=I訂口eMrnnULA亠JiFoSF.Tnne

』*■

WPJCr"烹Hesu

D專P8S301004盟

OJZPUXMMaE】

Dunpm『40+fiQ】mdsJ

Tns器5nc&^

晋QTU

百箱s§£HgzLI"L監Eu0-IadheKFlMErftQJL口

孟dKIhQexJI

**IS」・boOHoA■gm

■gl百

■■bollMI匕Bf営OQ••Eg*哼bsa*・su口2m

speakera.vsK;^^-

•■bela尸nSAOrp■■Elb-ri-r”■■bc«l;l3-ggIRn“be註口„ErriQMcl■■beflp"FA1.B叫rrlb口HMGyqLp■■rr苗四严誑

HM*令一】占lM駐匸一・sI门口ftAwlH.trmQCJocloloHT吕nmHOMDgilmMQn・A冒一一/&廿」)101口1lcHHO»?

^^-WM2soaMOMOHnsx*一二b1EO101£00HElsecb1HdtriQH1Do□口◎10YgeTlfPCH110C3H。

H8X4^^MMQSOSMMOHnKAiMM^MMOOMOMOHHOMOO^A—ITtrm00口吕口0rtffllMTtr醫01loccloQ-o

aoft*Aino^Aft

-—^OB■一3-E2】」■laGISAk普警n存。

席討:

一-4.■日吕qi』tu暮;i.*g—.占SQWJUQ切匸二g;蹲ph』:

■bseK苕冥■幕岂匸g」」—JnErQ口SJfLL也crA-^-ITiJJli託H—£卜0『

—.4二"I.占Q口一話曽弓{L总防sb.4^■tlcKZ*Klab具■HE1“味£t

■r*i4ilw"h*£001M岸3A.F1*bH*—"・■■«

Ho&prt5f:

rlJa片EHR(门Ik:

*TD口IT*5忙疔5inwtirlcllc":

mpllrfLlo“2Tcmmzoucpub5巧挥・"

mHmgPHeclm

9HrtQ呵匚一Isplcs"

HoHes3"0一counrtM

1】.reg〔10“OJCQUnrtll"

12r巾gCOLnlcz"

13reg5*O1C5“

14

14aJ-wa^m^-JPDSeclgeQllc》

16tregin

17iHl(caunc山¥11】XEnImPHeQLlcANl・tTl“

19ccmnrl血AM1*

hjoeyd

MHelseb-mgin

22pHecl片23counMAWCOUncm古•柑1“

B&

25end

27alwayag(posedge

23if(Count11>=11・HYFF)begin

29Count11<=Tone;

30FullSFkS<-1・bl;

31end

32elsebegin

33Countll<_Countll+lrbl;

34Full5p]c5<:

=0;

35end

36end

37

3Salways@(posedgeFullSpkS)begin

39Count2<—€0011^2;

40if(Count2=l・匕1)SpkS<=l'bl;

41elseSpfcS^l^O;

42end

43

44

45

4石endmodule

然后写testbench方针文件,进行方针:

ToneTaba.v的testbench文件代码是:

1'timescaleIns/Ips

2moduletestbench_ToneTaba;

3_

4//Inputs

5reg[3:

0]Index;

6

//Outputswire

wire

[3:

0]Code;High;

10

wire[10:

0]Tone;

11

12

//InsranriatetheUnitUnder

13

ToneTabauut(

14

•Index(Index)9

15

.Code(Code).

16

.High(High),

17

.Tone(Tone)

18

);

19

20

initialbegin

21

//InitializeInputs

22

Index=0;

23

24

//Wait100nsforglobal

25

#100begin

26

Index=0;

27

end

28

#100begin

29

Index=1;

30

end

31

#100begin

32

Index=2;

33

end

Test

reset

(UUT)

tofinish

tlOObegin

Index=3;end

#100begin

Index-E;end

f100begin

Index=7;end

#100begin

Index=8;end

#100begin

Index■9;end

#100begin

Index-10;end

#100begin

Index=12;end

#100begin

Index=13;end

f100beginIndex=15;

end

//Addstimulushere

end

endir.odule

仿真图形是:

Speakera.v的testbench文件代码是:

3

4

5

6

7

fl

9

10

1112

13

14

15

1617IS19NO2122

23

24

25

26272E

29

30

31

32

33

34

35

36

373S

I'tiitescaleIns/IpsmoduleEesubench_Spea)cera;

//Inputs

工亡gClk;

reg[10:

0]Tone;

//Outputs

wireSpkS;

//Ins匸arrtia/tErheUnitUnderTe:

sz(UUT)Speakersuut(

・Clk(Clk),

.Tone(Tone)t

・SpkS(5pXS)

initialbegin

//InitializeInpurs

Clk=0;

Tone■0;

//Wait100nsforglobalresettofinish#100begin

Clk=1;

Tone-20€7;

end

#100begin

Tone-1723;

end

#100begin

Ione■ices;

end

//Addstjjt.uIlibhere

end

en

仿真图形如下:

2•首先打开电脑上的记事本,按照COE文件的格式要求输入《梁祝》音乐,并存盘。

39J8

15

59362

i—l

_INITIALIZATION_RADIX二10;_INITIALIZATION_VECTOR=

3,3,3,5,5,5,6,8,8,

9,6,&5,5』12,12,12,

12,10,12,9,9,9,9t

0,9,9,9,10,匚7,

55,d&&9,9,

8.6,

5,6,8

5,5$

』5,5,10,IQ

10,12,

6,&5,5,

3,3,

5,6,

J玄

』6』6,5,6,

&Sj

‘12JO,9,9,10,

9,&&

3,3,3,3*8>8,8;&,6.5,3,5,6,8,5,5,

新建一个IPcore:

BMMFile

■;■!

・・;■・uafM・m・in・・』・・・r・・mii・w.・m・a;i・

^tnerator&ArcniteCtureWn£fV*vww^WWWH*WHWWWVWWWWWWWWWWWWWWWWWVWWI!

WWWWW

RIP(COREGenL._ll.1二WJlMEMFilt对Schematic

ImptemenUTiOnCOhttraintSFiltf*StateDpagram冋T总覺Emnj/.'j.T*srm

=*UierDoCumert

MVftrilogModule矽veri.QjT^stFixture陆『I4DLMccu.eQVHDLLibrary

5VmOLPackage

MoreInfo

5,

9』

S3

Filenamej

Mutic

Location:

EJFRGA.'20105381-sender

•Addtoproject

Carne

_AutQ^iQtiMELIdd_striaL

・SiiicElemerts

QConftparaton

一:

匚LUAr

--1MemoryEiernents

QBlockMemoryGeneratory27

匚DistritotedMemoryGe^e-at-r^34

勺DutlPortBlockM*moryv£_3

IS1Registers.ShiftersiPip^lining

Co™irmutiicati^jritT*Er.\Drkiflg

-'n^*HIfrAy^fifirA^rti^

jtitjrvInfo

*R*uk

W玳*

Cdncei

选择ReadOnly

存储器位宽:

Width为4,深度:

Depth为256按Next继续设定

訂刊佔QCort|qConlaclSinglePortBlockMemory

CornmnscirhhmnMw4e

«-PwtSrtlpuraiMi

ADDR

DOILTT»

怖Writ*

•R・强Only

—

厂MtnwySiui

1

mtgh|4

Wvii^ftangtt256

—

Dtptfl(2M

^shaRjungt2S4B570

CLK

1

i-Moat

PageSof4

钩选LoadInitFile

点击LoadFile•按键,装载初始文件Music.coe

点击Generate按键生成ROM的

IPCORE

输入NoteTabs.v文件,实现按照4HZ频率循环读取ROM的音乐节拍、频率信号。

2

moduleNateTabs(ClkfTanelndex,clr

□

4

}*

inp'jtCllcfclr;

5

dutp^jt[3:

0]Tonelndex;

巧

reg[7:

0]Counter;

7

always®(posedgeClkorposedgeclr)

S

if(clr)

9

CountezK—S*bOOOOOOOO;

10

else

11

begin

12

if{Counter>=138)Counter<=8rb0OOOOOOO;

13

elseCounte^^CounEer+l1bl;

14

end

15

Mu3zcu5(.addr(亡oun匸Et}”

16

17

・dout(Tonelndex^);

1S

endrr.odule

NoteTabs.v的testbench文件代码是:

7

B

9

10

11

12

13

14

15

16

17

IS

19

20

21

22

23

24

23

26

27

26

29

仿真图形如下:

|Ltirrescal^Ins/Ips

ireduletestbenchWoteTibs;

//Inputs

xegCllc;

reqclr;

//Outputs

wire[3:

0]Toneindex;

//InstantiatetheUnitUnderTest(UUT)NoteTabsuut(

.cik(cik),

.Toneindex(Tanelndex},

.clx(clr)

initialbegin

//InitializeInputs

Clk-0;

clr-0;

#40clr=l;

#40clr=0;

//Wait100nsforglobalreseutofinishforever#40ClJc=*Clk;

//AddBtimulushere

end

endiLodule

3.输入div_50_12M.v、div_50_4HZ.v的VerilogHDL文本:

其中div_50_12M.v

的代码是:

iLodulediv5012M(elk,elk12M,reset

inpLi匸clkfreset;outputclk_12M;reg[1:

01count;

regelk12M;parameterN=^;initial

count<=l;

always®(posedgeelk)begin

iflreset)

begincounc<=l;clk_12M<=0;end

elseif(count-=3)

clk_12M<—C1JC12M;coun匸c二2;

e^d

else

begin

eoLiii匸GuoLirrd;end

end

endnr.odjle

7

S

9

10

11

12

13

IT

15

1€

17

IS

19

20

21

22

23

24

25

26

27

23

div504HZ.v的代码如下:

5

6

7

S

9

10

11

12

13

14

15

1€

17

18

19

20

21

22

23

2弓

25

27

23

modulediv_50_4HZ(clkfclk_4HZ,reset);

incutelk,reset;

outputclk_4HZ;

reg[23:

0]count;

regclk_4HZ;

parairetezN=125OOO0O;

initial

count<=l:

always0(posedgeelk}

begin

if(reset)

begincount<=-l;clk_4HZ<=0;end

elseif(count==(N/2+1))begin

clk_4HZ<—alk_4HZ;count<-2;

end

else

begin

count<=count+1;

end

end

endmodule

div5012M.v的testbench文件代码是:

modulediv_12;

regclk_S0M=11b0;wirecllc_12M;

regresec;

仿真图像如下:

写顶层文件将上面的模块例化在一起:

2ooctidEmoa冒亡r口昶》上色百EE*色丄,日丄口話ifSpjfduu

3):

勺elJt_5DM;

$inpvtresets

4[3:

0]Ccde1;

outputfpkuut;

BwiEe(lOfO)Tiine;

5wireO;0jTonelndcx;

10wirecllr_^HZyClk_12M:

11Nor电Tat)日uOCCiir,,T0nelDd*K(Tonelndeatj,.clr[jflaerf\i

12ToneTabaul[・Index[ZaEielndex}t+Code(Codel)*.High*・Tone(Tone));

13Spealcerau2i.Cli(=1)£_12H)*.Tdm(Tane).Spt5-Spoilt});

14di¥_50_12MU3(ClDM,C1K_1JH.工七*亡匕||=

15div&04HZu4(dkSOM,elk4KZrn«»t>;

16en^jddul^

最后执行综合。

4•执行完上述步骤后,进行索引脚操作

锁引脚完成后,编辑、修改约束文件:

1:

StartofConstraintsgeneratedbyPACE

2

3tPACE:

StartofPACEI/OPinAssignrr.entB

4

5

NET叱1忙_500

NETT,Codel<0>

LOC-e匚却R;

"LOC="F12r,;

€

NETr-CodeL

□LOC="E15H;

7

NET"Codel<2>

”LOC-"Ell";

3

NET"Codel<3>

"LOC=nFllH;

9

NETh,Hig-hLr,

LOC=;

10

NET

LOC-"DIE";

11

NET吒口也W

LOC=nD7H;

12

13

#PACT:

Start

cfPACEAreaConstraints

14

15

♦PACE:

Starv

ofPACEProhibi匸Consrraints

17

#PACE:

Endof

ConstraintsgeneratedbyPAGE

1-o

5•生成下载配置文件,下载到开发板进行经行验证。

四、思考题:

1电路上应该满足哪些条件,才能用数字器件直接输出的方波驱动扬声器发声?

答:

电路上应当满足输出的频率在扬声器的工作范围之内,且驱动电流能够驱动扬声器。

2、如果演奏其他乐曲,程序应做哪些方面的改动?

答:

Music模块要改掉,改成相应乐曲的谱调。