篮球倒计时VHDL.docx

《篮球倒计时VHDL.docx》由会员分享,可在线阅读,更多相关《篮球倒计时VHDL.docx(15页珍藏版)》请在冰豆网上搜索。

篮球倒计时VHDL

EDA技术课程设计

课题:

篮球竞赛30s计时器设计

系别:

电气与电子工程系

专业:

电子信息工程

姓名:

陈振侠

学号:

123408101

指导教师:

梁成武

河南城建学院

2011年6月24日

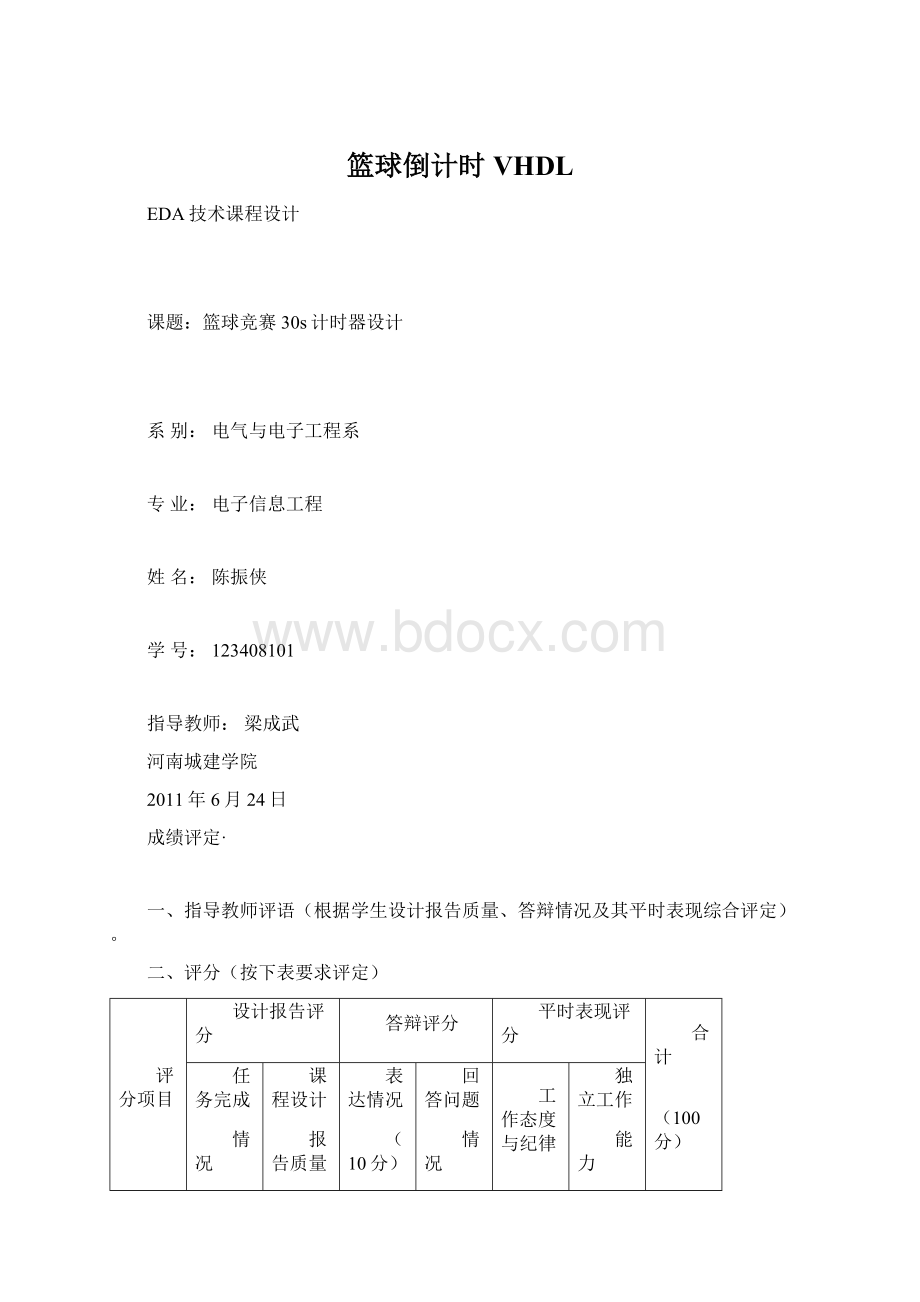

成绩评定·

一、指导教师评语(根据学生设计报告质量、答辩情况及其平时表现综合评定)。

二、评分(按下表要求评定)

评分项目

设计报告评分

答辩评分

平时表现评分

合计

(100分)

任务完成

情况

(20分)

课程设计

报告质量

(40分)

表达情况

(10分)

回答问题

情况

(10分)

工作态度与纪律

(10分)

独立工作

能力

(10分)

得分

课程设计成绩评定

一、设计目的

随着电子技术的高速发展和计算机技术的普遍应用,电子设计也越来越普遍地应用于整个电子行业中。

电子设计是人们进行电子产品设计、开发和制造过程中十分关键的一步,其核心就是电子电路的设计。

电子设计自动化(EDA)是在电子产品向更复杂、更高级,向数字化、集成化、微型化和低耗能方向发展过程中逐渐产生并日趋完善的电子设计方法,在这种方法中,设计过程的大部分工作(特别是底层工作)均由计算机自动完成,是电子技术发展历程中产生的一种先进的设计方法,是当今电子设计的主流。

在篮球比赛中,规定了球员的持球时间不能超过30秒,否则就犯规了。

本课程设计的“篮球竞赛30秒计时器”,可用于篮球比赛中,用于对球员持球时间30秒限制。

一旦球员的持球时间超过了30秒,它自动的报警从而判定此球员的犯规。

本课程设计是篮球竞赛30秒计时器。

此计时器功能齐全,显示30秒倒计时功能,系统设置外部操作开关可以直接清零、启动、暂停,同时应用了七段数码管来显示数值,可以方便地实现断点计时功能,当计时器递减到零时,还会发出光电报警信号。

本设计完成的中途计时功能,实现了在许多的特定场合进行时间追踪的功能,在社会生活中也具有广泛的应用价值.

二、设计要求

用EDA技术设计一个30s计时器,具体技术要求如下:

1、具有30s计时功能,并且能够实时显示计数结果。

2、设有外部操作开关,控制计数器实现直接清零、启动以及暂停/连续工作等操作。

3、计时器为30s递减计时,计时间隔为1s。

4、计时器递减计时到零时,数码显示器不能灭灯,同时发出光电报警信号。

三、总体设计原理与内容

1、设计的总体原理

本设计为30秒计数器,它主要由外部开关,控制电路,秒脉冲发生器,计数器,译码器和报警电路组成。

各部分相互联系,共同协作,实现电路功能。

各部分关系框图如图3-1所示:

图3-1总体框图

2、设计内容

本设计为30秒计数器,它主要分为三个部分:

计数部分,显示部分和控制部分。

其中计数器和控制电路是系统的主要部分。

计数器完成30s计时功能,而控制电路具有直接控制计数器的启动计数、暂停/连续计数、译码显示电路的显示功能。

为了满足系统的设计要求,在设计控制电路时,应正确处理各个信号之间的时序关系。

在操作直接清零开关CLR时,要求计数器清零,数码显示器不灭灯。

清零开关不工作时置数键才有效,置数键PLD为1时,同时计数器完成置数功能,译码显示电路显示“30”字样;当启动开关为高电平时,计数器开始计数;为了简单起见,我们将暂停与连续的控制与开始用一个键控制。

当计数器减到0时,启动报警系统,报警指示灯亮进行报警。

通过控制脉冲信号的传送来达到相应的目的。

3、设计方案

本设计主要能完成:

显示30秒倒计时功能;系统设置外部操作开关,控制计时器的直接清零、启动和暂停/连续功能;在直接清零时,数码管显示器灭灯;计时器为30秒递减计时其计时间隔为1秒;计时器递减计时到零时,数码显示器不灭灯,同时发出光电报警信号等。

经分析我们可以用两种方案进行实现:

方案一:

用VHDL编码进行实现。

VHDL是一门硬件描述语言,可以实现各种组合电路及逻辑电路。

使用VHDL编码实现,可读性强,易于理解,可以在软仿,硬仿时,依次进行查看其正确性,还能提高自己的编码水平,利于EDA课程的学习与应用。

采用静态编码,先设计计数器进行计数,数值通过数码管显示电路进行显示。

设置CLOCK为1HZ,数值变化周期为1秒。

方案二:

也是采用VHDL编码进行实现,但采用的是动态扫描法,设置一个片选信号,分时复用扫描两个数码管。

这时就要设置两个时钟,因为1HZ的时钟频率太小了,会使得看到的效果不连续,十位与个位产生分离,效果不好。

可以另选一个频率1000HZ左右的时钟信号作为扫描时钟。

这种设计节约了能量,延长了数码管的寿命,但引入了片选信号,又增加了一个时钟,所以较第一种方案复杂。

方案三:

用原理图输入法进行实现。

用原理图书输入法也能实现,电路的仿真。

但原理图输入法只适合中小型电路,而且需要良好的数字电路基础与电路功底。

另外,原理图输入法,比较繁琐,不易于操作。

综合比较,选择第一种方案。

四、EDA设计及仿真

1、30S倒计时器源程序

1.计数模块

计数模块,采用和三十秒减计数。

计数间隔为1秒。

其程序如下所示:

------------------------------------------------------------------------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

-----------------------------------------------------------------------------------------------------

ENTITYCNT30IS

PORT(CLK,EN:

INSTD_LOGIC;

C0,C10:

OUTSTD_LOGIC_VECTOR(5DOWNTO0);------C0,C10表示十位和个位

ENDCNT30;

------------------------------------------------------------------------------------------------------

ARCHITECTUREbehavOFCNT30IS

BEGIN

PROCESS(CLK,EN)

VARIABLETMPA:

STD_LOGIC_VECTOR(3DOWNTO0);

VARIABLETMPB:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IFCLK'EVENTANDCLK='1'THEN-------------检测时钟上升沿

TMPB:

="0011";TMPA:

="0000";

IFEN='1'THEN-------检测是否允许计数(同步使能)

IFTMPA="0000"THEN

IFTMPB/="0000"THEN

TMPA:

="1001";

TMPB:

=TMPB-1;

ENDPROCESS;

C0<=TMPA;C10<=TMPB;

ENDbehav;

-----------------------------------------------------------------------------------------------------------------

2、显示模块源程序

显示部分采用七段数码管进行实现。

LED数码管及引脚图资料:

7段LED数码管是利用7个LED(发光二极管)外加一个小数点的LED组合而成的显示设备,可以显示0~9等10个数字和小数点,使用非常广泛。

这类数码管可以分为共阳极与共阴极两种,共阳极就是把所有LED的阳极连接到共同接点com,而每个LED的阴极分别为a、b、c、d、e、f、g及dp;共阴极则是把所有LED的阴极连接到共同接点com,而每个LED的阳极分别为a、b、c、d、e、f、g及dp,图中的8个LED分别与上面那个图中的A~DP各段相对应,通过控制各个LED的亮灭来显示数字。

我们采用共阴极接法,其图如下:

图4-1共阴极数码管连接图

输入相应的数值,对应驱动相关二极管点亮,显示相应的数值。

显示部分功能表如表4-1所示:

表4-1功能表

用数码管进行显示,需把各个数值译码后传输到数码管,分十位与个位分别进行显示,其程序如下:

PRO2:

PROCESS(DD)

BEGIN

CASEDDIS-----------------------------------------DD表示十位

WHEN"0000"=>S1<="0111111";--显示0

WHEN"0001"=>S1<="0000110";--显示1

WHEN"0010"=>S1<="1011011";--显示2

WHEN"0011"=>S1<="1001111";--显示3

WHEN"0100"=>S1<="1100110";--显示4

WHEN"0101"=>S1<="1101101";--显示5

WHEN"0110"=>S1<="1111101";--显示6

WHEN"0111"=>S1<="0000111";--显示7

WHEN"1000"=>S1<="1111111";--显示8

WHEN"1001"=>S1<="1101111";--显示9

WHENOTHERS=>S1<="0000000";

ENDCASE;

ENDPROCESS;

PROCESS(SS)

BEGIN

CASESSIS-------------------------------------------SS表示个位

WHEN"0000"=>S0<="0111111";--显示0

WHEN"0001"=>S0<="0000110";--显示1

WHEN"0010"=>S0<="1011011";--显示2

WHEN"0011"=>S0<="1001111";--显示3

WHEN"0100"=>S0<="1100110";--显示4

WHEN"0101"=>S0<="1101101";--显示5

WHEN"0110"=>S0<="1111101";--显示6

WHEN"0111"=>S0<="0000111";--显示7

WHEN"1000"=>S0<="1111111";--显示8

WHEN"1001"=>S0<="1101111";--显示9

WHENOTHERS=>S0<="0000000";

ENDCASE;

ENDPROCESS;

ENDA;

2、总源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

--------------------------------------------------------------------------------------------

ENTITYCNT30IS

PORT

(CLK,CLR:

INSTD_LOGIC;

PLD,ENB:

INSTD_LOGIC;-------PLD表示复位信号

WARN:

OUTSTD_LOGIC;

S1,S0:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));------------译码输出,S1为十位S0为个位

ENDCNT30;

--------------------------------------------------------------------------------------------

ARCHITECTUREAOFCNT30IS

SIGNALDD:

STD_LOGIC_VECTOR(3DOWNTO0);--------------DD表示十位

SIGNALSS:

STD_LOGIC_VECTOR(3DOWNTO0);-------------SS表示个位

BEGIN

PRO1:

PROCESS(CLK,CLR,ENB)

VARIABLETMPA:

STD_LOGIC_VECTOR(3DOWNTO0);

VARIABLETMPB:

STD_LOGIC_VECTOR(3DOWNTO0);

VARIABLETMPWARN:

STD_LOGIC;

BEGIN

IFCLR='1'THENTMPA:

="0000";TMPB:

="0000";TMPWARN:

='0';

ELSIFCLK'EVENTANDCLK='1'THEN

IFPLD='1'THEN

TMPB:

="0011";TMPA:

="0000";TMPWARN:

='0';-------------------------------赋初值

ELSIFENB='1'THEN

IFTMPA="0000"THEN

IFTMPB/="0000"THEN

TMPA:

="1001";

TMPB:

=TMPB-1;

ELSE

TMPWARN:

='1';

ENDIF;

ELSETMPA:

=TMPA-1;

ENDIF;

ENDIF;

ENDIF;

SS<=TMPA;DD<=TMPB;WARN<=TMPWARN;

ENDPROCESS;-----------------------------------------PROT2显示部分

PRO2:

PROCESS(DD)

BEGIN

CASEDDIS--------------------------------------十位显示部分

WHEN"0000"=>S1<="0111111";--显示0

WHEN"0001"=>S1<="0000110";--显示1

WHEN"0010"=>S1<="1011011";--显示2

WHEN"0011"=>S1<="1001111";--显示3

WHEN"0100"=>S1<="1100110";--显示4

WHEN"0101"=>S1<="1101101";--显示5

WHEN"0110"=>S1<="1111101";--显示6

WHEN"0111"=>S1<="0000111";--显示7

WHEN"1000"=>S1<="1111111";--显示8

WHEN"1001"=>S1<="1101111";--显示9

WHENOTHERS=>S1<="0000000";

ENDCASE;

ENDPROCESS;

PROCESS(SS)

BEGIN

CASESSIS--------------------------个位显示部分

WHEN"0000"=>S0<="0111111";--显示0

WHEN"0001"=>S0<="0000110";--显示1

WHEN"0010"=>S0<="1011011";--显示2

WHEN"0011"=>S0<="1001111";--显示3

WHEN"0100"=>S0<="1100110";--显示4

WHEN"0101"=>S0<="1101101";--显示5

WHEN"0110"=>S0<="1111101";--显示6

WHEN"0111"=>S0<="0000111";--显示7

WHEN"1000"=>S0<="1111111";--显示8

WHEN"1001"=>S0<="1101111";--显示9

WHENOTHERS=>S0<="0000000";

ENDCASE;

ENDPROCESS;

ENDA;

-----------------------------------------------------------------------------

2、源程序仿真结果及数据分析

(1)仿真结果

图4-2仿真结果部分波形图

图4-3仿真结果总体波形图

(2)数据分析

由仿真结果图可以看出:

先清零,再置数,置初始值为30,置数后,保持30,直至使能端ENB为高电平,等到上升沿的到来,开始计数,计数器减计数至零时,报警信号WARM变为高电平,发出报警信号。

但信号在FPGA器件内部通过连线和逻辑门时,都有一定的延时。

延时的大小与连线的长短和门单元的数目有关,同时还受器件的制造工艺、工作电压、温度等的影响。

此外,信号的高低电平转换也需要一定的过度时间。

由于存在这些因素的影响,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的“毛刺”,称为“冒险”现象。

可以通过改变设计来破坏毛刺的产生的条件,从而减少毛刺的发生。

例如,在数字电路设计中,常采用格雷码。

还可以利用D触发器消除毛刺。

但由于时间和条件的限制没有进行时延现象的消除,在本次设计中没有太大影响,但在以后的工作中是一定要避免的。

五、硬件实现

1、打开Quartus

软件,建立一个工程,将编写好的源代码加载进去进行仿真。

2、代码编译成功之后,进行功能仿真,首先建立波形文件,设置时钟参数;将波形文件保存好,进行软件仿真;

3、软仿真实现之后,要进行硬仿,即硬件实现。

硬件实现简单明了,可以清楚的看到实验的成功与否,而且真实可靠。

为了实现硬仿,我们先进行管脚绑定。

CLR,ENB,PLD分别由键8,键7及键6来执行,S1,S0分别由数码管8和数码管7来显示。

绑定情况如图4-4所示:

图4-4管脚绑定图

4、管脚绑定好之后,进行编译。

5、编译无误后,进行下载硬仿。

硬件电路选择模式6,数码管8和数码管7分别显示计数值的十位与个位。

键8,键7与键6分别代表清零,启动/暂停/连续与复位键。

加载结果如图4-5所示:

图4-5加载成功图

图4-6清零效果显示图

实验箱选择模式6.按下清零键,数码管清零,显示00,并且报警灯不亮。

图4-7复位效果显示图

释放清零键,按下复位键,显示预置数30,上图为显示效果。

图4-8硬件运行效果剪影

释放复位键,按下启动按钮,计数器开始减计数,计数周期为1秒。

图为计数器减至19时的效果。

图4-9光电报警示意图

计数器继续进行减计数,当减至0时出发光电报警信号进行报警。

并保持数码管不灭,保持0状态。

直至清零。

重复上述过程。

六、设计总结

1、设计过程中遇到的问题及解决方法

在此次设计中,我自己的动手能力有了显著的提高。

在软仿的时候一切都比较顺利,但硬仿的时候,却发现有一个不该报警的地方报警了,看程序也没错误,波形也没错误,刚开始怎么也找不出问题,后来我们感觉应该还是程序的问题,便从程序入手,在程序中又强调了一下,报警条件,结果硬仿正确了。

所以说,实验就要不断的尝试,VHDL是一门语言,语言有些时候不仅仅是语法这么简单,只有在不断地调试中才能取得成功。

在本次设计中,其实我们做了两种方案。

第二种方案没有详细提及,该方案采用的时动态扫描。

做完第一种方案之后,我们又进行了第二种方案的仿真,在硬仿时发现数码管不能正确显示,出现了乱码现象。

这让我们很是费解,软仿没有错误,试验箱也不可能有问题,这是什么原因呢?

我们思索了很久,也做了许多尝试,都没有成功。

后来忽然间看到模式指示数码管旁边有一个短路帽,这让我哦联想到电路实验中短路帽的转换,所以,我把短路帽从上方拿到了下方,结果就正确显示了。

还有一次,同学的显示怎么都成功不了,按了开始就变为0,完全看不到变化现象,我看了程序感觉没错,就觉得是不是时钟设置的问题,我把它的时钟频率调小之后,发现果真正确显示了。

2,设计体会

为期一周的EDA课程设计就要结束了,在这一周的实训中,我收获颇丰。

在此次课程设计之前我对QUARTUS软件已经有了接触,但却没有很深的了解。

在此次课程设计时我将梁老师上课的内容在复习理解的基础上有了深刻的理解,对VHDL语言也有了更加熟悉的认知。

更重要的是对实验箱的功能及应用更熟练了。

本次课程设计是运用VHDL语言将模拟电子技术基础和数字电子技术基础以及电工电子技术的内容相结合,在此次设计的过程中发现了自己对理论知识认识的不足还有在动手操作方面还欠缺锻炼,因此我在此次课程设计的时候加深对老师所教的内容进一步复习,并且在上机练习的时候我就更加加强了对实践的重视。

通过这次课程设计我还知道了在学习这条道路上我们不断要加强学习,还要有坚持不懈的学习精神。

要将理论知识与实践相结合,要用理论指导实践,用实践来验证理论,让我们学于所用。

在这次设计中,我学到了很多东西,尝试到了成功的喜悦,但也有不足的地方,时钟有一点延时,虽然不影响效果,但若能考虑到延时问题,这样既会让所设计的器件的功能更加完善。

报警采用的是光电报警,但若能再加上声报警就更完美了。

此次课程设计中我还更加体会到合作的重要性,要有协助精神,这样我们才能事半功倍!

这次设计比较成功,但是由于时间关系,还是有一些做的不够好的地方。

这次设计中得到了老师及同学们的大力帮助,在此衷心的感谢大家的指导与批评。

3、对设计的建议

课程设计是一次很好的实践机会,它可以让我们很好的将所学理论知识与具体实际相结合,在实践中检验理论,在忙碌中提高自己,所以我希望在以后的学习中可以得到更多的实践机会。

多做课程设计,最好可以提前给出题目,这样我们就可以做好充分的准备,甚至可以做出事物。

七、设计生成的电路图

见附图:

八、参考文献

[1]《数字电子技术基础》阎石主编 高等教育出版社

[2]潘松,黄继业.《EDA技术实用教程》[M].北京:

科学出版社,2002.

[3]康华光主编.《电子技术基础》(模拟部分).第四版.北京:

高等教育出版社,2001

[4]乔庐峰王志功《VHDL数字电路设计教程》电子工业出版社。

2005

[5]网络资源篮球30秒计时器XX文库

[6]网络资源计数器XX文库

附图:

图7-1总体电路图