#基于TMS320VC5402的语音信号采集系统设计.docx

《#基于TMS320VC5402的语音信号采集系统设计.docx》由会员分享,可在线阅读,更多相关《#基于TMS320VC5402的语音信号采集系统设计.docx(22页珍藏版)》请在冰豆网上搜索。

#基于TMS320VC5402的语音信号采集系统设计

湖北民族学院

信息工程学院

DSP课程设计报告书

题目:

基于TMS320VC5402的语音信号采集系统设计

专业:

电气工程及其自动化

班级:

0307406班

学号:

学生姓名:

指导教师:

黄勇

2010年6月25日

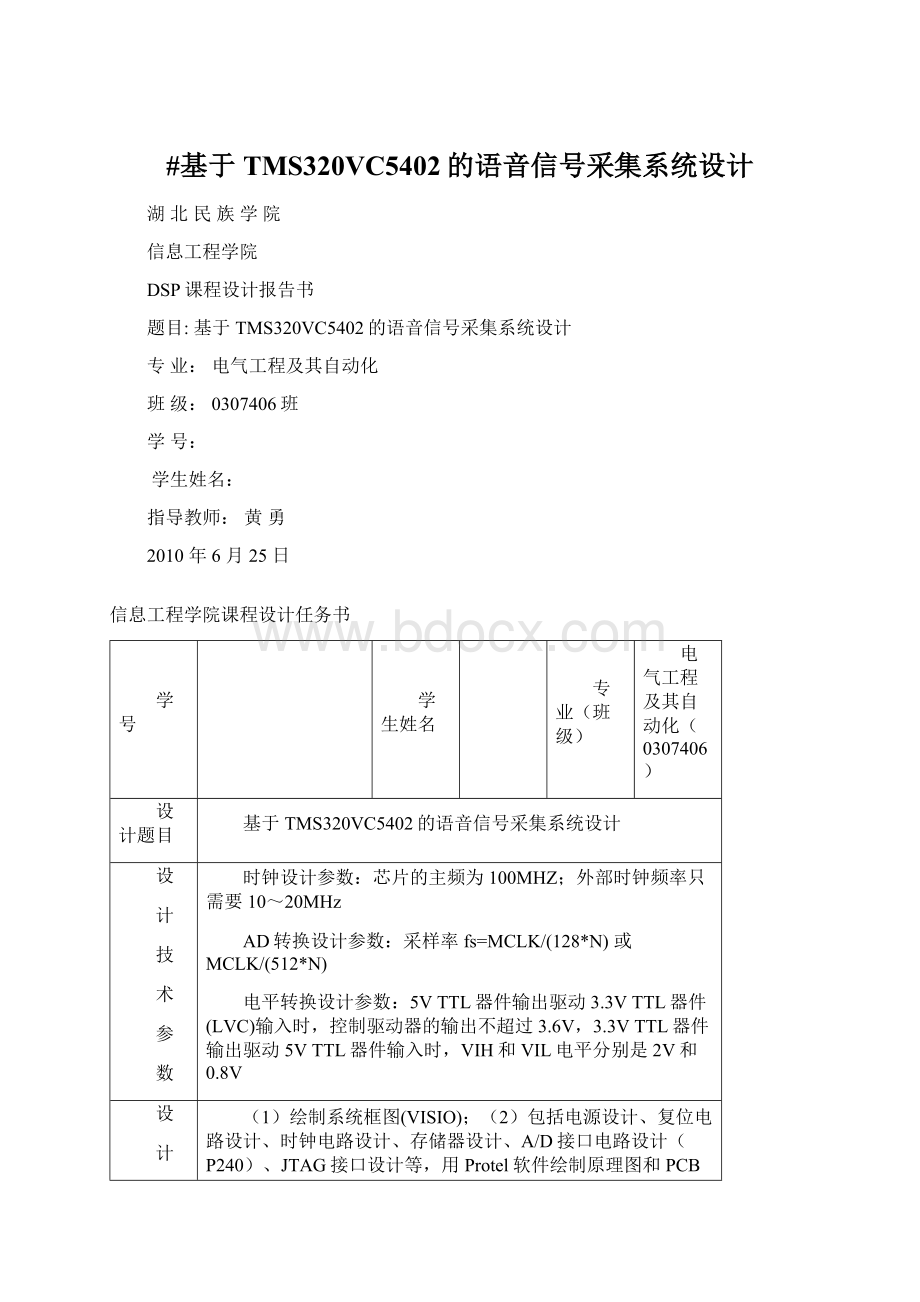

信息工程学院课程设计任务书

学号

学生姓名

专业(班级)

电气工程及其自动化(0307406)

设计题目

基于TMS320VC5402的语音信号采集系统设计

设

计

技

术

参

数

时钟设计参数:

芯片的主频为100MHZ;外部时钟频率只需要10~20MHz

AD转换设计参数:

采样率fs=MCLK/(128*N)或MCLK/(512*N)

电平转换设计参数:

5VTTL器件输出驱动3.3VTTL器件(LVC)输入时,控制驱动器的输出不超过3.6V,3.3VTTL器件输出驱动5VTTL器件输入时,VIH和VIL电平分别是2V和0.8V

设

计

要

求

(1)绘制系统框图(VISIO);

(2)包括电源设计、复位电路设计、时钟电路设计、存储器设计、A/D接口电路设计(P240)、JTAG接口设计等,用Protel软件绘制原理图和PCB图;(3)研究语音信号处理算法,并在MATLAB环境下仿真;

(4)给出程序流程图,编写初始化程序及数据处理程序;

工

作

量

7000字左右,图纸13张。

工

作

计

划

14周:

图书馆查阅相关资料;

15周:

系统总体设计构思;

16周:

系统详细设计;

17周:

整理形成设计报告。

参

考

资

料

[1] 杨进,李平,文玉梅,等.自适应供水管网泄漏检测定位仪器系统[J].

[2] 张勇,曾炽祥,周好斌,陈滨.TMS320C5000系列DSP汇编语言程序设计

[3] 杨进,文玉梅,李平.自来水铸铁管道泄漏声信号频率特征研究[J].

[4] 胡剑波,徐盛.数字信号处理系统的应用和设计[M].

[5]刘益成。

TMS320C54xDSP应用程序设计与开发。

指导教师签字

年月日

学生姓名:

学号:

专业(班级):

0307406班

课程设计题目:

基于TMS320VC5402的语音信号采集系统设计

指导教师评语:

成绩:

指导教师:

年月日

信息工程学院课程设计成绩评定表

摘要

在研究数字信号处理的基础上,提出了一个基于DSPTMS320VC5402和A/D转换芯片TLC320AD50的语音信号采集系统的设计。

给出了该系统的总体设计方案,具体硬件电路,包括系统电源设计、复位电路设计、时钟电路设计、存储器设计、A/D接口电路设计、JTAG接口设计、DSP与A/D芯片的连接等,以及软件流程图。

实验表明:

所设计的基于DSP的硬件和软件系统是一个很好的语音信号采集系统,该系统结构清晰,电路简洁,易于实现。

关键词:

语音信号;数据采集;DSP;TLC320AD50

Abstract

Inthestudybasedondigitalsignalprocessing,proposedadesignbasedonDSPTMS320VC5402andA/DconverterchipTLC320AD50speechsignalacquisitionsystem.Givestheoveralldesignschemeofthesystem,thehardwarecircuitincludingthesystempowersupplydesign,theresetcircuitdesign,clockcircuits,memorydesign,A/Dinterfacecircuit,JTAGinterfacedesign,theconnectionsofDSPandA/Dchipandsoon,andsoftwareflowchart.Experimentsshowthat:

thedesignbasedonDSPhardwareandsoftwaresystemsisanexcellentvoicesignalacquisitionsystem,thesystemstructureisclear,thecircuitissimpleandeasytoachieve.

Keywords:

Voicesignal;DataAcquisition;DSP;TLC320AD50

1任务提出与方案论证

20世纪50年代以来,随着数字信号处理各项技术的发展,语音信号处理技术得到不断提高,语音合成、语音识别、语音记录与语音控制等技术已开始逐步成熟并得到应用。

在语音信号处理过程中,要实现语音信号处理技术的精确性、实时性目的,语音信号采集和无误差存储成为语音信号处理中的前提。

TMS320VC5402是TI公司推出的定点数字信号处理器,它采用修正的哈佛结构,包括1个程序存储总线、3个数据存储总线和4个地址总线,这种结构允许同时执行程序指令和对数据操作,运行速度快,单周期定点指令执行时间为10ns,远高于语音信号采集和处理的要求。

在语音信号采集中,模拟信号向数字信号转换(ADC)的精度和实时性对后续信号处理过程起到了重要作用。

设计中采用TLC320AD50完成语音信号的A/D转换。

TLC320AD50是TI公司提供的一款16bit同步串口A/D和D/A转换芯片,ADC之后有1个抽取滤波器以提高输入信号的信噪比,其采样频率最高可达22.5Kb/s,满足语音信号处理中关于采样频率的要求。

1.1TMS320VC5402介绍

TMS320VC5402是基于一个先进的哈佛结构:

一个指令存储总线和三个数据存储总线。

此处理器提供一个具有高平行度的算术逻辑单元、特殊功效的硬件逻辑、片上存储器和附加的外围芯片。

操作灵活和快速的DSP原理及专用的指令系统。

独立的程序和数据空间允许他同时并行地访问指令和数据,提供了高度的平行性。

在一个独立的周期内可以同时执行一次写操作和两次读操作。

并行的指令存储和特殊功用的指令都可以完全的被在一个机器周期内执行。

数据可以在程序空间或数据空间内传输(见图1.1-1输入输出时序图)。

这一并行操作是算术、逻辑以及二进制运算的强大的机制。

另外,C5402还包括控制机制从而可以处理中断、循环、程序调用。

图1.1-1输入输出时序图

C5402设备提供片上ROM和RAM来帮助系统完成执行任务和系统的综合。

C5402映射到片上一块4K×16bitROM。

用户可以根据自己的需要来设置ROM的编程实现自己应用目的。

安全选项可以用来保护自定义的ROM。

系统的引导可以在C5402的片上ROM中利用。

这段引导程序在上电时可以主动的把用户代码程序从片外存储器中装载进来。

但如果引脚MP/MC在硬件复位时被采样低电平,那么程序将从ROM的FF8h0处开始执行。

这个区域包含了启动引导程序的分支指令。

C5402引导提供了不同装载程序的方法以便适应不同系统的需求:

并行的8位时16位EPROM并行的8位I/O空间或16位模式8位或时16位的串口模式主机端口引导。

图1.1-2TMS320VC5402的引脚图

中断和陷阱向量都被定义地址到程序空间。

这些向量是软的---也就是说当遇到陷阱时,处理器的PC装入陷阱向量从而让处理器去处理向量位置处的程序。

每个向量地址都有四个字空间被保留,以便适应延迟的分叉指令,不管是一字指令还是两字指令,只要是允许中断分支服务与正常的服务。

在系统复位时,复位、中断和陷阱向量都被映射到程序地址空间FF80h。

然而,这些向量可以被重新映射到128字页的程序空间当系统复位时。

这将pmtr寄存器装载中断向量标志位被完成。

在完成装载IPTR之后,任何用户中断或陷阱向量将会被映射到新的128数字的页面上来。

C5402在程序空间规划时用一个可扩展的页存储器,它允许访问1024K的程序存储器空间数据存储器空间用于存储需要程序处理的数据或程序处理后的结果。

通过对处理器方式状态寄存器PMST的DROM位的设置,将片内ROM配置在数据存储器空间(DROM=1),这样,可以用指令将片内ROM作为数据存储器中的数据ROM来读取。

复位时,DROM位被清0;64K字的数据存储器空间包括数据存储器映像寄存器,0000H~001FH是常用的CPU寄存器地址,0020H~005FH是片内外设寄存器的地址。

I/O空间用于与外部存储器映像的外设接口,也可以用于扩展外部数据存储空间,除程序存储器空间和数据存储器空间外,C54x系列器件还提供了I/O存储器空间,利用I/O空间可以扩展外部存储器。

I/O存储器空间为64K字(0000h~FFFFh),有两条指令PORTR和PORTW可以对I/O存储器空间操作,读写时序与程序存储器空间和数据存储器空间有很大不同。

TMS320VC5402存储器分配情况如图1.1-3存储器分配图所示,当存储空间超过64K之后,TMS320VC5402采用了分页机制,进行程序扩展见图1.1-4存储器分页机制所示。

图1.1-3存储器分配图

图1.1-4存储器分页机制

1.2TLC320AD50介绍

TLC320AD50(以下简称AD50)是TI生产的多媒体音频编解码器芯片,它集成了16位A/D和D/A转换器,采样速率最高可达22.05KHz,其采样速率可通过DSP编程来设置。

在AD50内部ADC之后有抽样滤波器,以提高输入信号的信噪比,在DAC之前有插值滤波器,以保证输出信号平滑。

AD50内部有7个数据和控制寄存器,用于编程设置它们的工作状态。

由于语音信号的频率范围在200Hz~23400Hz之间,采样率一般设定为8kHz,所以用AD50做AD转换器非常合适。

AD50的工作方式和采样频率均通过串口编程来实现。

由于转换的数据和控制数据是通过同一串行口进行传输的,所以AD50中有首次通信和二次通信。

首次通信专用于转换数据的传送,其时序如图2所示。

二次通信则用来设置和读出寄存器的值,所有的寄存器都在二次通信时编程。

启动二次通信有两种方法,一种是在FC上加高电平,第二种是将15位方式在首次通信的DIN的LSB位置为1。

AD50完成语音信号采集后,在DSP中进行相应的处理算法,语音信号经处理再从AD50输出。

2总体设计

基于TMS320VC5402的语音信号采集系统的结构如图2–1所示,该系统的中央处理单元采用美国TI(德州仪器)公司的高性能定点数字信号处理芯片TMS320VC5402,TMS320VC5402是TI公司推出的定点数字信号处理器,它采用修正的哈佛结构,包括1个程序存储总线、3个数据存储总线和4个地址总线,这种结构允许同时执行程序指令和对数据操作,运行速度快,单周期定点指令执行时间为10ns。

在语音信号采集中,模拟信号向数字信号转换(ADC)的精度和实时性对后续信号处理过程起到了重要作用。

设计中采用TLC320AD50完成语音信号的A/D转换。

TLC320AD50是TI公司提供的一款16bit同步串口A/D和D/A转换芯片,ADC之后有1个抽取滤波器以提高输入信号的信噪比,其采样频率最高可达22.5Kb/s,满足语音信号处理中关于采样频率的要求。

图2-1系统结构框图

2.1DSP核心模块的设计

TMS320VC5402是整个数据采集系统中,核心处理部分。

把缓存器的数据转存到海量存储器中,并对CPLD逻辑的工作方式,工作时钟进行控制,同时还完成与上位机的通信。

TMS320VC5402有20根地址线,16根数据线,可以寻址1M的地址空间,在这里,选用TMS320VC5402的数据空间用做SRAM的扩展,选用TMS320VC5402的I/O空间用做FLASH扩展。

DSP核心模块充当整个系统的CPU的功能,除了承担对A\D转换器送来的信号做相应的处理之外,还驱动RS-232串行通信链路将相应的数据及时的传到上位机上以备做之后的相关处理或计算,这就要求DSP芯片的处理能力相当的强大和速度必须与ADC相匹配,这一点TMS320VC5402完全有能力做到。

2.2A\D转换模块

A\D转换模块是整个系统的主要部分,它接收来自外部的信号或模拟数据,然后经过处理转换成数字信号传递给CPU做后续的处理。

设计中采用TLC320AD50完成语音信号的A/D转换。

TLC320AD50是TI公司提供的一款16bit同步串口A/D和D/A转换芯片,ADC之后有1个抽取滤波器以提高输入信号的信噪比,其采样频率最高可达22.5Kb/s,满足语音信号处理中关于采样频率的要求。

TLC320AD50(以下简称AD50)是TI生产的多媒体音频编解码器芯片,它集成了16位A/D和D/A转换器,采样速率最高可达22.05KHz,其采样速率可通过DSP编程来设置。

在AD50内部ADC之后有抽样滤波器,以提高输入信号的信噪比,在DAC之前有插值滤波器,以保证输出信号平滑。

AD50内部有7个数据和控制寄存器,用于编程设置它们的工作状态。

由于语音信号的频率范围在200Hz~23400Hz之间,采样率一般设定为8kHz,所以用AD50做AD转换器非常合适。

AD50的工作方式和采样频率均通过串口编程来实现。

由于转换的数据和控制数据是通过同一串行口进行传输的,所以AD50中有首次通信和二次通信。

首次通信专用于转换数据的传送,其时序如图2所示。

二次通信则用来设置和读出寄存器的值,所有的寄存器都在二次通信时编程。

启动二次通信有两种方法,一种是在FC上加高电平,第二种是将15位方式在首次通信的DIN的LSB位置为1。

AD50完成语音信号采集后,在DSP中进行相应的处理算法,语音信号经处理再从AD50输出。

3详细设计

由系统结构框图可知,系统主要包括实现模/数转换的A/D模块、掉电时存放程序的Flash模块、为DSP提供电源的外部电源模块、时钟模块,复位电路模块、实现程序下载的JTAG接口模块以及外接扩展存储器等几个部分.系统结构框图如图2-1所示。

本章将详细介绍各模块的硬件设计以及软件设计。

3.1硬件设计

3.1.1DSP芯片

作为DSP家庭高性价比代表的16位定点DSP芯片,C5402适用于语音通信等实时嵌入应用场合。

与其它C54X芯片一样,C5402具有高度灵活的可操作性和高速的处理能力。

其性能特点如下:

操作速率可达100MIPS;具有先进的多总线结构,三条16位数据存储器总线和一条程序存储器总线;40位算术逻辑单元(ALU),包括一个40位桶形移位器和两个40位累加器;一个17×17乘法器和一个40位专用加法器,允许16位带/不带符号的乘法;整合维特比加速器,用于提高维特比编译码的速度;单周期正规化及指数译码;8个辅助寄存器及一个软件栈,允许使用业界最先进的定点DSPC语言编译器;数据/程序寻址空间为1M×16bit,内置4K×16bitROM和16K×16bitRAM;内置可编程等待状态发生器、锁相环(PLL)时钟产生器、两个多通道缓冲串口、一个与外部处理器通信的8位并行HPI口、两个16位定时器以及6通道DMA控制器且低功耗。

与C54X系列的其它芯片相比,C5402具有高性能、低功耗和低价格等特点。

它采用6级流水线,且当RPT(重复指令)时,一些多周期的指令就变成了单周期的指令;芯片内部RAM和ROM可根据PMST寄存器中的OVLY和DROM位灵活设置。

这些都有利于算法的优化。

3.1.2电源设计

为了降低芯片功耗,C54x系列芯片大部分都采用低电压设计,并且采用双电源供电,即内核电源CVDD:

采用1.8V,主要为芯片的内部逻辑提供电压,包括CPU、时钟电路和所有的外设逻辑;I/O电源DVDD:

采用3.3V,主要供I/O接口使用。

可直接与外部低压器件接口,而无需额外的电平变换电路。

DSP芯片采用的供电方式,主要取决于应用系统中提供什么样的电源。

在实际中,大部分数字系统所使用的电源可工作于5V或3.3V,本设计采用TI公司提供的双电源芯片:

TPS73HD318电源的最大输出电流为750mA,并且提供两个宽度为200ms的低电平复位脉冲。

电路图如图3.1-1所示。

图3.1-1由TPS73HD318芯片组成的双电源电路

3.1.3复位电路设计

TMS320VC5402的复位输入引脚RS为处理器提供了一种硬件初始化的方法,它是一种不可屏蔽的外中断,可在任何时候对TMS320VC5402进行复位。

当系统上电后,RS引脚应至少保持5个时钟周期稳定的低电平,以确保数据、地址和控制线的正确配置。

复位后(RS回到高电平),CPU从程序存储器的FF80H单元取指,并开始执行程序。

本设计采用由TPS3707-33组成的自动复位电路(如图3.1-2)。

图3.1-2由TPS3707-33芯片组成的自动复位电路

3.1.4时钟电路设计

时钟电路用来为’C54x芯片提供时钟信号,由一个内部振荡器和一个锁相环PLL组成,可通过芯片内部的晶体振荡器或外部的时钟电路驱动。

利用DSP芯片内部提供的晶振电路,在DSP芯片的X1、X2之间连接晶体振荡器。

使用芯片内部的振荡器在芯片的X1和X2/CLKIN引脚之间接入一个晶体,用于启动内部振荡器。

时钟电路图如图3.1-3。

C1=C2=20pF

图3.1-3时钟电路

3.1.5程序存储器扩展设计

FLASH存储器用以扩展程序存储器AT29LV1024是1M位的FLASH存储器FLASH存储器与EPROM相比,具有更高的性能价格比,而且体积小、功耗低、可电擦写、使用方便,并且3.3V的FLASH可以直接与DSP芯片连接。

地址线:

A0~A15;数据线:

I/O0~I/O15;控制线:

—片选信号;

—编程写信号;

—输出使能信号。

扩展连接图如图3.1-4。

图3.1-4程序存储器扩展电路

3.1.6数据存储器扩展设计

要实现语音数据和系统程序的存储,TMS320VC5402必须有外接扩展存储器。

TMS320VC5402的速度为100MI/s,为保证DSP运行速度,需要外部存储器的速度接近10ns。

系统选择ICSI64LV16作为外部存储器,其容量64K字×16bit。

其硬件连接图如图3.1-5所示。

图3.1-5数据存储器扩展电路

3.1.7JTAG接口设计

在系统中,通过JTAG测试口访问和调试DSP芯片。

JTAG是一种国际标准测试协议(IEEE1149.1兼容),针对现代超大规模集成电路测试、检验困难而提出的基于边界扫描机制和标准测试存取口的国际标准。

标准JTAG测试端口包括4个必选引脚和一个可选的异步JTAG的复位引脚TRST,分别是工作模式选择引脚TMS,串行数据输入引脚TDI,串行数据输出引脚TDO,端口工作时钟引脚TCK。

JTAG接口引脚连接如图3.1-6所示。

图3.1-6JTAG接口引脚连接图

3.1.8A/D接口电路设计

A/D转换模块是整个系统的主要部分,它接收来自外部的信号或模拟数据,然后经过处理转换成数字信号传递给CPU做后续的处理。

TLC320AD50是一款SIGMA-DELTA型单片音频接口芯片,通过串行口与DSP或其它设备通信。

它内部集成了16位的D/A和A/D转换器,采样速率最高可达22.05Kb/s,其采样速率可通过DSP编程来设置。

设置AD50时,串行通信数据最低为高电平。

在DAC之前有一个插值滤波器以保证输出信号平滑,ADC之后有一个抽取滤波器以提高输入信号的信噪比。

AD50的发送和接收可以同时进行。

参考AD50的产品手册文献,得出TMS320VC5402与TLC320AD50的连接方法如图3.1-7所示

图3.1-7TLC320AD50与TMS320VC5402串行口的连接

3.2软件设计

3.2.1MATLAB环境中的语音信号采集和处理仿真

MATLAB是美国MathWorks公司推出的一种面向工程和科学计算的交互式计算软件,在MATLAB环境中,可以通过多种编程方法驱动声卡实现对语音信号的采集和播放,它的信号处理与分析工具箱为语音信号分析提供了十分丰富的功能函数,利用这些功能函数可以快捷而又方便地完成语音信号的处理和分析.使用MATLAB语言编程可以将声音文件变换为离散的数据文件,然后利用其强大的矩阵运算能力处理数据,如数字滤波、傅里叶变换、时域和频域分析、声音回放以及各种分析图的呈现等等.下面给出一个MATLAB程序,读入一个采样频率为22.050kHz、16位单声道的WAV文件,然后播放并做语音信号的波形图、频谱图和倒谱图(见图3.2-1),具体程序如下:

[y,fs]=wavread('c:

\wav\wav1.wav');%读一个已保存的WAV语音文件

wavplay(y);%播放语音文件

t=(0:

length(y)-1)/fs;%计算语音播放时间

subplot(3,1,1);%确定语音波形的显示位置

plot(t,y);%画波形图

legend('波形图');

xlabel('时间(s)');%X轴的标题

ylabel('幅度');%Y轴的标题

x=fft(y.*hamming(length(y)));%加hamming窗快速傅立叶变换

fm=5000*length(x)/fs;%限定频率范围

f=(0:

fm)*fs/length(x);%确定频率刻度

subplot(3,1,2);%确定语音波形的显示位置

plot(f,20*log10(abs(x(1:

length(f)))+eps));%画频谱图

legend('频谱图');

xlabel('频率(Hz)');

ylabel('频谱幅度(dB)');

c=fft(log(abs(x)+eps));%倒频谱计算

ms1=fs/1000;

ms20=fs/50;

q=(ms1:

ms20)/fs;%确定倒频刻度

subplot(3,1,3);

plot(q,abs(c(ms1:

ms20)));%画倒谱图

legend('倒谱图');

xlabel('倒频(s)');

ylabel('倒频谱幅度');

图3.2-1MATLAB环境中做出的语音信号的波形图、频谱图和倒谱图

3.2.2系统软件设计

主程序流程图如图3.2-2。

图3.2-2主程序流程图

DSP初始化程序:

#include"timothy.h"

#include"math.h"

intsin_data[256];

inttri_data[256];

ioportintport9100;

ioportintport8000;

intkeycode=0x0000;//thecodenumberofthekey;

voidmain(void)

{

inti;

ST0=0x1800;

ST1=0x4800;//disableallmaskableinterrupt;

SWWSR=0x7fff;//nowaitcycle;

CLKMD=0x1007;

IFR=0xffff;

IMR=0x0007;

asm("RSBXINTM");//opentheinterrupt;

for(i=0;