体系结构实验手册.docx

《体系结构实验手册.docx》由会员分享,可在线阅读,更多相关《体系结构实验手册.docx(22页珍藏版)》请在冰豆网上搜索。

体系结构实验手册

实验1简单CPU设计

一.实验目的

设计实现简单CPU,熟悉并掌握指令结构,利用verilog编写各个子模块。

二.实验原理

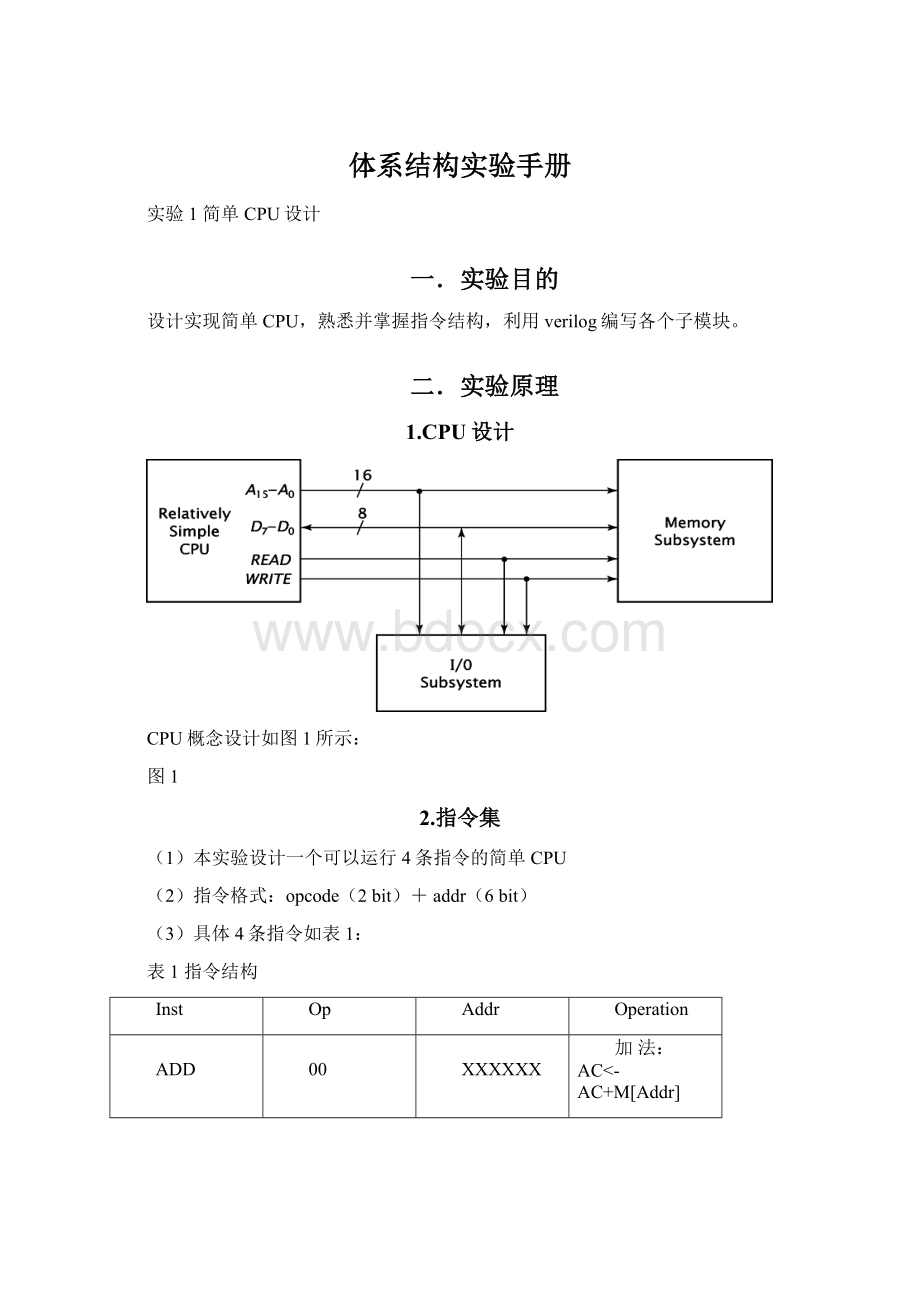

1.CPU设计

CPU概念设计如图1所示:

图1

2.指令集

(1)本实验设计一个可以运行4条指令的简单CPU

(2)指令格式:

opcode(2bit)+addr(6bit)

(3)具体4条指令如表1:

表1指令结构

Inst

Op

Addr

Operation

ADD

00

XXXXXX

加法:

AC<-AC+M[Addr]

AND

01

XXXXXX

逻辑与:

AC<-AC^M[Addr]

INC

10

XXXXXX

加1:

AC<-AC+1

JMP

11

XXXXXX

跳转:

PC<-Addr

3.寄存器组织

(1)累加器(AC)

a.提供ADD,AND操作的一个操作数

b.存放ADD,AND操作的结果

(2)用户不可见寄存器

a.地址寄存器(AR):

6bit,提供访问存储器单元地址

b.程序计数器(PC):

6bit,存放下一条指令在存储器单元中的地址

c.数据寄存器(DR):

8bit,存放从访问存储器单元的内容

d.指令寄存器(IR):

2bit,存放当前取出的指令的操作码部分

4.指令的执行

指令的执行过程如图2:

图2

(1)取指

FETCH1:

AR<-PC

FETCH2:

DR<-M,PC<-PC+1

FECTH3:

IR<-DR[7..6],AR<-DR[5..0]

(2)执行

ADD1:

DR<-M

ADD2:

AC<-AC+DR

AND1:

DR<-M

AND2:

AC<-AC^DR

INC1:

AC<-AC+1

JMP1:

PC<-DR[5..0]

(3)寄存器操作

AR:

AR<-PC;AR<-DR[5..0]

PC:

PC<-PC+1;PC<-DR[5..0]

DR:

DR<-M

IR:

IR<-DR[7..6]

AC:

AC<-AC+DR;AC<-AC^DR;AC<-AC+1

5.CPU数据通路

CPU数据通路设计如图3所示:

图3

图3是已经过简化的数据通路,它反映了CPU内部各单元的功能特点:

(1)AR只向存储器提供数据

(2)IR不向其他单元提供数据

(3)AC不向其他单元提供数据

(4)AC需保存ALU运算结果

(5)8bitBUS

6.控制器

(1)控制器功能

控制器是负责产生CPU内的各种信号,控制程序的执行:

1、取指令(fetch)

2、分析指令(decode)

3、执行指令(Execute)

4、其他功能:

控制程序数据的输入输出、异常处理、中断等

(2)控制信号

控制器中有9条信号线,分别是:

PCLOAD:

允许PC置值

PCINC:

允许PC自加1

DRLOAD:

允许DR置值

ACLOAD:

允许AC置值

ACINC:

允许AC自加1

IRLOAD:

允许IR置值

MEMBUS:

控制存储器是否输出

PCBUS:

控制PC是否输出

READ:

读存储器

(3)信号生成逻辑

1.控制信号的线性表达:

PCLOAD=JMP1

PCINC=FETCH2

DRLOAD=FETCH1vADD1vAND1

ACLOAD=ADD2vAND2

ACINC=INC1

IRLOAD=FETCH3

MEMBUS=FETCH2vADD1vAND1

PCBUS=FETCH1

READ=FETCH2vADD1vAND1

2.控制信号的生成逻辑,如图4:

图4

三.实验环境

软件:

QuartusII6,ModelSim

硬件平台:

GW48-SOPC/DSPEP1C6Q240

四.实验步骤

1.各个子模块的Verilog实现

(1)ALU模块

modulealu(op,a,b,c);

inputop;

input[7:

0]a,b;

output[7:

0]c;

assignc=(op==0)?

(a+b):

(a&b);

endmodule

(2)IR模块

moduleir(clk,load,din,dout);

inputclk,load;

input[1:

0]din;

output[1:

0]dout;

reg[1:

0]dout;

always@(posedgeclk)

begin

if(load)

dout=din;

end

endmodule

(3)DR模块

moduledr(clk,load,din,dout);

inputclk,load;

input[7:

0]din;

output[7:

0]dout;

reg[7:

0]dout;

always@(posedgeclk)

begin

if(load)

dout=din;

end

endmodule

(4)PC模块

modulepc(clk,rst,load,inc,din,dout);

inputclk,rst,load,inc;

input[5:

0]din;

output[5:

0]dout;

reg[5:

0]dout;

always@(posedgeclk)

begin

if(rst)

dout=0;

elseif(inc)

dout=dout+1;

elseif(load)

dout=din;

end

endmodule

(5)AR模块

modulear(clk,load,din,dout);

inputclk,load;

input[5:

0]din;

output[5:

0]dout;

reg[5:

0]dout;

always@(posedgeclk)

begin

if(load)

dout=din;

end

endmodule

(6)AC模块

moduleac(clk,rst,load,inc,din,dout);

inputclk,rst,load,inc;

input[7:

0]din;

output[7:

0]dout;

reg[7:

0]dout;

always@(posedgeclk)

begin

if(rst)

dout=0;

elseif(inc)

dout=dout+1;

elseif(load)

dout=din;

end

endmodule

(7)Control模块

modulecontrol(clk,rst,ir,

read,membus,

arload,

pcload,pcinc,pcbus,

drload,drbus,

alusel,

acload,acinc,

irload

);

parameterFETCH1=0;

parameterFETCH2=1;

parameterFETCH3=2;

parameterADD1=3;

parameterADD2=4;

parameterAND1=5;

parameterAND2=6;

parameterINC1=7;

parameterJMP1=8;

inputclk,rst;

input[1:

0]ir;

outputread,membus,

arload,

pcload,pcinc,pcbus,

drload,drbus,

alusel,

acload,acinc,

irload;

reg[3:

0]state,nextstate;

always@(posedgeclk)

begin

if(rst)

state<=FETCH1;

else

state<=nextstate;

end

always@(stateorir)

begin

case(state)

FETCH1:

nextstate<=FETCH2;

FETCH2:

nextstate<=FETCH3;

FETCH3:

begin

if(ir==0)

nextstate<=ADD1;

elseif(ir==1)

nextstate<=AND1;

elseif(ir==2)

nextstate<=INC1;

else

nextstate<=JMP1;

end

ADD1:

nextstate<=ADD2;

ADD2:

nextstate<=FETCH1;

AND1:

nextstate<=AND2;

AND2:

nextstate<=FETCH1;

JMP1:

nextstate<=FETCH1;

INC1:

nextstate<=FETCH1;

default:

nextstate<=FETCH1;

endcase

end

assignarload=(state==FETCH1||state==FETCH3)?

1:

0;

assignpcload=(state==JMP1)?

1:

0;

assignpcinc=(state==FETCH2)?

1:

0;

assigndrload=(state==FETCH2||state==ADD1||state==AND1)?

1:

0;

assignacload=(state==ADD2||state==AND2)?

1:

0;

assignacinc=(state==INC1)?

1:

0;

assignirload=(state==FETCH3)?

1:

0;

assignalusel=(state==AND2)?

1:

0;

assignmembus=(state==FETCH2||state==ADD1||state==AND1)?

1:

0;

assignpcbus=(state==FETCH1)?

1:

0;

assigndrbus=(state==FETCH3||state==ADD2||state==AND2||state==JMP1)?

1:

0;

assignread=(state==FETCH2||state==ADD1||state==AND1)?

1:

0;

endmodule

(8)三态门(6bit)模块

moduletri6(en,din,dout);

inputen;

input[5:

0]din;

output[5:

0]dout;

assigndout=(en)?

din:

6'bzzz_zzz;

endmodule

(9)三态门(8bit)模块

moduletri8(en,din,dout);

inputen;

input[7:

0]din;

output[7:

0]dout;

assigndout=(en)?

din:

8'bzzzz_zzzz;

endmodule

2.CPU模块的Verilog实现

modulecpu(clk,rst,data,read,addr,acout);

inputclk,rst;

input[7:

0]data;

outputread;

output[5:

0]addr;

output[7:

0]acout;

wire[7:

0]bus;

wire[5:

0]pcout;

wire[7:

0]drout,acout,aluout;

wire[1:

0]irout;

wirealusel,acload,acinc;

tri8t0(membus,data,bus[7:

0]);

arar1(clk,arload,bus[5:

0],addr);

pcpc1(clk,rst,pcload,pcinc,bus[5:

0],pcout);

tri6t1(pcbus,pcout,bus[5:

0]);

drdr1(clk,drload,bus[7:

0],drout);

tri8t2(drbus,drout,bus[7:

0]);

alualu1(alusel,acout,bus[7:

0],aluout);

acac1(clk,rst,acload,acinc,aluout,acout);

irir1(clk,irload,bus[7:

6],irout);

controlc1(clk,rst,bus[7:

6],

read,membus,

arload,

pcload,pcinc,pcbus,

drload,drbus,

alusel,

acload,acinc,

irload);

endmodule

3.InstMem模块的实现(用Altera的宏)

4.DataMem模块的实现(用Altera的宏)

5.顶层模块(系统:

CPU+指令Mem+数据Mem)用Schematic实现

6.引脚配置(要求引出。

。

。

。

)及测试数据

Clk信号,复位信号

7.测试

在quartus中,将cpu.v文件设置为顶层文件。

然后生成cpu和memery器件,建立一个block模板,在里面讲cpu和memery连接好,并配上相应的输入输出信号。

接着,编译工程。

然后建立一个wave文件,进行模拟仿真。

最后连接实验箱,进行仿真。

一.思考题

1、单周期CPU的控制器设计与实验1中控制器设计有何异同。

实验2单周期MIPS处理器设计

一、实验目的

设计实现是指令简单,容易译码的单周期MIPS处理器,设计实现单周期的MIPS处理器,熟悉并掌握指令结构,利用verilog编写各个子模块。

二、实验原理

1、MIPS的简单介绍

MIPS是世界上很流行的一种RISC处理器。

MIPS的意思是“无内部互锁流水级的微处理器”(Microprocessorwithoutinterlockedpipedstages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

MIPS技术公司是美国著名的芯片设计公司,它采用精简指令系统计算结构(RISC)来设计芯片。

和英特尔采用的复杂指令系统计算结构(CISC)相比,。

RISC具有设计更简单、设计周期更短等优点,并可以应用更多先进的技术,开发更快的下一代处理器。

MIPS是出现最早的商业RISC架构芯片之一,新的架构集成了所有原来MIPS指令集,并增加了许多更强大的功能。

2、单周期MIPS设计

单周期MIPS处理器的概念设计如图1所示:

图1单周期MIPS处理器的结构

3、指令集

本实验共有9条指令,每一条MIPS指令是一个32位的。

MIPS指令集中共包括三种格式的指令,分别是立即数(immediate)类型(I类型)指令,跳转(jump)类型(J类型)指令和寄存器(register)类型(R类型)指令。

指令集的这种设计方法简化了指令译码,一些复杂的很多使用的操作和寻址方式可以通过编译器利用一组简单指令来合成。

MIPS的指令格式如下所示:

(1)R类型指令

312625212016151110650

op

rs

rt

rd

shamt

func

6-bit5-bit5-bit5-bit5-bit6-bit

(2)I类型指令

312625212016150

op

rs

rt

immediate

6-bit5-bit5-bit16-bit

(3)J类型指令

3126250

op

Targetaddress

6-bit26-bit

指令格式中的op(opcode)是指令操作码。

rs(registersource)是源操作数的寄存器号。

rd(registerdestination)是目的寄存器号。

rt(registertarget)既可为源寄存器号,又可为目的寄存器号,由具体的指令决定。

func(function)被认为是操作码。

shamt(shiftamount)由移位指令使用,定义移位位数。

immediate是16位立即数,使用之前由指令进行O扩展或符号扩展。

26位Targetaddress由jump指令使用,用于产生跳转的目标地址。

R(register)类型的指令从寄存器堆中读取两个源操作数,计算结果写回寄存器堆。

I(immediate)类型的指令使用一个16位的立即数作为一个源操作数。

J(jump)类型的指令使用一个26位立即数作为跳转的目标地址(targetaddress)。

MIPS指令集具有以下特点。

①简单的LOAD/STORE结构。

②IPS指令集的指令格式非常规整,所有的指令均为32位,而且指令操作码在固定的位置上。

③易于编译器的开发。

一般地讲,编译器在编译高级语言程序时,很难用到复杂的指令。

MIPS指令的寻址方式非常简单,每条指令的操作也非常简单。

MIPS具体的指令结构:

表1指令结构

Instructionbitnumber

31..26

25..21

20..16

15..11

10..6

5..0

add

000000

rs

rt

rd

00000

100000

sub

000000

rs

rt

rd

00000

100010

and

000000

rs

rt

rd

00000

100100

or

000000

rs

rt

rd

00000

100101

slt

000000

rs

rt

rd

00000

101010

lw

100011

rs

rt

immediate

sw

101011

rs

rt

immediate

beq

000100

rs

rt

immediate

j

000010

Address

4、单周期MIPS处理器结构

每条指令1个时钟周期内完成。

三、实验环境

软件:

QuartusII6,ModelSim

硬件平台:

GW48-SOPC/DSPEP1C6Q240

四、实验步骤

1.各个子模块的设计和Verilog实现

(1)PC寄存器

PC(programcounter)是专用寄存器,CPU使用它从存储器中取指令。

每执行一条指令PC加4。

Clk为时钟信号,rst为复位信号。

PC寄存器的部分程序:

always@(posedgeclk)

begin

if(rst)//当有复位信号时,输出为0;

dout=32'h00000000;

else

dout=din;

end

(2)二选一的数据选择器

二选一的数据选择器电路框图如图二所示:

输入端是a、b,输出端为c,sel为控制端。

当sel为0时,输出端c输出a信号,当sel为1时,输出端c输出b信号,w为数据宽度参数。

程序为:

modulemux1(a,b,sel,c);

parameterw=32;

input[w-1:

0]a,b;

inputsel;

output[w-1:

0]c;

assignc=(sel==0)?

a:

b;

endmodule

(3)符号扩展和移位

本实验中的符号扩展是在数据使用之前进行0扩展或符号扩展,是把16位的数据扩展成32的数据。

din为16位输入数据,dout为32为输出数据,程序如下:

modulesignextend(din,dout);

input[15:

0]din;

output[31:

0]dout;

assigndout[15:

0]=din;

assigndout[31:

16]=16'h0000;

endmodule

(4)寄存器RegFile模块

根据输入的寄存器地址读写寄存器,n1为源操作数1的寄存器地址,n2为源操作数2的寄存器地址,we为写寄存器信号,nd写寄存器的地址,di写寄存器的数据,q1为源操作数1的数据,q2为源操作数2的数据。

当we为0时,q1输出以源操作数1为地址的数据,q2输出以源操作数2为地址的数据,当we为1时,把di输入的数据写到以nd为地址的寄存器中。

部分程序如下:

reg[31:

0]r[31:

0];//定义寄存器;

assignq1=(n1==0)?

0:

r[n1];

assignq2=(n2==0)?

0:

r[n2];

always@(posedgeclk)

begin

if(we)

r[nd]=di;

end

endmodule

(5)ALU模块

算术逻辑单元(ALU:

aritl-irneticlogicunit)的设计是CPU设计中重要的一个环节。

可以这样说,微处理器中最重要的地方是ALU,它是CPU真正处理数据的地方。

ALU使用的数据来自寄存器(Register),它读取寄存器中的数据并进行一些计算(如对两个数据相加、对两个数据进行逻辑或运算等等),然后把计算结果返回到寄存器中,最后再把寄存器中的结果返回到主内存中。

根据控制信号aluc确定执行功能如图三所示:

assignzero=(c==0)?

1:

0;

always@(a,b,aluc)

begin

case(aluc)

ADD:

c=a+b;

SUB:

c=a-b;

AND:

c=a&b;

OR:

c=a|b;

SLT:

c=(a1:

0;

default:

c=0;

endcase

end

(6)InstMem模块和DataMem模块的实现

InstMem是32位的指令寄存器,存放着指令数据。

DataMem是数据寄存器,当we信号为1时,写寄存器。

部分程序如下:

reg[31:

0]ram[31:

0];

always@(negedgeclk)

begin

if(we)

begin

ram[addr]=wd;

end

data=ram[addr];

end

(7)Control控制器