EDA实验报告时序电路.docx

《EDA实验报告时序电路.docx》由会员分享,可在线阅读,更多相关《EDA实验报告时序电路.docx(10页珍藏版)》请在冰豆网上搜索。

EDA实验报告时序电路

专用集成电路设计实验报告

实验78时序逻辑的特性

姓名:

***

学号:

**********

班级:

电科1301

指导老师:

***

1、实验目的

理解CMOS静态传输门寄存器的结构和时序特性。

了解SPICE仿真模型、门级(RTL级)仿真模型、电路综合模型之间的区别。

2、实验内容

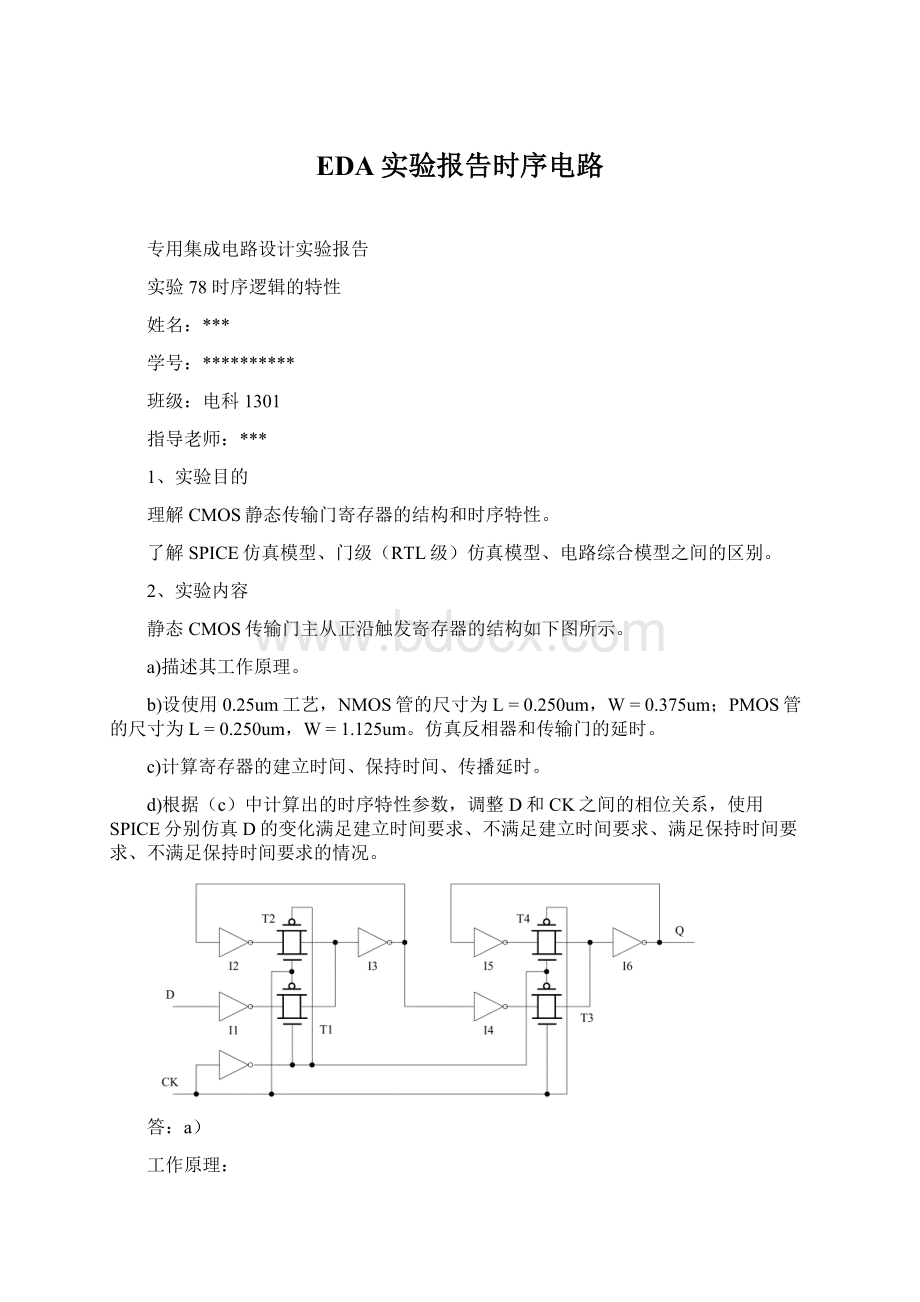

静态CMOS传输门主从正沿触发寄存器的结构如下图所示。

a)描述其工作原理。

b)设使用0.25um工艺,NMOS管的尺寸为L=0.250um,W=0.375um;PMOS管的尺寸为L=0.250um,W=1.125um。

仿真反相器和传输门的延时。

c)计算寄存器的建立时间、保持时间、传播延时。

d)根据(c)中计算出的时序特性参数,调整D和CK之间的相位关系,使用SPICE分别仿真D的变化满足建立时间要求、不满足建立时间要求、满足保持时间要求、不满足保持时间要求的情况。

答:

a)

工作原理:

当时钟处于低电平时(CLK=0),T1导通T2关断,输入D被采样到节点Qm上。

在此期间,T3和T4分别关断和导通。

交叉耦合的反相器(I5,I6)保持从锁存器的状态。

当时钟上升到高电平时,主级停止采样输入并进入维持状态。

T1关断T2导通,交叉耦合的反相器I2和I3保持Qm状态。

同时,T3导通T4关断,Qm被复制到输出Q上。

b)

反相器延时:

仿真波形图如图1.1所示。

图1.1反相器延时仿真波形图

Measure输出文件为:

$DATA1SOURCE='HSPICE'VERSION='U-2003.09'

.TITLE'*dai78_1object'

invt1dlayinvt2dlaytemperalter#

2.795e-111.937e-1125.00001.0000

输入下降延时:

2.795e-11s

输入上升延时:

1.937e-11s

(这里及以下计算的都是50%——50%延时)

传输门:

仿真波形如图1.2所示

这里设置传输门的C端(Nmos的栅极)为高电平,输入A为脉冲信号,测试B端输出的延时。

图1.2传输门的延时

Measure输出文件为:

$DATA1SOURCE='HSPICE'VERSION='U-2003.09'

.TITLE'*dai78_1object'

invt1dlayinvt2dlaytemperalter#

1.204e-111.108e-1125.00001.0000

上升沿延时:

1.204e-11s

下降沿延时:

1.108e-11s

该部分的程序为:

*dai78_1object

.lib'cmos25_level49.txt'TT

.optionspost=2

.tran1ps1ns

.probe

.globalpvccvcc

Vccpvcc0dc2.5V

V1A0pulse(0V2.5V0ps0ps0ps200ps400ps)

V3C0dc2.5V

*pulse(0V2.5V0ps0ps0ps200ps400ps)

.subcktinvinout

m1outinGNDGNDNMOSL=0.25uW=0.375u

m2outinpvccpvccPMOSL=0.25uW=1.125u

.ends

.subckttrangABC0C

m1BC0ApvccPMOSL=0.25uW=1.125u

m2BCAGNDNMOSL=0.25uW=0.375u

.ends

x1CC0inv

x2AoutC0Ctrang

.measuretraninvt1dlaytrigV(A)val=1.25Vtd=0rise=2

+targV(out)val=1.25Vtd=0rise=2

.measuretraninvt2dlaytrigV(A)val=1.25Vtd=0fall=2

+targV(out)val=1.25Vtd=0fall=2

.end

c)

计算寄存器的建立时间

选择反相器上升沿和下降沿延时中较大的作为传播延时Tpd_inv=27.95ps.

选择传输门上升沿和下降沿延时中较大的作为传播延时Tpd_tx=12.04ps

假设污染延时为0,而且CLK的反向输出延时也为0.

则建立时间=3*Tpd_inv+Tpd_tx=95.89ps

传播延时=Tpd_inv+Tpd_tx=39.99ps

维持时间为0.

当时钟为高电平时,传输门T1关断。

由于D输入和CLK在到达T1之前都要通过反相器,所以在时钟变为高电平之后输入上的任何变化都不会影响输出。

d)

设置输入D和时钟CLK都为pulse电压源。

输入D延时130ps

时钟CLK延时300ps

相差170ps

仿真的波形输出如图1.3所示。

图1.3输入与时钟相差170ps时的仿真波形输出

由上至下依次是D、CLK、Q、Qm,可以看出Q的值不对。

可以看到Qm有上升的过程,但是在上升结束前传输门T2的输入就已经下降了。

而时钟在传输门T2两端的节点稳定在同一值之前就有效了,因此造成了不正确的值写入主寄存器。

调整输入D与时钟的时间差

输入延时120ps

时钟延时300ps

相差180ps

仿真的波形如图1.4所示

图1.4输入与时钟相差180ps时的仿真波形输出

可见Q的输出稳定在2.5V(高电平),所以对输入D的采样值是正确的。

故寄存器的建立时间应小于等于180ps,在171ps——180ps之间。

继续调整输入与时钟的时间差,通过仿真得到寄存器的建立时间。

相差175ps时的仿真波形图:

图1.5输入与时钟相差175s时的仿真波形输出

相差173ps时的仿真波形:

图1.6输入与时钟相差173s时的仿真波形输出

相差171ps时的仿真波形:

图1.7输入与时钟相差171s时的仿真波形输出

这里Q的输出错误,所以建立时间应大于171ps

相差172ps时的仿真波形:

图1.8输入与时钟相差172s时的仿真波形输出

Q的输出正确,所以可以在ps级确定寄存器的建立时间为172ps。

保持时间:

验证保持时间是否为0s

即让输入的下降沿与时钟的上升沿的时间差为0.

仿真的波形图如图1.9所示。

图1.9输入与时钟相差0s时的仿真波形输出

可见即使保持时间为0,Q依旧输出正确。

传播延时:

这里计算从CLK边沿的50%点处到Q输出的50%点处的延时。

仿真波形如图1.10所示。

图1.10传输门寄存器的传播延时

$DATA1SOURCE='HSPICE'VERSION='U-2003.09'

.TITLE'*dai76_2object'

upt1dlaydownvt2dlaytemperalter#

1.371e-101.944e-1025.00001.0000

可见Tc-q(lh)=137.1ps

Tc-q(hl)=194.4ps

疑问:

为何依照书上P-244计算出的建立时间和传播延时与仿真得到的结果不同呢?

分析:

可能是因为书上的计算是假设了污染延时为0,CLK经过的反相器延时也为0.显然在仿真中,这些假设都是不能成立的。

所以计算出现了误差。

程序(网表文件):

*dai76_2object

.lib'cmos25_level49.txt'TT

.optionspost=2

.tran1ps3ns

.probe

.globalpvccvcc

Vccpvcc0dc2.5V

*V1A0dc2.5V

V3D0pulse(0V2.5V0ps0ps0ps1.25ns3ns)

V4Clk0pulse(0V2.5V500ps0ps0ps0.5ns1ns)

x1ClkClk0inv

.subcktinvinout

m1outinGNDGNDNMOSL=0.25uW=0.375u

m2outinpvccpvccPMOSL=0.25uW=1.125u

.ends

.subckttrangABC0C

m1BC0ApvccPMOSL=0.25uW=1.125u

m2BCAGNDNMOSL=0.25uW=0.375u

.ends

.subcktheadginDinCinC0outQ

x1inDinD0inv

x2inD0BinC0inCtrang

x3BoutQinv

x4outQAinv

x5ABinCinC0trang

.ends

x3Dclk0clkQmheadg

x4Qmclkclk0Qheadg

.measuretranupt1dlaytrigV(Clk)val=1.25Vtd=0rise=1

+targV(Q)val=1.25Vtd=0rise=1

.measuretrandownt2dlaytrigV(Clk)val=1.25Vtd=0rise=2

+targV(Q)val=1.25Vtd=0fall=1

.end