DSP实验指导书.docx

《DSP实验指导书.docx》由会员分享,可在线阅读,更多相关《DSP实验指导书.docx(23页珍藏版)》请在冰豆网上搜索。

DSP实验指导书

第一章实验系统介绍

一、系统概述

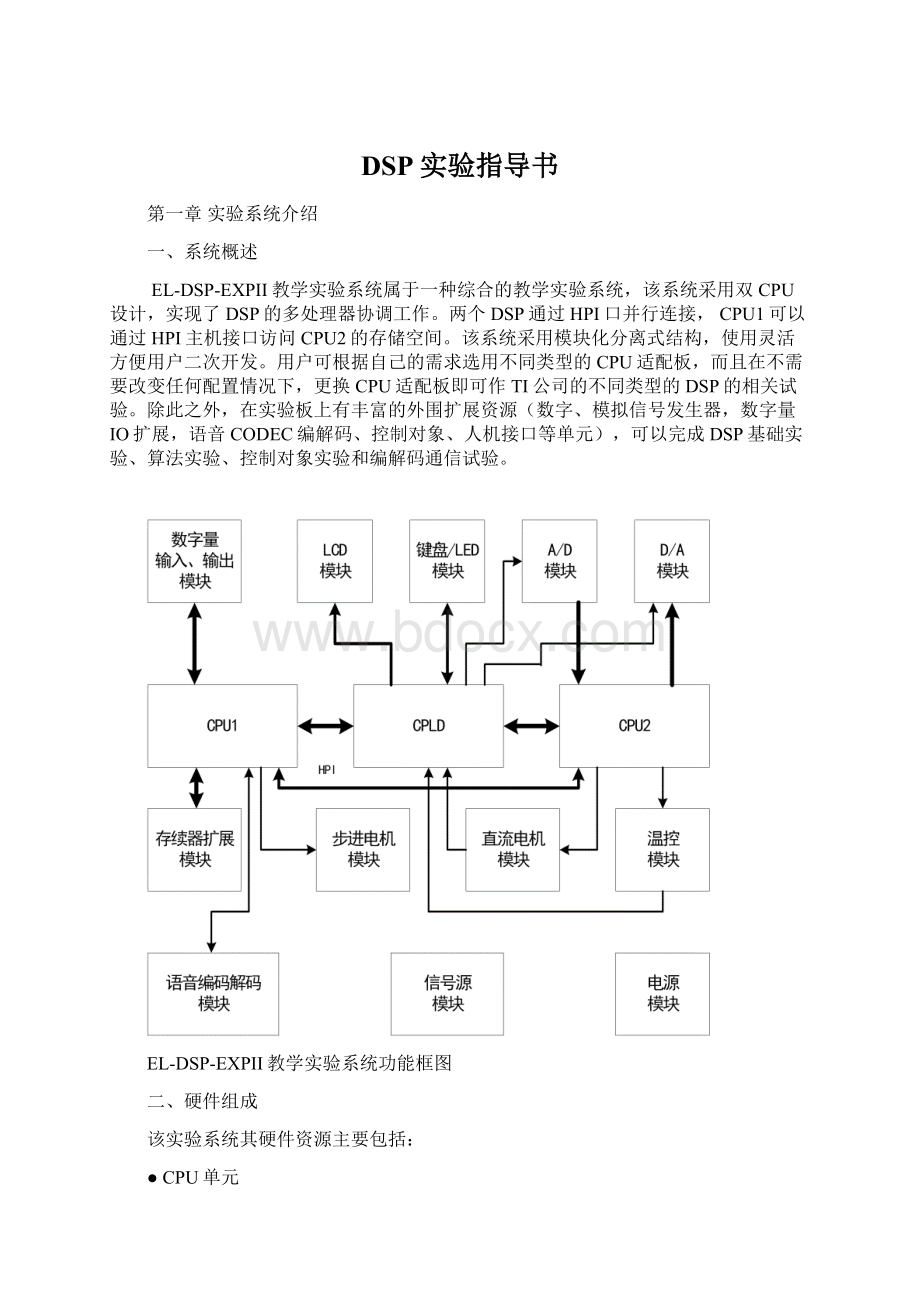

EL-DSP-EXPII教学实验系统属于一种综合的教学实验系统,该系统采用双CPU设计,实现了DSP的多处理器协调工作。

两个DSP通过HPI口并行连接,CPU1可以通过HPI主机接口访问CPU2的存储空间。

该系统采用模块化分离式结构,使用灵活方便用户二次开发。

用户可根据自己的需求选用不同类型的CPU适配板,而且在不需要改变任何配置情况下,更换CPU适配板即可作TI公司的不同类型的DSP的相关试验。

除此之外,在实验板上有丰富的外围扩展资源(数字、模拟信号发生器,数字量IO扩展,语音CODEC编解码、控制对象、人机接口等单元),可以完成DSP基础实验、算法实验、控制对象实验和编解码通信试验。

EL-DSP-EXPII教学实验系统功能框图

二、硬件组成

该实验系统其硬件资源主要包括:

●CPU单元

●数字量输入输出单元

●存储器及信号扩展单元

●BOOTLOADER单元

●语音模块

●液晶模块

●CPLD接口

●A/D转换单元

●D/A转换单元

●信号源单元

●温控单元

●步进电机

●直流电机

●键盘接口

●电源模块

1、CPU单元

CPU单元包括CPU1、CPU2两块可以更换的CPU板,用户可根据需要选择不同种

类的CPU板。

板上除CPU之外还包括以下单元:

1)CPU模式选择

CPU通常情况下可以根据用户需求工作在不同的模式下,主要用MP/

的电平来决定。

当MP/

为高电平时,DSP工作在微处理器模式,当MP/

为低电平时。

DSP工作在为计算机方式。

在不同模式下存储器映射表有所不同。

详细信息请查阅相应的数据手册。

2)电源模块

在CPU板上由于TMS320VC54X数字信号处理器内核采用3.3V和1.8V供电,因此需要将通用的5V转换成3.3V和1.8V。

为中央处理器提供内部电源。

转换电路如图所示:

3)电平转换

由于数字信号处理其内部采用3.3V和1.8V供电,而且其输入输出接口电平为3.3V,对于数字量输出而言完全可以和5V电平兼容。

但对于数字量输入而言,由于其内部是3.3V,因此不能将中央处理器的输出口直接和外围扩展的5V器件相连,必须加入电平转换期间进行电平转换和信号隔离。

典型的就是数据线,必须进行隔离,对于其他的涉及到的输入信号也要进行相应的转换。

在CPU板上,U2(LVTH16245)完成了该项功能。

4)复位电路以及时钟单元

复位电路主要包括上电复位和硬件手动复位,每次复位要求至少要有8到10个系统时钟。

因此要求适当的配置复位电路RC网络。

时钟电源主要利用数字信号处理器内部晶振源,并通过外部锁相环控制电路,选择适当倍频倍数,为CPU内部提供系统时钟。

2、数字量输入输出单元

●8bit的数字量输入(由八个带自锁的开关产生),通过74LS244缓冲;8bit的数字量输出(通过八个LED灯显示),通过74LS273锁存。

数字量的输入输出都映射到CPU的IO空间。

●数字量显示的八个LED数码管,通过HD7279控制。

3、存储器及信号扩展单元:

1)静态存储器SRAM(IS61C25632K×8bit)

在该实验板上,使用的存储器接口芯片是ISSI公司的IS61C256,它具有以下特点:

●访问速度10、12、15、20、25ns可选;

●低功耗:

400mW(典型);

●低静态功耗

-250μW(典型)CMOS器件;

-55mW(典型)TTL器件;

●全静态操作,无需时钟或刷新;

●输入输出和TTL电平兼容;

●单5V供电。

静态存储器分为两个部分,一部分是32K×16bit的程序存储器(地址为8000H~0FFFFH)芯片序号U20、U21和32K×16bit的数据存储器(地址为0000H~7FFFH)芯片序号U22、U23。

根据选择不同类型的CPU分别映射到相应地址的程序空间和数据空间。

2)、DSK扩展信号插座:

接插件P7、P8是和TI公司DSK兼容的信号扩展接口,可连接图像处理、高速AD、DA、USB、以太网等扩展板,也可以连接TI公司的标准DSK扩展信号板。

P7:

CPU信号扩展(TI公司兼容DSK接口)

序号

符号

备注

1

+12V

电源

2

-12V

电源

3

GND

地

4

GND

地

5

+5V

电源

6

+5V

电源

7

GND

地

8

GND

地

9

+5V

电源

10

+5V

电源

11

NC

空脚

12

NC

空脚

13

NC

空脚

14

NC

空脚

15

NC

空脚

16

NC

空脚

17

NC

空脚

18

NC

空脚

19

+3.3V

电源

20

+3.3V

电源

21

BCLKX0

MCBSP0数据输出时钟

22

NC

空脚

23

BFX0

MCBSP0数据输出帧时钟

24

BDX0

MCBSP0数据输出

25

+5V

电源

26

GND

地

27

BCLKR0

MCBSP0数据输入时钟

28

NC

空脚

29

BFR0

MCBSP0数据输入帧时钟

30

BDR0

MCBSP0数据输入

31

+12V

电源

32

GND

地

33

BCLKX1

MCBSP1数据输出时钟

34

NC

空脚

35

BFX1

MCBSP1数据输出帧时钟

36

BDX1

MCBSP1数据输出

37

GND

地

38

GND

地

39

BCLKR1

MCBSP1数据输入时钟

40

NC

空脚

41

BFR1

MCBSP1数据输入帧时钟

42

BDR1

MCBSP1数据输入

43

GND

地

44

GND

地

45

TOUT0

定时器0输出

46

NC

空脚

47

NC

空脚

48

INT0

中断0

49

TOUT1

定时器1输出

50

NC

空脚

51

GND

地

52

GND

地

53

INT1

中断1

54

NC

空脚

55

NC

空脚

56

NC

空脚

57

NC

空脚

58

NC

空脚

59

RES

复位信号

60

NC

空脚

61

GND

地

62

GND

地

63

NC

空脚

64

NC

空脚

65

NC

空脚

66

NC

空脚

67

INT2

中断2

68

INT3

中断3

69

NC

空脚

70

NC

空脚

71

NC

空脚

72

NC

空脚

73

NC

空脚

74

NC

空脚

75

GND

地

76

GND

地

77

GND

地

78

CLK

时钟

79

GND

地

80

GND

地

P8:

CPU信号扩展(TI公司兼容DSK接口)

序号

符号

备注

1

+5V

电源

2

+5V

电源

3

A19

地址

4

A18

地址

5

A17

地址

6

A16

地址

7

A15

地址

8

A14

地址

9

A13

地址

10

A12

地址

11

GND

地

12

GND

地

13

A11

地址

14

A10

地址

15

A9

地址

16

A8

地址

17

A7

地址

18

A6

地址

19

A5

地址

20

A4

地址

21

+5V

电源

22

+5V

电源

23

A3

地址

24

A2

地址

25

A1

地址

26

A0

地址

27

A21

地址

28

A20

地址

29

NC

空脚

30

NC

空脚

31

GND

地

32

GND

地

33

NC

空脚

34

NC

空脚

35

NC

空脚

36

NC

空脚

37

NC

空脚

38

NC

空脚

39

NC

空脚

40

NC

空脚

41

+3.3V

电源

42

+3.3V

电源

43

NC

空脚

44

NC

空脚

45

NC

空脚

46

NC

空脚

47

NC

空脚

48

NC

空脚

49

NC

空脚

50

NC

空脚

51

GND

地

52

GND

地

53

D15

数据

54

D14

数据

55

D13

数据

56

D12

数据

57

D11

数据

58

D10

数据

59

D9

数据

60

D8

数据

61

GND

地

62

GND

地

63

D7

数据

64

D6

数据

65

D5

数据

66

D4

数据

67

D3

数据

68

D2

数据

69

D1

数据

70

D0

数据

71

GND

地

72

GND

地

73

DSKRE

读写信号CPLD控制

74

SWE

写信号

75

SOE

读信号

76

READY

准备好信号

77

CE3

片选

78

CE2

片选

79

GND

地

80

GND

地

4、BOOTLOADER单元:

使用的存储器接口芯片是28C25632K×8bit,地址为数据空间8000H~0FFFFH,它具有以下特点:

●访问速度快于45ns

●低功耗:

典型静态CMOS电流20μA

●单5V供电

●供电电压可在±10%变化

●典型编程时间4S

●100mA闩锁保护从-1V到VCC+1V

●高噪声门限

●CMOS/TTL输入/输出电平兼容

●标准28脚DIP、PDIP封装或32脚PLCC封装

板上芯片序号U24用来存放用户程序,可以通过选择CPU板上的MP/

来选择bootloader模式。

出厂时存储器内固化了系统测试程序,上电后可对系统硬件进行自动测试。

在本系统中采用并行存储器引导模式。

5、语音处理单元

语音CODEC采用TLC320AD50芯片。

该芯片采用sigma-delta技术提供高精度低速信号变换,有两个串行同步变换通道、D/A转换前的差补滤波器和A/D变换后的滤波器。

其他部分提供片上时序和控制功能。

Sigma-delta结构可以实现高精度低速的数模/模数转换。

芯片的各种应用软件配置可以通过串口来编程实现。

主要包括:

复位、节电模式、通信协议、串行时钟速率、信号采样速率、增益控制和测试模式。

最大采样速率22.05kb/s,采样精度16bit。

语音处理单元由语音输入模块、TLC320AD50模块、输出功率模块组成。

语音输入模块采用偏置和差动放大技术,并经过滤波和处理后将输入到语音编解码芯片TLV320AD50,前端输入的电压范围为-2.5V---+2.5V。

经过变换后输入到AD50的芯片的差动信号范围为0---5V。

TLC320AD50C作为主方式,通过DSP的MCBSP0口进行通信。

音频信号通过D/A转换后输出,由于TLC320AD50输出的是差动信号,因此首先经过差动放大,然后可以推动功率为0.4W的板载扬声器,也可以接耳机输出。

语音处理单元原理框图

语音处理单元接口说明:

J14:

音频输入端子,可输入CD、声卡、MP3、麦克风等语音信号。

J15:

音频输出端子,可接耳机、音箱。

J3:

语音处理单元输入信号接口

J1:

语音处理单元输出信号接口

J6:

地

语音处理单元拨码开关说明:

S1:

拨码开关:

码位

备注

1

ON:

帧同步脉冲接通,缺省设置;OFF:

帧同步脉冲关断;

2

ON:

串口时钟接通,缺省设置;OFF:

缓冲串口时钟关断;

S2:

拨码开关

码位

备注

1

ON:

直流量输入,OFF:

交流量输入,缺省设置

2

ON:

扬声器输出;OFF:

扬声器关闭,缺省设置

语音处理单元可调电位器说明:

“输入调节”:

逆时针

音量变大

顺时针

音量变小

“输出调节”:

逆时针

音量变大

顺时针

音量变小

注:

语音处理单元的二号孔IN和OUT通过导线的连接,可以为温控单元,信号源单元提供A/D,D/A转换的功能。

详细操作参见实验指导。

6、液晶模块

本实验系统选用中文液晶显示模块LCM12864ZK,其字型ROM内含8192个16*16点中文字型和128个16*8半宽的字母符号字型;另外绘图显示画面提供一个64*256点的绘图区域GDRAM;而且内含CGRAM提供4组软件可编程的16*16点阵造字功能。

电源操作范围宽(2.7Vto5.5V);低功耗设计可满足产品的省电要求。

同时,与CPU等微控器的接口界面灵活(三种模式并行8位/4位串行3线/2线);LCD数据接口基本上分为串行接口和并行接口两种形式,本实验采用串行接口方式,用户根据需要改变跳线JS1改用并行接口方式。

液晶模块拨码开关说明:

S23:

拨码开关

码位

备注

1

空位

2

ON,液晶模块背光电源开;OFF,液晶模块背光电源关,缺省设置;

7、CPLD接口

采用XILINX公司的XC95144XL芯片,完成译码和时序控制。

JTAG4为CPLD下载接口。

可用XILINX公司的软件,通过并口下载电缆对CPLD在线编程。

JTAG4CPLD下载口定义

JTAG1引脚序号

JTAG功能组

相关说明

1

TCK

时钟

2

NC

空脚

3

TMS

模式控制

4

GND

地

5

TDI

数据输入

6

NC

空脚

7

TDO

数据输出

8

GND

地

9

+5V

电源

10

+5V

电源

D2、D3为CPLD工作指示灯,正常工作时D2、D3点亮。

CPU1复位时,

D3不亮,CPU2复位时,D2不亮。

8、D/A转换单元

数模转换采用DAC08芯片,分辨率8位,精度1LSB,转换时间可达85ns。

DAC08可以应用在8-bit,1usA/D变换,伺服电机、波形发生、语音编码、衰减器、可编程功率变换器、CRT显示驱动、高速modems以及其他要求低成本、高速等多功能场合。

在本实验系统中,DAC08采用对称偏移二进制输出方式,输出电压范围-5V~+5V。

注:

Vref=+10V

对称偏移二进制输出编码图

底板DAC08参考电压Vref=+5V;输入00h,输出电压-5V;输入ffh,输出电压+5V。

D/A单元原理框图

数模转换单元接口说明:

S24:

拨码开关

码位

备注

1

ON,DA输出给直流电机控制端;OFF,DA输出悬空,缺省设置;

2

ON,DA输出给J4端子;OFF,DA输出悬空,缺省设置;

J4:

DA输出端子

J2:

地

9、A/D转换单元

模数转换芯片选用AD7822,单极性输入,采样分辨率8BIT,并行输出;內含取样保持电路,以及可选择使用內部或外部参考电压源,具有转换后自动Power-Down的模式,电流消耗可降低至5μA以下。

转换时间最大为420ns,SNR可达48dB,INL及DNL都在±0.75LSB以內。

可应用在数据采样、DSP系统及移动通信等场合。

在本实验系统中,参考电压源+2.5V,偏置电压输入引脚Vmid=+2.5V。

模拟输入信号经过运放处理后输入AD7822。

Vin

D7~D0

Vref/2

00000000

Vref

10000000

Vref+Verf/2

11111111

AD7822编码图

模数单元原理框图

模数转换单元拨码开关说明:

S25:

拨码开关

码位

备注

1

ON,信号源1输出给AD;OFF,AD输入悬空,缺省设置;

2

ON,信号源2输出给AD;OFF,AD输入悬空,缺省设置;

S26:

拨码开关

码位

备注

1

ON,温控单元输出给AD;OFF,AD输入悬空,缺省设置;

2

ON,J12端子输入给AD;OFF,AD输入悬空,缺省设置;

J12:

AD输入端子

J23:

地

拨码开关其它设置状态为非法状态

10、信号源单元

频率、幅值可调双路三角波、方波和正弦波产生电路采用两片8038信号发生器,输出频率范围20~100KHz,幅值范围-10V~+10V。

输出波形、频率范围可通过波段开关来选择。

频率、幅值可独立调节。

两路输出信号可以经过加法器进行信号模拟处理和混叠,作为信号滤波处理的混叠信号源。

混叠后的信号从信号源1输出。

ICL8038原理框图

信号源单元原理框图

信号源单元波段开关说明:

波形选择波段开关拨到底板丝印的相应位置选择对应的波形(正弦、三角、方波),频率选择波段开关拨到底板丝印的相应位置选择对应的频率范围(0~2K、2K~10K、10K~120K)。

信号源单元电位器说明:

“频率调节”

左旋

变小

右旋

变大

“幅值调节”

左旋

变大

右旋

变小

J8:

信号源1输出

J7:

信号源2输出

J5:

地

11、温度控制单元

由温度信号采集单元、加热信号驱动单元、模拟温箱加热控制电路组成。

温度信号采集单元电路的热敏电阻的阻值随温度的变化而变化,经运放处理,输出一个电压变化(逐渐减小)的温度信号给系统板的A/D采集输入端;加热信号驱动单元将系统板送来的加热信号分两路处理:

一路放大后驱动加热指示二极管发光;另一路经隔离后驱动可控硅导通。

模拟温箱加热控制电路由加热信号隔离电路、AC220V控制电路(可控硅)输出电路组成。

温度控制单元拨码开关说明:

S5:

拨码开关

码位

备注

1

ON,+5V电源给温控单元;OFF,断开+5V电源,缺省设置

2

ON,+12V电源给温控单元;OFF,断开+12V电源,缺省设置

J10:

温度控制单元反馈电压输出

J11:

地

LED18:

+12V电源指示灯。

12、步进电机单元

步进电机多为永磁感应式,有两相、四相、六相等多种,实验所用的电机为两相四拍式,通过对每相线圈中的电流的顺序切换来使电机作步进式旋转,驱动电路由脉冲信号来控制,所以调节脉冲信号的频率便可改变步进电机的转速。

脉冲信号是有DSP的IO端口(地址8001H)的低四位提供。

位0对应“D”,位1对应“C”,位2对应“B”,位3对应“A”;

如下图所示,电机每相电流为0.2A,相电压为5V,两相四拍的通电顺序如下表所示:

相

顺序

A

B

C

D

0

1

0

1

0

1

0

1

1

0

2

0

1

0

1

3

1

0

0

1

注:

顺时针方向旋转通电顺序为0-1-2-3;

逆时针方向旋转通电顺序为3-2-1-0;

步进电机单元拨码开关说明:

S4:

拨码开关

码位

备注

1

ON,+5V电源给步进电机单元;OFF,断开+5V电源,缺省设置

2

ON,+12V电源给直流电机单元;OFF,断开+12V电源,缺省设置

LED16:

+12V电源指示灯;

LED17:

+5V电源指示灯;

13、直流电机单元

该单元由电压调整、驱动电路、速度检测反馈电路组成。

由系统板送来的电压信号与可调节的基准电压经加法运算后,输出驱动直流电机运行;速度检测、反馈电路由于电机同轴转的转盘上的强力磁钢、霍尔磁感应放大器、单周期速度信号采集器组成,当与电机同轴运行的转盘上的磁钢与霍尔片正对时,霍尔片输出负电压,经整形、放大,供系统采集。

J9:

直流电机控制脉冲输入端

J13:

地

LED15:

中断反馈指示灯;

14、键盘接口

键盘接口是由芯片HD7279按制的,HD7279是一片具有串行接口的,可同时驱动8位共阴式数码管或(64只独立LED)的智能显示驱动芯片,该芯片同时还可连接多达64键的键盘矩阵,单片即可完成LED显示,键盘接口的全部功能。

HD7279A内部含有译码器,可直接接受BCD码或16进制码,并同时具有2种译码方式。

此外,还具有多种控制指令,如消隐、闪烁、左移、右移、段寻址等。

HD7279A具有片选信号,可方便地实现多于8位的显示或多于64键的键盘接口。

在该实验系统中,仅提供了16个键。

15、其它接口说明

电源单元:

为系统提供+5V、+12V、-12V、+3.3V电源

S22:

拨码开关,CPU中断源选择

码位

备注

1---ON

2---ON

CPU中断2给键盘接口

1---ON

2---OFF

CPU中断2给A/D转换单元

1---OFF

2---ON

CPU中断3给键盘接口

1---OFF

2---OFF

CPU中断2、3置高,缺省设置

S3:

拨码开关

码位

备注

1

OFF,A/D单元采样时钟为低频,缺省设置;

ON,A/D单元采样时钟为高频

2

ON,J8为信号源1、2路的混频输出;OFF,断开混频输出,缺省设置

JTAG接口:

JTAG3接口定义

引脚序号

JTAG功能组

相关说明

1

TMS

JTAG模式控制

2

TRST

JTAG复位

3

TDI

JTAG数据输入

4

GND

地

5

电源

+3.3V

6

NC

空脚

7

TDO

JTAG数据输出

8

GND

地

9

TCLK

JTAG时钟

10

GND

地

11

TCLK

JTAG时钟

12

GND

地

13

EMU0

仿真中断0

14

EMU1

仿真中断1

K1:

非自锁按键,每按一下产生一个负的脉冲。

K10:

自锁按键

状态

备注

按下

JTAG3连接到JTAG2

弹起

JTAG3连接到JTAG1

综上所述,本章介绍了该系统的硬件资源,看完本章内容,应该对实验系统有一个基本的了解,在余下的几章中将会结合实验详细介绍,每个单元在实验中的具体应用。