ABEL部分程序要点.docx

《ABEL部分程序要点.docx》由会员分享,可在线阅读,更多相关《ABEL部分程序要点.docx(14页珍藏版)》请在冰豆网上搜索。

ABEL部分程序要点

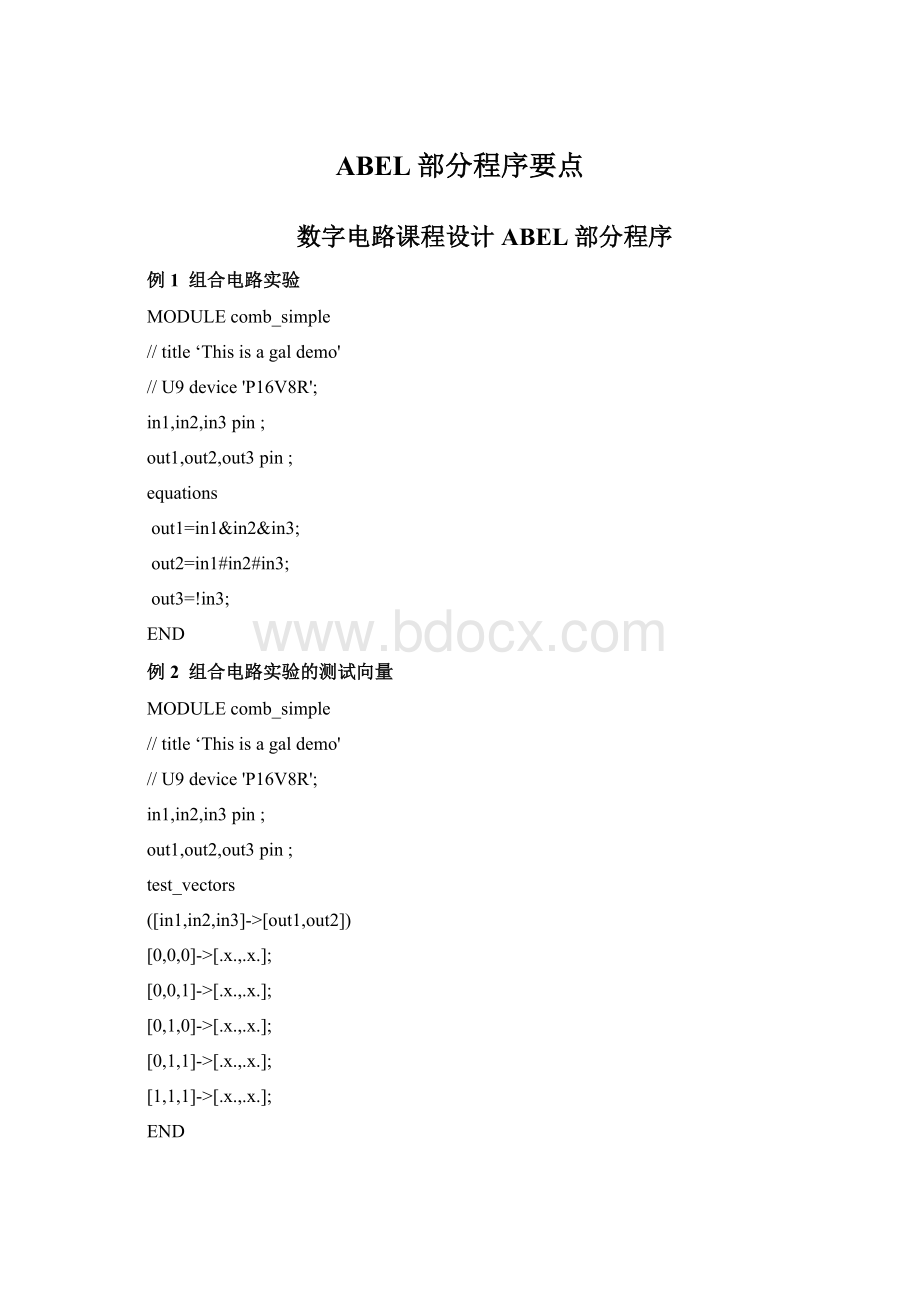

数字电路课程设计ABEL部分程序

例1组合电路实验

MODULEcomb_simple

//title‘Thisisagaldemo'

//U9device'P16V8R';

in1,in2,in3pin;

out1,out2,out3pin;

equations

out1=in1&in2&in3;

out2=in1#in2#in3;

out3=!

in3;

END

例2组合电路实验的测试向量

MODULEcomb_simple

//title‘Thisisagaldemo'

//U9device'P16V8R';

in1,in2,in3pin;

out1,out2,out3pin;

test_vectors

([in1,in2,in3]->[out1,out2])

[0,0,0]->[.x.,.x.];

[0,0,1]->[.x.,.x.];

[0,1,0]->[.x.,.x.];

[0,1,1]->[.x.,.x.];

[1,1,1]->[.x.,.x.];

END

例3用GAL16V8设计如下6个基本逻辑门:

P123与门,或门,与非门,或非门,异或门,同或门。

解6个基本逻辑门的逻辑表达式为

根据上述逻辑表达式,采用一片GAL16V8就可以实现6个基本逻辑门。

用ABLE-HDL语言写出的基本逻辑门的设计源文件如下:

MODULEBASIC-GATES//头部

TITLE'BASICGATES';//说明部

IC1DEVICE'P16V8S';

A1,B1,A2,B2PIN19,1,2,3;输入脚定义

A3,B3,A4,B4PIN4,5,6,7;

A5,B5,GNDPIN8,9,10;

A6,B6,F6,F5PIN11,12,14,14;

F4,F3,F2,F1PIN15,16,17,18;输出脚定义

EOUATIONS//逻辑描述部

F1=A1&B1;&表示“与”运算

F2=A2#B2;#表示“或”运算

F3=!

(A3&B3);!

表示“非”运算

F4=!

(A4#B4);

F5=A5$B5;$表示“异或”运算

F6=(A6!

$B6);!

$表示“同或”运算

TEST_VECTIORS([A1,B1,A2,B2,A3,B3,A4,B4,A5,B5,A6,B6]->[F1,F2,F3,F4,F5,F6])

"INPUTOUTPUT"

[0,0,0,0,0,0,0,0,0,0,0,0]->[0,0,1,1,0,1]

[0,1,0,1,0,1,0,1,0,1,0,1]->[0,1,1,0,1,0]

[1,0,1,0,1,0,1,0,1,0,1,0]->[0,1,1,0,1,0]

[1,1,1,1,1,1,1,1,1,1,1,1]->[1,1,0,0,0,1]

ENDBASIC-GATES

例4带三态控制的四输入与非门

P153例2一个带三态控制的四输入与非门的ABLE-HDL模块源程序如下:

MODULEGAL5//模块GAL5开始

TITLE'ableinputfile'//标题语句

U05DEVICE'P16V8C'//器件说明:

U05为P16V8C

a,b,c,dPIN2,3,4,5;//输入管脚说明

fPIN12;//输出管脚说明

ENBPIN6;//三态控制说明

h,1,x,z=1,0,.x.,z.;//常量定义,便于向量测试使用

EQUATIONS//逻辑方程描述部

f=!

(a&b&c&d);

Enablef=enb;

TEST_VECTORS([end,a,b,c,d]->[f])//测量向量部

[h,0,.x.,.x.,.x.]->[1];//.x.表示任意态(0或1)

[h,.x.,0.x.,.x.]->[1];

[h,.x.,.x.,0,.x.]->[1];

[h,.x.,.x.,.x.,0]->[1];

[h,1,1,1,1]->[0];

[1,x,x,x,x]->[z];//Z表示高阻态输出

ENDGAL5//模块GAL5结束

例52位计数器

P153例3描述一个2位计数器的ABLE_HDL模块源程序如下:

MODULEcounter//头部

TITLE'TwobitsCounterBlock';

DECLARATIONS//说明部

"Input

ClockPIN

CLRPIN

"Output

q0,q1PINISTYPE'reg';

EQUATIONS//逻辑描述部

q0.clk=clock;

q1.clk=clock;

q0.AR=CLR;

q1.AR=CLR;

q0:

=!

q0;

q1:

=!

q1&q0#q1&!

q0;

ENDcoubter//结束部

例62位计数器实验的测试向量

MODULEcounter//头部

TITLE'TwobitsCounterBlock';

DECLARATIONS//说明部

"Input

ClockPIN

CLRPIN

"Output

q0,q1PINISTYPE'reg';

test_vectors

([CLR,Clock]:

>[q0,q1])

[0,.C.]:

>[.x.,.x.];

[1,.C.]:

>[.x.,.x.];

[1,.C.]:

>[.x.,.x.];

[1,.C.]:

>[.x.,.x.];

[1,.C.]:

>[.x.,.x.];

END

例74位二进制加法计数器

P156例4用基本表达形式描述一个4位二进制加法计数器。

解EQUATIONS

COUNT.CLK=CLK;

COUNT.AR=CLR;

COUNT:

=(COUNT.FB)&!

CAI#(COUNT.FB+1)&CAI;

CAO=Q3.Q&Q2.Q&Q1.Q&Q0.Q&CAO;

例8状态图的设计

P124例10采用GAL16V8器件,用状态图方式描述图4.24所示的状态图,用ABLE-HDL语言写出设计源文件。

解该状态机具有四个状态。

在时钟的作用下,该状态机由一个状态转到下一状态。

状态机在这四个状态之间轮流转换。

状态机的状态由A、B寄存器定义,在AB=01时,输出信号Y为0,其余情况下,输出Y=1.

首先要定义状态名,状态名由寄存器A、B的二进制码定义:

S0=^b00;S1=^b01;S2=^b10;S3=^b11.其状态图如图4.24所示。

然后用状态机语言描述该状态图的转换。

下面只写出设计的核心部分:

DECLARATIONS

STATEMA=[A,B];

STATE0=[0,0];

STATE1=[0,1];

STATE2=[1.0];

STATE3=[1,1];

STATE_DIAGRAM

STATESTATE0:

Y=1;

GOTOSTATE1

STATESTATE1:

Y=0;

GOTOSTATE2

STATESTATE2:

Y=1;

GOTOSTATE3

STATESTATE3:

Y=1;

GOTOSTATE0;

P156例5用条件转移方程形式描述例4的4位二进制加法计数器。

解EOUATIONS

COUNT.CLK=CLK;

COUNT.AR=CLR;

WHEN!

CAI

THENCOUNT:

=COUNT.FB;

ELSECOUNT:

=COUNT.FB+1

CAO=Q3.Q&Q2.Q&Q1.Q&Q0.Q&CAO;

P157例6描述一个具有使能端的异或门。

TRUTH_TABLEINIC5

([EN,A,B]->C)

[0,.x.,.x.]->.z.;//使能端关闭,输出高阻态

[1,0,0]->0;

[1,0,1]->1;

[1,1,0]->1;

[1,1,1]->0;

P157例7描述一个简单的状态机。

TRUTH_TABLEINIC6

([A,B]:

>[C,D]->Y)

[0,0]:

>[0,1]->1;

[0,1]:

>[1,0]->0;

[1,0]:

>[1,1]->1;

[1,1]:

>[0,0]->1;

P157例8用状态图发描述例7的逻辑。

解从例7分析知,该状态机由4个状态,在时钟作用下,状态机在四个状态之间轮流装换。

状态机的状态由A,B两个寄存器(触发器)定义,在A,B分别为0,1时输出信号Y=0,其余为1.如图所示。

首先定义状态名,状态名由寄存器A,B的二进制码定义:

S0=^b00;S1=^b01;S2=^b10;S3=^b11

DECLARATIONS

STATEMA=[A,B];

STATE0=[0,0];

STATE1=[0,1];

STATE2=[1.0];

STATE3=[1,1];

STATE_DIAGRAM

STATESTATE0:

y=1;

GOTOSTATE1

STATESTATE1:

y=0;

GOTOSTATE2

STATESTATE2:

y=1;

GOTOSTATE3

STATESTATE3:

y=1;

GOTOSTATE0;

P158例9用状态图法描述下图所示的状态机。

解我们使用条件转移语句CASE。

CASE的转移条件是:

满足条件时为下一状态表达式。

在一个CASE语句中,可并列若干转移条件和状态表达式,但必须保证转移条件的互斥性。

STATE_DIAGRAM

STATES0;

CASEK==0:

S0;

K==1:

S1;

ENDCASE

STATES1;

CASEK==0:

S1;

K==1:

S2;

ENDCASE

STATES2;

CASEK==0:

S3;

K==1:

S2;

ENDCASE

STATES3;

CASEK==0:

S3;

K==1:

S0;

ENDCASE

例9层次说明举例

P171例7层次说明举例

为了解释层次说明,下面举个简单的的例子。

底层模块有2个,一个是3个输入端,1个输出端的与门AND1,另一个是2个输入端,1个输出端的或门OR1。

高层模块AND_OR_INVERT是一个与或非门,它将2个3与门或起来后求反。

高层模块:

MODULEAND_OR_INVERT

TITLE'1WIDEAND_OR_INVERTGATES'

Declarations//说明部

ANDINTERFACE(ia1,ia2,ia3->oa1);//与门接口说明

AND_1functional_blockAND;//与门例化1

AND_2functional_blockAND;//与门例化2

ORINTERFACE(ib1,i2->ob1)//或门接口说明

OR1_1functional_blockOR1;//或门例化

I1,i2,i3,i4,i5,i6,o1PIN

EQUATIONS//逻辑描述部

AND1_1.ia1=i1;

AND1_1.ia2=i2;

AND1_1.ia3=i3;

AND1_2.ia1=i1;

AND1_2.ia1=i2;

AND1_2.ia1=i3;

OR1_1.ib1=AND1_1.oa1;

OR2_1.ib2=AND1_2.oa1;

O1=!

OR1_1.ob1;

ENDAND_OR_INVERT;

低层模块1与门

MODULEAND1

INTERFACE(ia1,ia2,ia3->oa1);

TITLE'3inputsANDgate';

DECLARATIONS//说明部

ia1,ia2,ia3,oa1pin;

EOUATIONS//逻辑描述部

Oa1=ia1&ia2&ia3;

EndAND1

低层模块2或门

MODULEOR1//省略INTERFACE语句

TITLE'2inputsORgate';

ib1,ib2,ob1PIN;//说明部,省略了DECLARATIONS关键字

EOUATIONS//逻辑描述部

Ob1=ib1#ib2;

ENDOR1

例10电子琴

(1)顶层模块piano的ABEL语言源文件

MODULEpiano

DECLARATIONS

//lowermoduledeclaration

valueinterface(d1..d7,di->right);

value_0functional_blockvalue;

//input

clockpin11;//时钟输入100KHz

d1,d2,d3,d4pin9,40,36,3;//琴键

d5,d6,d7,dipin29,10,16,43;

//output

mupin38istype'reg';//音频输出

//node

mu2node;

mu0,mu1node;

q0..q7nodeistype'reg';//多模计数器

q=[q7..q0];

d=[di,d7..d1];

EQUATIONS

value_0.[di,d7..d1]=d;

//多模计数器,模191、模170、模151、模143、模128、模114、模101、模97

q.clk=clock;

q:

=(q+1)&!

mu2&value_0.right;

mu0=(q==190)&(d1==1)#(q==169)&(d2==1)#(q==150)&(d3==1)#(q==142)&(d4==1);

mu1=(q==127)&(d5==1)#(q==113)&(d6==1)#(q==100)&(d7==1)#(q==96)&(di==1);

mu2=mu0#mu1;

mu.clk=mu2;//二分频计数器

mu:

=!

mu;

END

(2)底层模块value的ABEL语言源文件:

MODULEvalue

DECLARATIONS

//input

d1..d7,dipin;//琴键1,2,3,4,5,6,7,i

//output

rightpin;//为1表示当前按键有效

//node

right0,right1node;

d=[d1..d7,di];

EQUATIONS

right0=(d==^b00000001)#(d==^b00000010)#(d==^b00000100)#(d==^b00001000);

right1=(d==^b00010000)#(d==^b00100000)#d==^b01000000)#(d==^b10000000);

right=right0#right1;//为1表示当前按键有效

END

例11P178例11名位Sequence的状态机源文件举例。

标示符A,B和C规定了各个状态。

这些标示符在说明部中赋予十进制的常量值,即为代表各状态的状态寄存器规定了位置。

A,B,C只是标示符,并不代表状态机的位值情况。

它们说明的值才为每个状态定义了状态寄存器的值;A=0,B=1,C=2.

MODULESequence

TITLE'statemachinexample'

Sequencedevice'p16r4'

q1,q0pin14,15istype'reg';

cock,enab,start,hold,resetpin1,11,4,2,3;

Haltpin17istype'reg';

In_B,in_Cpin12,13istype'com';

Sreg=[q1,q0];

"StateValue

A=0;B=1;C=2;

EQUATIONS

[q1,q0,halt].clk=clock;

[q1,q0,halt].oe=!

enab;

State_diagramsreg;

StateA:

"HoldinstateAuntilstartisactive

i_B=0;

In_C=0;

IT(start&!

reset)THENBWITHhalt:

=0;

ELSEAWITHhalt:

=halt.fb;

StateB:

"AdvancetostateCunlessresetisactive

i_B=1;"orholdisactive.turnonhaltindicator

In_C=0;"ifreset

IT(reset)THENAWITHhalt:

=1;

ELSEif(hold)THENBWITHhalt:

=0;

ELSECWITHhalt:

=0;

StateC"GobacktoAunlessholdisactive

i_B=0;"Resetoverrideshold

In_C=1;

IT(start&!

reset)THENCWITHhalt:

=0;

ELSEAWITHhalt:

=0;

ENDSequence

例12P179例12三选一多路器测试向量的具体例子。

MODULEmux12T4

TITLE'12tomultiplex';

A0..a3,b0..b3,c0..c3,s1,s0,y0,,y3pin;

H=[1,1,1,1];

L=[0,0,0,0];

X=.X.;

slect=[s1,s0];

Y=[y3..y0];

A=[a3..a0];

B=[b3..b0];

C=[c3..c0];

EQUATIONS

WHEN(select==0)THENy=a;

WHEN(select==1)THENy=b;

WHEN(select==2)THENy=c;

WHEN(select==3)THENy=c;

TEST_VECTORS([select,a,b,c]->y)

[0,1,x,x]->1;

[0,10,H,L]->10;

[0,5,H,L]->5;

[1,H,3,H]->3;

[1,10,7,H]->7;

[0,L,15,L]->15;

[2,L,L,8]->8;

[2,H,H,9]->9;

[2,LL,1]->1;

[3,H,H,0]->0;

[3,L,L,9]->9;

[3,H,L,0]->0;

ENDmux12T4

三、分频原理

100kHz/262Hz=382

100kHz/191=524Hz

524Hz/2=262Hz

分频原理

N分频

二分频