编码器的设计.docx

《编码器的设计.docx》由会员分享,可在线阅读,更多相关《编码器的设计.docx(18页珍藏版)》请在冰豆网上搜索。

编码器的设计

4线-2线编码器的设计

实验目的

1.利用Cadence软件完成一个4线-2线编码器的设计;

2.完成编码器的瞬态仿真、最高工作频率和功耗的性能指标测试;

3.学会自底向上地设计基于组合逻辑电路的编码器的设计;

4.掌握创建符号的步骤;

5.掌握编码器设计和仿真的步骤;

6.学会设置仿真参数,从而加深对Cadence软件仿真的熟悉度。

实验原理

编码和译码的问题在日常生活中经常遇到,数字系统中存储或者处理的信息,常常是用二进制码表示的。

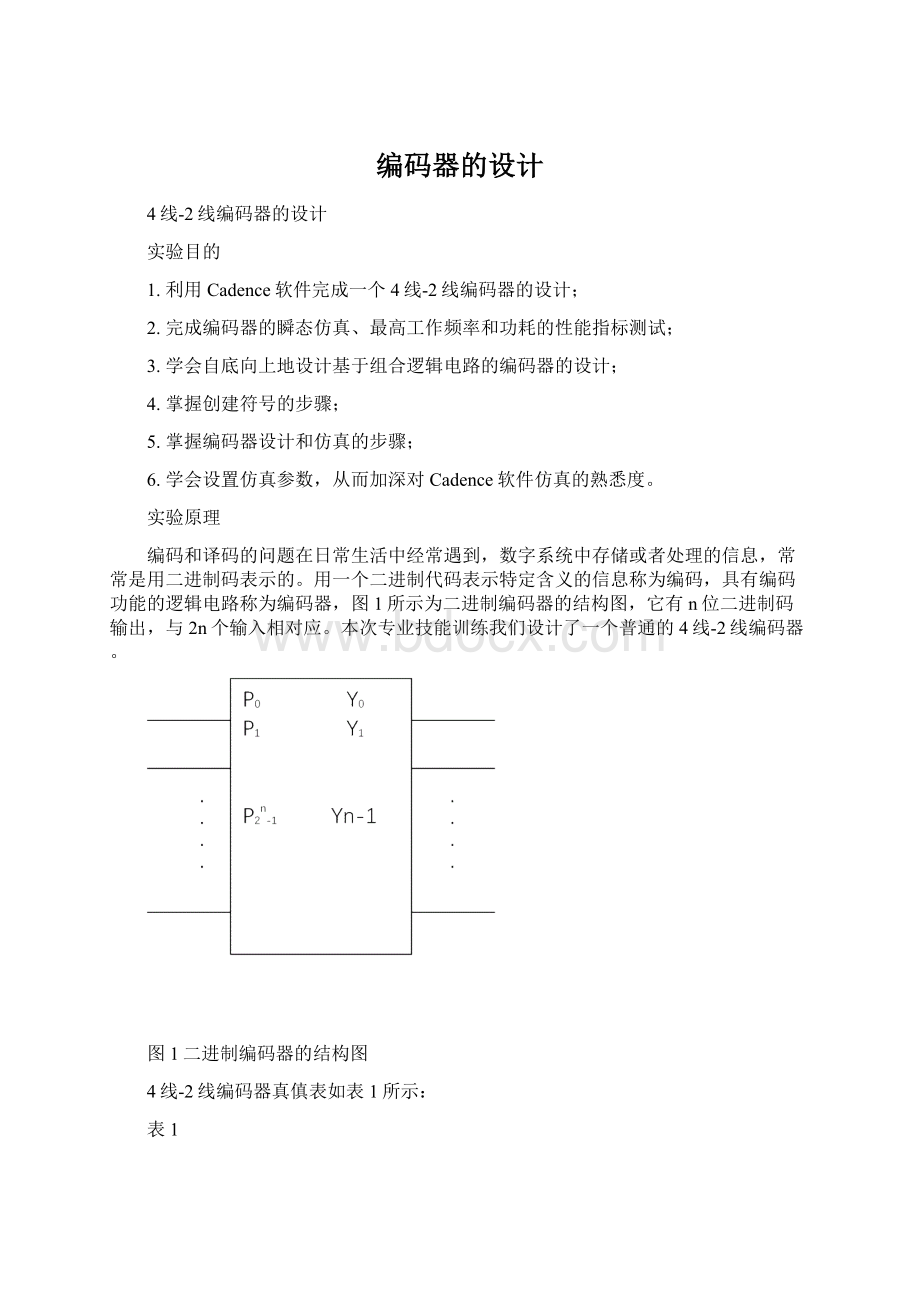

用一个二进制代码表示特定含义的信息称为编码,具有编码功能的逻辑电路称为编码器,图1所示为二进制编码器的结构图,它有n位二进制码输出,与2n个输入相对应。

本次专业技能训练我们设计了一个普通的4线-2线编码器。

图1二进制编码器的结构图

4线-2线编码器真傎表如表1所示:

表1

输入

输出

P0

P1

P2

P3

Y1

Y0

1

0

0

0

0

0

0

1

0

0

0

1

0

0

1

0

1

0

0

0

0

1

1

1

4个输入P0到P3为高电平有效信号,输出是两个二进制代码Y1Y0,任何时刻P0~P3中只能有一个取值为1,并且有一组对应的二进制码输出。

除表中的4种取值组合有效外,其余12种组合所对应的输出均应为0。

对于输入或输出变量,凡取1值的用原变量表示,取0值的用反变量表示,由真值表可以得到如下逻辑表达式:

Y1=

Y0=

根据逻辑表达式画出逻辑图,如下图2所示:

图24线-2线编码器逻辑图

实验内容及结果

本文的设计思路是首先完成4线-2线编码器所需要的各个模块的电路原理图设计,再将其创建成可以调用的符号,最后按照图2的编码器逻辑图完成首4线-2线编码器的设计。

首先需要创建一个库(如:

08063224)与各个视图单元inv、nand4、nor2和encode;注意在新建各个视图单元文件时应该都是建到库文件里,不然会提示文件位置报错。

其次按照要求完成编码器的瞬态工作频率功耗等前仿真。

实验的内容及结果具体如下:

1.反相器原理图及其符号的创建

开启虚拟机,进入RedHatLinux后,点击CIW窗口的→library,由此可创建库08063224(用来存放单元视图的文件夹)。

将库文件的路径设置在cadence目录下,Name栏输入库名,右侧TechnologyFile栏中选择Attachtoanexistingtechfile,点击窗口OK。

然后再点击→cellview,创建一个单元视图文件夹inv,LibraryName选取为,CellName可自定义为inv,设置viewname为schematic,设置tool为composerschematic,点击OK,此时便弹出SchematicEditing空白窗口。

输入反相器设计原理图的结果如下图3所示:

图3反相器原理图

具体的操作步骤:

①添加元件:

在原理编辑窗口中,选择Add→Intance,打开Intance窗口,点击Browse按钮,弹出LibraryBrowser窗口,在Library一栏中选择gpdk180,Cell一栏选择pmos,Cellview一栏选择symbol,都选好后并且设置pmos的宽长为4U就可以点击close,将LibraryBrower窗口关闭,此时AddInstance窗口的Cell和View栏就会被填好,就可以将pmos管添加到原理编辑窗口中了。

同样可添加nmos管,并且设置nmos的宽长为2U。

添加Source和Ground,在Library一栏中选analoglib,Cell一栏中选vcc,Cellview一栏中选symbol。

添加Ground与添加Source的方法相同。

②添加Pin:

点击Add→pin,会出现Addpin窗口,在PinNames栏中输入in,Direction设置为input,完成输入端的添加;同理再添加一个输出管脚,在PinNames栏中输入out,Direction设置为output完成输出端的添加。

③连线:

点击Add→Wire(Narrow),将应该要连线的地方连接起来,点击即可。

若需要移动的时候也是先选中,按M再点击到相应的位置,切记不能有拖动的操作。

④检查并保存,在画完原理图后,需要检查原理图是否有错,点击Design→CheckandSave,然后就可在CIW窗口中观察是不有错或警告。

生成的反相器符号结果如下图4所示:

图4反相器符号

具体的操作步骤:

①在Schematic中,点击Design→CreateCellview→FromCellview弹出CellFromCellview窗口,图中LibraryName和CellName会自动填写我们所要创建符号的原理图名称,点击OK,弹出SymbolGenerationOption窗口,在填好各项后进入SymbolEditing窗口编辑符号。

②点击Add→shape,可通过其中的Line和Circle各项来编辑符号形状,结果如上图4所示。

③点击Design→CheckandSave,可在CIW窗口中观察是不有错或警告,检查并保存编辑好的符号。

2.四输入与非门原理图及其符号的创建

在CIW窗口点击→cellview,创建一个单元视图文件夹nand4,LibraryName选取为08063224,CellName自定义为nand4,设置viewname为schematic,设置tool为composerschematic,点击OK即可。

输入的四输入与非门设计原理图结果如下图5所示:

图5四输入与非门原理图

先添加元件,在analogLib库中选择vcc与gnd各一个,按照图添加所需元件。

在gpdk180库中选择pmos与noms各4个,并且设置pmos的宽长为4U,nmos的宽长为2U。

然后添加输入输出管脚,再进行连线。

生成的四输入与非门符号结果如下图6所示,操作步骤和创建反相器的符号方法相似。

图6四输入与非门符号

3.二输入或非门原理图及其符号的创建

二输入或非门原理图设计:

在CIW窗口,点击→cellview创建一个单元视图文件夹nor2,LibraryName选取为08063224,CellName自定义为nor2,设置viewname为schematic,设置tool为composerschematic,点击OK即可,打开电路原理图设计窗口。

添加元件在gpdk180中选择两个pmos和两个nmos,在analoglib库中选择vcc和gnd各一个,即按下图7所示添加所须元件;添加输入端管脚为a、b;输出端管脚为y;连线,按设计的原理图连线。

检查电路结构与连线,使用checkandsave

图标检验查错,修改并存档。

输入的二输入或非门设计原理图结果如下图7所示:

图7或非门设计原理图

创建符号:

从原理图打开逻辑符号窗口,同创建反相器符号方法,对符号进行编辑,最终形成nor2逻辑符号如图8所示:

图8二输入或非门符号

4.利用设计好的符号设计顶层4-2线编码器原理图

电路结构:

构成4-2线编码器的电路形式主要有非门、四输入与非门结构和二输入或非门结构,CMOS结构的4-2线编码器电路如图9所示:

添加输入pin为P0、P1、P2和P3;输出pin为Y1与Y0。

图94-2线编码器原理图

5.4-2线编码器的瞬态仿真

在设计好的4-2线编码器原理图编辑窗口,点击Tools→AnalogEnvironment,弹出AnalogDesignEnvironment,首先设置库的路径,点击Setup→Modellibraries,然后点击Browse,将库路径设为/home/irio//gpdk180/models/spectre/gpdk.scs,将Section设为stat。

然后点击Setup→Stimuli,在弹出的SetupAnalogStimuli窗口,设置4个输入参数P0、P1、P2、P3和GlobalSources,参数设置方法如下图10—13所示:

(在设置这些参数时都要点击Enabled和Change使得参数从OFF状态变到ON状态)

图10输入参数P0的设置

图11输入参数P1的设置

图12输入参数P2的设置

图13输入参数P3的设置

①点击Analyses→Choose,选择分析类型为Tran瞬态分析,StopTime仿真时间参数设置16n,并选中moderate和Enabled。

②点击Output→SaveAll,选择输出,输出信号选择allpub,器件电流选择all,点击OK。

此时我们再将输出结果选中,操作步骤:

Outputs→ToBePlotted→SelectOnSchematic。

在原理图中选中输入端P0、P1、P2、P3和输出端Y1和Y2,再返回仿真的界面如图14所示。

图14瞬态仿真窗口

③点击Simulation→NelistandRun,进行仿真,点击后会弹出WelcometoSpectre窗口,点击OK就开始仿真。

如果提示有错误,就需要查找错误并修改原理图。

若无错误,运行后就会弹出仿真波形如图15所示。

图15瞬态仿真波形图

直流分析

创建新的单元视图Pnvfz,并调用实验三中生成的反相器符号来连接反相器的仿真电路,输入原理图步骤同实验二。

只是现在单元视图中多了一个反相器的符号,同时直流分析需要对电路外加一个激励。

具体电路图如图4所示。

图4反相器直流分析原理图

此时Vcc不需要再进行设值,而是要对外接激励V0设置为1.8V,对V1进行直流扫描和参数设置:

点击SelectComponent,选择电路图中的V1,弹出SelectComponentParameter窗口,选中窗口中dc,点击OK。

运行后仿真波形如图5所示。

注意:

仿真波形中Net2为输入电压,out为输出电压。

6.4线-2线编码器的最高工作频率仿真

同时直流分析需要对电路外加一个激励。

Y0的最高工作频率:

1.998G

Y1的最高工作频率:

2.0000G

P0的最高工作频率:

0.998G

P1的最高工作频率:

0.998G

P2的最高工作频率:

0.998G

P3的最高工作频率:

0.998G

最终的最高工作频率波形:

7.4线-2线编码器的功耗仿真

最终的电流的值:

0.00112A也即1.1286mAP=UI=1.8V*I=0.00203148W

结果分析

问题分析

1.在原理图设计时连线一定不能十字相交,否则在进行checkandsave操作后CIW窗口会出现警告,但可以丁相交。

2.在设计顶层4-2线编码器原理图时添加输入端时,一开始命名为I0、I1、I2、I3,但checkandsave没通过出现了很多的警告大体意思是命名有冲突,将I0、I1、I2、I3改为P0、P1、P2、P3后,就没有警告,所以可能是因为反相器符号的输入端命名为in与I0、I1、I2、I3有相同的英文字母。

3.顶层4-2线编码器原理图时添加激励进行仿真时的线性电压源一定要和各个模块所加的电源Vcc相同,而不是Vdd,否则在进行仿真时会报错,并且出现的错误提示表明是致命的错误。

4.为了方便仿真验证,在Schematic中要对所有元件进行参数定义,选取模型并定义器件宽长比等。

5.原理图输入时要表明各MOS管子的尺寸,不然仿真的波形会不理想,在本次设计中设置pmos的宽长为4U,nmos的宽长为2U。

实际中可以通过严格按要求设置MOS管的宽长,以减少管子的功耗。

6.生成符号时应注意要将标有Instancename删去,否则在其他电路上调用此符号时器件会出错。

另外在添加输入(出)端口时一定要标明是INPUT还是OUTPUT,否则也会报错。

7.若仿真时出现错误,可返回到仿真参数设置中检查参数的设置是否正确,各个模块的原理图和符号是否正确,反复修改错误才能得到最终正确的输出仿真曲线。

心得体会

通过这次专业综合技能训练,我们学会了从列真值表

上述编码器存在一个问题,如果P0~P3中有2个或2个以上的取值同时为1,输出会出现错误编码。

例如,P2和P3同时为1时,Y1Y0为00,此时输出既不是对P2或P3的编码,更不是对P0的编码。

而实际应用中,经常会遇到两个以上的输入同时为1的情况。

因此实际应用需要根据轻重缓急,规定好这些控制对象允许操作的先后次序,即优先级别,也就是我们所熟悉的优先编码器。