微型计算机原理及应用课程教案1汇总.docx

《微型计算机原理及应用课程教案1汇总.docx》由会员分享,可在线阅读,更多相关《微型计算机原理及应用课程教案1汇总.docx(21页珍藏版)》请在冰豆网上搜索。

微型计算机原理及应用课程教案1汇总

第1章 计算机基础知识

1.1数制

数制是人们利用符号来记数的科学方法。

数制可以有很多种,但在计算机的设计与使用上常使用的则为十进制、二进制、八进制和十六进制。

1.1.1数制的基与权

数制所使用的数码的个数称为基;数制每一位所具有的值称为权。

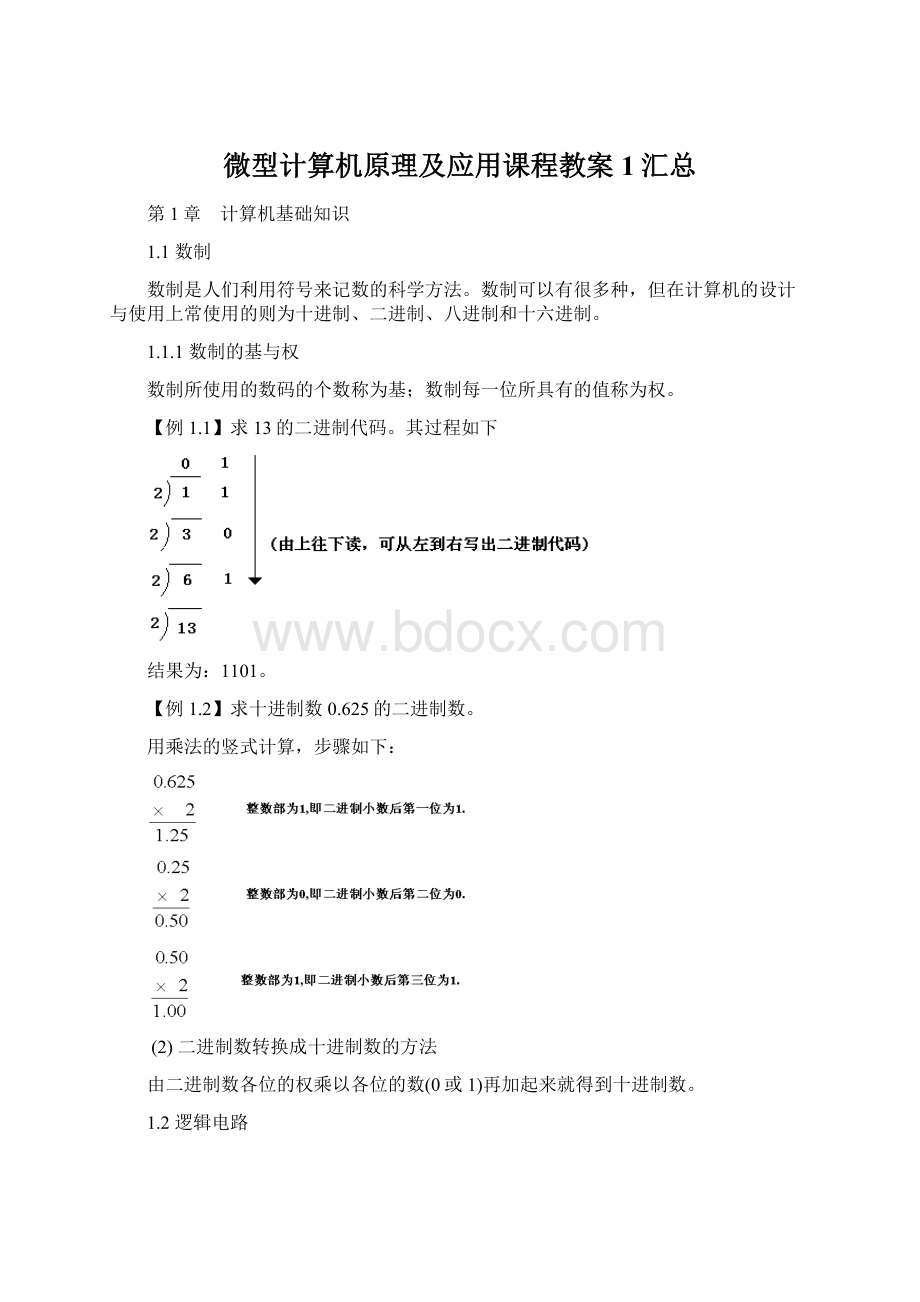

【例1.1】求13的二进制代码。

其过程如下

结果为:

1101。

【例1.2】求十进制数0.625的二进制数。

用乘法的竖式计算,步骤如下:

(2)二进制数转换成十进制数的方法

由二进制数各位的权乘以各位的数(0或1)再加起来就得到十进制数。

1.2逻辑电路

逻辑电路由其3种基本门电路(或称判定元素)组成。

图1.1是基本门电路的名称、符号及表达式。

在这3个基本门电路的基础上,还可发展成如图1.2那样更复杂的逻辑电路。

其中,最后一个叫作缓冲器(buffer),为两个非门串联以达到改变输出电阻的目的。

如果A点左边电

图1.1

图1.2

路的输出电阻很高,则经过这个缓冲器之后,在Y点处的输出电阻就可以变得低许多倍,这样就能够提高带负载的能力。

1.4.6二进制数的减法运算

所以,在二进制中,常用反码加1的方法来获得补码。

这在计算机中非常方便,因为二进制电路由原码求反码是很容易的,这在下面就会看到。

有了补码,就可以将减法变成加法来运算了。

请看下面的例子。

【例1.12】求Y=8(10)-4(10)=?

解:

因为 A=8(10)=1000

(2) B=4(10)=0100

(2)

则 B′=1011+1=1100

(2)

于是 Y=A-B=A+B′=1000+1100=1 0100=0100

(2)=4(10)

进位,应舍去

【例1.13】求

(即求15减10之差)

设

)则:

所以

(结果为5)

进位,舍去

1.4.7可控反相器及加法/减法电路

利用补码可将减法变为加法来运算,因此需要有这么一个电路,它能将原码变成反码,并使其最小位加1。

图1.8的可控反相器就是为了使原码变为反码而设计的。

这实际上是一个异或门(异门),两输入端的异或门的特点是:

两者相同则输出为0,两者不同则输出为1。

图1.8可控反相器

利用这个特点,在图1.7的4位二进制数加法电路上增加4个可控反相器并将最低位的半加器也改用全加器,就可以得到如图1.9的4位二进制数加法器/减法器电路了,因为这个电路既可以作为加法器电路(当SUB=0),又可以作为减法器电路(当SUB=1)。

图1.9二进制补码数加法器/减法器

如果有下面两个二进制数:

则可将这两个数的各位分别送入该电路的对应端,于是:

当SUB=0时,电路作加法运算:

A+B。

当SUB=1时,电路作减法运算:

A-B。

图1.9电路的原理如下:

当SUB=0时,各位的可控反相器的输出与B的各位同相,所以图1.9和图1.7的原理完全一样,各位均按位相加。

结果

,而其和为:

。

当SUB=1时,各位的反相器的输出与B的各位反相。

注意,最右边第一位(即S0位)也是用全加器,其进位输入端与SUB端相连,因此其C0=SUB=1。

所以此位相加即为:

其他各位为:

因此其总和输出

,即:

=

=

=

当然,此时C4如不等于0,则要被舍去。

2.1算术逻辑单元

顾名思义,这个部件既能进行二进制数的四则运算,也能进行布尔代数的逻辑运算。

第1章已讲过,二进制数的运算电路只能算加法。

增加可控反相器后,又能进行减法,所以上章最后介绍的二进制补码加法器/减法器就是最简单的算术部件。

但是,只要利用适当的软件配合,乘法也可以变成加法来运算,除法也可变成减法来运算。

如果在这个基础上,增加一些门电路,也可使简单的ALU进行逻辑运算。

所谓逻辑运算就是指“与”运算和“或”运算。

为了不使初学者陷入复杂的电路分析之中,本教程不打算在逻辑运算问题上开展讨论。

图2.1

ALU的符号一般画成图2.1那样。

A和B为两个二进制数,S为其运算结果,control为控制信号(见图1.9的控制线端SUB)。

2.2触发器

触发器(trigger)是计算机的记忆装置的基本单元,也可说是记忆细胞。

触发器可以组

成寄存器,寄存器又可以组成存储器。

寄存器和存储器统称为计算机的记忆装置。

微型计算机所用触发器一般用晶体管元件而不用磁性元件。

这是因为晶体管元件可以制成大规模的集成电路,体积可以更小些。

从晶体管电路基础中,我们已经知道触发器可以由两个晶体管组成的对称电路来构成,我们也知道触发电路中有所谓单稳态触发电路和双稳态触发电路,这里不打算重复这些电路的原理图和工作特点了。

下面简要地介绍一下RS触发器、D触发器和JK触发器,因为这些类型的触发器是计算机中最常见的基本元件。

图2.11JK触发器的符号

2.3寄存器

寄存器(register)是由触发器组成的。

一个触发器就是一个一位寄存器。

由多个触发器可以组成一个多位寄存器。

寄存器由于其在计算机中的作用之不同而具有不同的功能,从而被命名为不同的名称。

常见的寄存器有:

缓冲寄存器——用以暂存数据;移位寄存器——能够将其所存的数据一位一位地向左或向右移;计数器——一个计数脉冲到达时,会按二进制数的规律累计脉冲数;累加器——用以暂存每次在ALU中计算的中间结果。

下面分别介绍这些寄存器的工作原理及其电路结构。

2.3.1缓冲寄存器

其基本工作原理为:

设有一个二进制数,共有4位数:

X=X3X2X1X0

要存到这个缓冲寄存器(buffer)中去,此寄存器是由4个D触发器组成的。

将X0,X1,X2,X3分别送到各个触发器的D0,D1,D2,D3端去,只要CLK的正前沿还未到来,则Q0,Q1,Q2,Q3就不受X0,X1,X2,X3的影响而保持其原有的数据。

只有当CLK的正前沿来到时,Q0,Q1,Q2,Q3才接受D0,D1,D2,D3的影响,而变成:

Q0=X0

Q1=X1

Q2=X2

Q3=X3

结果就是:

Q=Q3Q2Q1Q0=X3X2X1X0=X。

这就叫做将数据X装到寄存器中去了。

如要将此数据送至其他记忆元件去,则可由Y0,Y1,Y2,Y3各条引线引出去。

可控缓冲寄存器:

图2.12的缓冲寄存器的数据X输入到Q只是受CLK的节拍管理,即只要一将X各位加到寄存器各位的D输入端,时标节拍一到,就会立即送到Q去。

这有时是不利而有害的,因为也许我们还想让早已存在其中的数据多留一些时间,但由于不可控之故,在CLK正前沿一到就会立即被来到门口的数据X替代掉。

图2.124位缓冲寄存器电路原理图

为此,我们必须为这个寄存器增设一个可控的“门”。

这个“门”的基本原理如图2.13所示,它是由两个与门一个或门以及一个非门所组成的。

图2.13寄存器的装入门LOAD

在X0端送入数据(0或1)后,如LOAD端(以下简称为L端)为低电位,则右边的与门被阻塞,X0过不去,而原来已存在此位中的数据由Q0送至左边的与门。

此与门的另一端输入从非门引来的与L端反相的电平,即高电位。

所以Q0的数据可以通过左边的与门,再经或门而送达D0端。

这就形成自锁,即既存的数据能够可靠地存在其中而不会丢失。

如L端为高电位,则左边与门被阻塞而右边与门可让X0通过,这样Q0的既存数据不再受到自锁,而X0可以到达D0端。

只要CLK的正前沿一到达,X0即被送到Q0去,这时就叫做装入(LOAD)。

一旦装入之后,L端又降至低电平,则利用左边的与门,X0就能自锁而稳定地存在Q0中。

图2.14可控缓冲寄存器

要记住,以后我们一提到“L门”,大家就要想到图2.13的电路结构及其作用:

高电平时使数据装入,低电平时,数据自锁在其中。

对于多位的寄存器,每位各自有一套如图2.13一样的电路。

不过只用一个非门,并且只有一个LOAD输入端,如图2.14所示。

可控缓冲寄存器的符号一般画成图2.15那样,LOAD为其控制门,而CLR为高电平时则可用以清除,使其中各位变为0。

图2.15可控缓冲寄存器的符号

2.3.2移位寄存器

移位寄存器(shiftingregister)能将其所存储的数据逐位向左或向右移动,以达到计算机在运行过程中所需的功能,例如用来判断最左边的位是0或1等。

电路原理图如图2.16所示。

图2.16移位寄存器简化原理图

左移寄存器如图2.16(a)所示,当Din=1而送至最右边的第1位时,D0即为1,当CLK的正前沿到达时,Q0即等于1。

同时第2位的D1也等于1。

当CLK第2个正前沿到达时,Q1也等于1。

结果可得下列的左移过程:

CLK前沿未到 Q=Q3Q2Q1Q0=0000

第1前沿来到 Q=0001

第2前沿来到 Q=0011

第3前沿来到 Q=0111

第4前沿来到 Q=1111

第5前沿来到,如此时Din仍为1,则Q不变,仍为1111。

当Q=1111之后,改变Din,使Din=0,则结果将是把0逐位左移:

第1前沿来到 Q=1110

第2前沿来到 Q=1100

第3前沿来到 Q=1000

第4前沿来到 Q=0000

由此可见,在左移寄存器中,每个时钟脉冲都要把所储存的各位向左移动一个数位。

右移寄存器如图2.16(b)所示。

图2.16(b)与图2.16(a)之差别仅在于各位的接法不同,而且输入数据Din是加到左边第1位的输入端D3。

根据上面的分析,当Din=1时,随着时钟脉冲而逐步位移是这样的:

CLK前沿未到Q=0000

第1前沿来到Q=1000

第2前沿来到Q=1100

第3前沿来到Q=1110

第4前沿来到Q=1111

由此可见,在右移寄存器中,每个时钟脉冲都要把所存储的各位向右移动一个位置。

可控移位寄存器:

和缓冲寄存器一样,在整机运行中,移位寄存器也需要另有控制电路,以保证其在适当时机才参与协调工作。

这个电路也和图2.13一样,只要在每一位的电路上增加一个这样的LOAD门(L门)即可以达到控制的目的。

可控移位寄存器的符号如图2.17所示,其中新出现的符号的意义是:

SHL——左移(shifttotheleft)

SHR——右移(shifttotheright)

图2.17可控移位寄存器的符号

2.3.3计数器

计数器(counter)也是由若干个触发器组成的寄存器,它的特点是能够把存储在其中的数字加1。

计数器的种类很多,有行波计数器、同步计数器、环形计数器和程序计数器等。

(1)行波计数器(travellingwavecounter)的特点是:

第1个时钟脉冲促使其最低有效位(leastsignificantbit,LSB)加1,由0变1。

第2个时钟脉冲促使最低有效位由1变0,同时推动第2位,使其由0变1。

同理,第2位由1变0时又去推动第3位,使其由0变1,这样有如水波前进一样逐位进位下去。

图2.18就是由JK触发器组成的行波计数器的工作原理图。

图2.18中的各位的J,K输入端都是悬浮的,这相当于J,K端都是置1的状态,亦即是各位都处于准备翻转的状态。

只要时钟脉冲边缘一到,最右边的触发器就会翻转,即Q由0转为1或由1转为0。

各位的JK触发器的时钟脉冲输入端都带有一个“气泡”,这表示是串有一个反相门(非门),这样,只有时钟脉冲的后沿(产生负的尖峰电压)才能为其所接受。

因此,可得计数步骤如下:

图2.18行波计数器的工作原理图

开始时使CLR由高电位变至低电位(这也是由于有“气泡”在CLR输入端之故),则计数器全部清除,所以:

Q=Q3Q2Q1Q0=0000

第1时钟后沿到Q=0001

此Q0由低电位(0)升至高电位

(1),产生的是电位上升的变化,由于有“气泡”在第2位的时钟脉冲输入端,所以第2个触发器不会翻转,必须在Q0由1降为0时才会翻转。

接着:

第2时钟后沿到Q=0010

第3时钟后沿到Q=0011

第4时钟后沿到Q=0100

第5时钟后沿到Q=0101

第6时钟后沿到Q=0110

第7时钟后沿到Q=0111

第8时钟后沿到Q=1000

…………

第15时钟后沿到Q=1111

第16时钟后沿到Q=0000

在第16个时钟脉冲到时,计数器复位至0,因此这个计数器可以计由0至15的数。

如

图2.19可控计数器的电路原理图

果要计的数更多,就需要更多的位,即更多的JK触发器来组成计数器。

如8位计数器可计由0至255的数,12位计数器可计由0至4095的数,16位则可计由0至65535的数。

图2.19是可控计数器的电路原理图。

图2.18中的J,K输入端是悬浮的,所以每次时钟脉冲到时,它都要翻转一次。

图2.19中的各个J,K输入端连在一起引出来,由计数控制端COUNT的电位信号来控制。

当COUNT为高电位时,JK触发器才有翻转的可能。

当COUNT为低电位时就不可能翻转。

图2.20是这种计数器的符号。

图2.20可控计数器的符号

(2)同步计数器(synchronouscounter),行波计数器的工作原理是在时钟边缘到来时开始计数,由右边第一位(LSB)开始,如有进位的话则要一位一位的推进。

而每一位触发器都需要建立时间tp(tp约为10纳秒)。

如果是16位的计数器,则最大可能的计一个数的时间为160纳秒,这就显得太慢了。

同步计数器是将时钟脉冲同时加到各位的触发器的时钟输入端,而将前一位的输出端(Q)接到下一位的JK端去。

这样可以使计数器计数时间只相当于一个触发器的建立时间tp,所以同步计数器在很多微型机中常被使用。

为了避免初学者陷到电路分析中去,这里就不介绍具体线路了。

(3)环形计数器(ringcounter)也是由若干个触发器组成的。

不过,环形计数器与上述计数器不一样,它只是仅有唯一的一个位为高电位,即只有一位为1,其他各位为0。

图2.21是由D触发器组成环形计数器的电路原理图。

图2.21环形计数器的电路原理图

当CLR端有高电位输入时,除右边第1位(LSB)外,其他各位全被置0(因清除电位CLR都接至它们的CLR端),而右边第1位则被置1(因清除电位CLR被引至其PR端)。

这就是说,开始时Q0=1,而Q1,Q2,Q3全为0。

因此,D1也等于1,而D0=Q3=0。

在时钟脉冲正边缘来到时,则Q0=0,而Q1=1,其他各位仍为0。

第2个时钟脉冲前沿来到时,Q0=0,Q1=0,而Q2=1,Q3仍=0。

这样,随着时钟脉冲而各位轮流置1,并且是在最后一位(左边第1位)置1之后又回到右边第1位,这就形成环形置位,所以称为环形计数器。

环形计数器的符号如图2.22所示。

图2.22环形计数器的符号

环形计数器不是用来计数用,而是用来发出顺序控制信号的,这在计算机的控制器中是一个很重要的部件。

(4)程序计数器(programcounter)也是一个行波计数器(也可用同步计数器)。

不过它不但可以从0开始计数,也可以将外来的数装入其中,这就需要一个COUNT输入端,也要有一个LOAD门,程序计数器的符号如图2.23所示。

2.23程序计数器的符号

2.3.4累加器

累加器也是一个由多个触发器组成的多位寄存器,累加器的英文为accumulator,译作累加器,似乎容易产生误解,以为是在其中进行算术加法运算。

其实它不进行加法运算,而是作为ALU运算过程的代数和的临时存储处。

这种特殊的寄存器在微型计算机的数据处理中担负着重要的任务。

累加器除了能装入及输出数据外,还能使存储其中的数据左移或右移,所以它又是一种移位寄存器。

累加器的符号如图2.24所示。

图2.24累加器的符号

2.4三态输出电路

由于记忆元件是由触发器组成的,而触发器只有两个状态:

0和1,所以每条信号传输线只能传送一个触发器的信息(0或1)。

如果一条信号传输线既能与一个触发器接通,也可以与其断开而与另外一个触发器接通,则一条信息传输线就可以传输随意多个触发器的信息了。

三态输出电路(或称三态门)就是为了达到这个目的而设计的。

三态输出电路可以由两个或非门和两个NMOS晶体管(T1,T2)及一个非门组成,如图2.25所示。

当ENABLE(选通端)为高电位时,通过非门而加至两个或非门的将为低电位,则两个或非门的输出状态将决定于A端的电位。

当A为高电位,G2就是低

电位,而G1为高电位,因而T1导通而T2截止,所以B端也呈现高电位(VB≈VDD);当A为低电位,G2将呈现高电位而G1为低电位,因而T1截止而T2导通,所以B也呈现低电位(VB≈0)。

这就是说,在选通端(ENABLE端)为高电位时A的两种可能电平(0和1)都可以顺利地通到B输出去,即E=1时,B=A。

当选通端E为低电位时,通过非门加至两个或非门的将为高电位。

此时,无论A为高或低电位,两个或非门的输出都是低电位,即G1与G2都是低电位。

所以T1和T2同时都是截止状态。

这就是说,在选通端(E端)为低电位时,A端和B端是不相通的,即它们之间存在着高阻状态。

三态输出电路的符号如图2.25(b)所示。

图2.25称为单向三态输出电路。

有时需要双向输出时,一般可以用两个单向三态输出电路来组成,如图2.26所示。

A为某个电路装置的输出端,C为其输入端。

当EOUT=1时,B=A,即信息由左向右传输;EIN=1时,C=B,即信息由右向左传输。

图2.25三态输出电路及的符号图2.26双向的三态输出电路

三态门(E门)和装入门(L门)一样,都可加到任何寄存器(包括计数器和累加器)电路上去。

这样的寄存器就称为三态寄存器。

L门专管对寄存器的装入数据的控制,而E门专管由寄存器输出数据的控制。

有了L门和E门就可以利用总线结构,使计算机的信息传递的线路简单化,控制器的设计也更为合理而易于理解了。

2.5总线结构

设有A,B,C和D4个寄存器,它们都有L门和E门,其符号分别附以A,B,C和D的下标。

它们的数据位数,设有4位,这样只要有4条数据线即可沟通它们之间的信息来往。

图2.27就是总线结构的原理图。

图2.27总线结构的原理图

如果将各个寄存器的L门和E门按次序排成一列,则可称其为控制字CON:

CON=LAEALBEBLCECLDED

为了避免信息在公共总线W中乱窜,必须规定在某一时钟节拍(CLK为正半周),只有一个寄存器L门为高电位,和另一寄存器的E门为高电位。

其余各门则必须为低电位。

这样,

图2.28总线结构的符号图

E门为高电位的寄存器的数据就可以流入到L门为高电位的寄存器中去。

控制字中哪些位为高电平,哪些位为低电平,将由控制器发出并送到各个寄存器上去。

为了简化作图,不论总线包含几条导线,都用一条粗线表示。

在图2.28中,有两条总线,一条称数据总线,专门让信息(数据)在其中流通。

另一条称为控制总线,发自控制器,它能将控制字各位分别送至各个寄存器上去。

控制器也有一个时钟,能把CLK脉冲送到各个寄存器上去。

2.6存储器

存储器(memory)是计算机的主要组成部分。

它既可用来存储数据,也可用以存放计算机的运算程序。

存储器由寄存器组成,可以看做一个寄存器堆,每个存储单元实际上相当于一个缓冲寄存器。

根据使用不同,存储器分为两大类:

只读存储器(ROM)和随机存取存储器(RAM)。

下面将分别介绍这两种存储器的结构和性能。

在微型计算机中采用半导体器件作为记忆元件,这样体积小些,可以制成大规模集成电路。

每个存储单元所存储的内容称为一个字(word)。

一个字由若干位(bit)组成。

比如8个记忆元件的存储单元就是一个8位的记忆字称为一个字节(byte),由16个记忆单元组成的存储单元就是一个16位的记忆字(由两个字节组成)。

一个存储器可以包含数以千计的存储单元。

所以,一个储存器可以存储很多数据,也可以存放很多计算步骤——称为程序(program)。

为了便于存入和取出,每个存储单元必须有一个固定的地址。

因此,存储器的地址也必定是数以千计的。

为了减少存储器向外引出的地址线,在存储器内部都自带有译码器。

根据二进制编码译码的原理,除地线公用之外,n根导线可以译成2n个的地址号。

例如,一个16×8的存储器如图2.29所示,它是一个有16个存储单元,每个单元为8位记忆字(即每单元存一个字节)的集成电路片,它将有4条地址线A0,A1,A2,A3和8条数据线D0,D1,D2,D3,D4,D5,D6,D7。

如16个存储单元为R0,R1,…,R15。

它们是A0,A1,A2,A3的全部组合。

图2.2916×8的存储器

顺便提一句,当地址线为10条时,n=10,则可编地址号为1,024个,或称为1K字节。

这里的1K和习惯为1000不一样,请务必注意。

A0~A3就是地址总线中的4根译码线。

当存储器的存储单元愈多,则地址总线中的译码线,亦即存储器集成电路片的地址线愈多。

在一般微型计算机中,地址线大都为16条。

16条地址线,可译出64K个地址。

在286/386/486中采用20条地址线。

2.6.1只读存储器

这是用以存放固定程序的存储器,一旦程序存放进去之后,即不可改变。

也就是说,不

图2.30只读存储器原理

能再“写”入新的字节,而只能从中“读”出其所存储的内容,因此称为只读存储器。

图2.30是一个8×4ROM集成电路片的内部电路原理图。

右半部分由矩阵电路及半导体二极管组成8个4位的存储单元。

二极管的位置是由制造者配置好了而不可更改的。

一条横线相当于一个存储单元,而一条竖线相当于一位。

所以8条横线组成8个存储单元,4条竖线成为一个4位的字。

二极管连接到的竖线,则为该位置1。

无二极管相连的竖线,则为该位置0。

输出电信号是取自限流电阻R上的电位。

为了可控,每条数据线都加一个三态输出门(E门)。

这样,只有在E门为高电位时,才有可能输出此ROM中的数据。

左半部为地址译码器电路。

因为是8个地址号,所以只需3条地址线:

A2,A1,A0,每条地址线都并以一个非门,而得3条非线:

A2,A1,A0。

这6条线通过8个与门即可译成8个地址号。

例如,R0的地址号为A2A1A0=000,当地址线上出现A2A1A0=000时,则R0所在的那条横线所连接的与门1将导通,而使此横线为高电位。

而此时R0的4条竖线中只有最右一条接有二极管。

它将横线的高电位引至下面的限流电阻R上。

所以电阻R的上端出现高电位。

其他3条竖线由于无二极管与R0横线相连,所以它们各自的限流电阻上无电流流过而呈现为低电平(地电位)。

当E门为高电位时数据线D3D2D1D0将送出数据为0001,其他各个存储单元也可由地址线的信号之不同而选出,并通过E门将数据输出去。

图2.31为ROM的符号图,图2.31(a)是8个存储单元,每个4位(即半个字节),所以写成8×4ROM。

图2.31(b)为通用写法,m×nROM意即为m个存储单元,其中每个为n位。

图2.31ROM的符号

存储地址寄存器(memoryaddressregister,MAR):

作为存储器的一个附件,存储地址寄存器是必需的。

它将所要寻找的存储单元的地址暂存下来,以备下一条指令之用。

存储地址寄存器也是一个可控缓冲寄存器,它具有L门以控制地址的输入。

它和存储器的联系是双态的,即地址一进入MAR就立即被送到存储器去,如图2.32所示。

图2.32MAR和ROM的联系

【例2.1】程序计数器PC,存储地址寄存器MAR和ROM通过总线的联系如图2.33所示。

图2.33取数周期的信号流通

设控制字依次是:

(1)CPEPLMER=0110

(2)CPEPLMER=0001

(3)CPEPLMER=1000

问:

它们之间的信息是如何流通的?

解开机时,先令CLR=1,则PC=0000

(1)