CameraLink接口时序控制.docx

《CameraLink接口时序控制.docx》由会员分享,可在线阅读,更多相关《CameraLink接口时序控制.docx(9页珍藏版)》请在冰豆网上搜索。

CameraLink接口时序控制

CameraLink接口

1.CameraLink接口简介

1.1CameraLink标准概述

CameraLink技术标准是基于NationalSemiconductor公司的ChannelLink标准发展而来的,而ChannelLink标准是一种多路并行LVDS传输接口标准。

低压差分信号(LVDS)是一种低摆幅的差分信号技术,电压摆幅在350mV左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在。

90年代美国国家半导体公司(NationalSemiconductor)为了找到平板显示技术的解决方案,开发了基于LVDS物理层平台的ChannelLink技术。

此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。

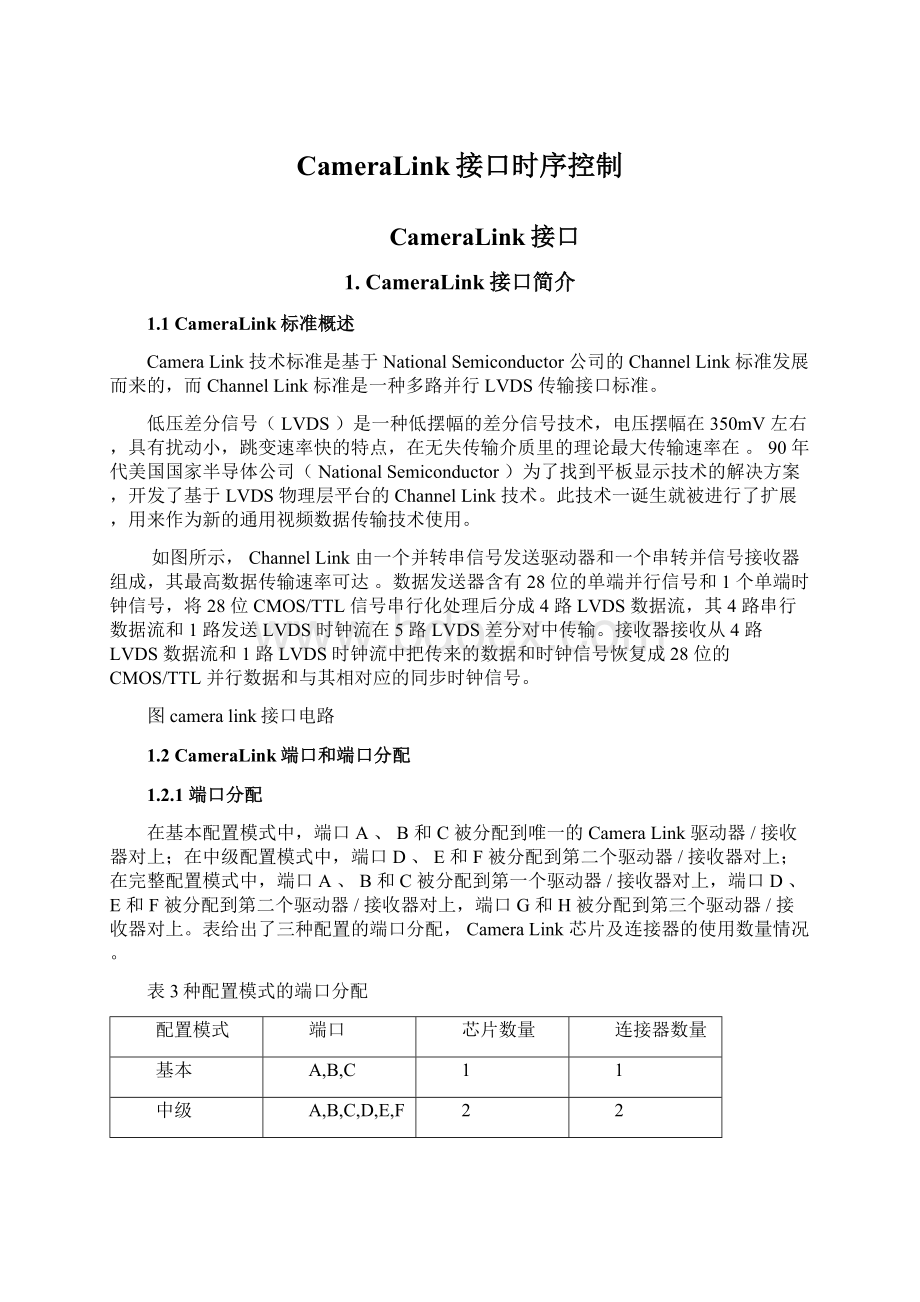

如图所示,ChannelLink由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达。

数据发送器含有28位的单端并行信号和1个单端时钟信号,将28位CMOS/TTL信号串行化处理后分成4路LVDS数据流,其4路串行数据流和1路发送LVDS时钟流在5路LVDS差分对中传输。

接收器接收从4路LVDS数据流和1路LVDS时钟流中把传来的数据和时钟信号恢复成28位的CMOS/TTL并行数据和与其相对应的同步时钟信号。

图cameralink接口电路

1.2CameraLink端口和端口分配

1.2.1端口分配

在基本配置模式中,端口A、B和C被分配到唯一的CameraLink驱动器/接收器对上;在中级配置模式中,端口D、E和F被分配到第二个驱动器/接收器对上;在完整配置模式中,端口A、B和C被分配到第一个驱动器/接收器对上,端口D、E和F被分配到第二个驱动器/接收器对上,端口G和H被分配到第三个驱动器/接收器对上。

表给出了三种配置的端口分配,CameraLink芯片及连接器的使用数量情况。

表3种配置模式的端口分配

配置模式

端口

芯片数量

连接器数量

基本

A,B,C

1

1

中级

A,B,C,D,E,F

2

2

完整

A,B,C,D,E,F,G,H

3

2

图各种配置下的端口连接关系

1.2.2端口的位分配

从表中我们可以看出在3种CameraLink配置模式中,图像数据位是怎样分配到端口的。

这种位分配方式已经被应用于市场上最流行的相机上了。

表CameraLink接口的端口分配

驱动器输入信号

对应芯片引脚

Strobe

TxCLKOut/TxCLKIn

LVAL

TX/RX24

FVAL

TX/RX25

DVAL

TX/RX26

Spare

TX/RX23

PortA0,PortD0,PortG0

TX/RX0

PortA1,PortD1,PortG1

TX/RX1

PortA2,PortD2,PortG2

TX/RX32

PortA3,PortD3,PortG3

TX/RX3

PortA4,PortD4,PortG4

TX/RX4

PortA5,PortD5,PortG5

TX/RX6

PortA6,PortD6,PortG6

TX/RX27

PortA7,PortD7,PortG7

TX/RX5

PortB0,PortE0,PortH0

TX/RX7

PortB1,PortE1,PortH1

TX/RX8

PortB2,PortE2,PortH2

TX/RX9

PortB3,PortE3,PortH3

TX/RX12

PortB4,PortE4,PortH4

TX/RX13

PortB5,PortE5,PortH5

TX/RX14

PortB6,PortE6,PortH6

TX/RX10

PortB7,PortE7,PortH7

TX/RX11

PortC0,PortF0

TX/RX15

PortC1,PortF1

TX/RX18

PortC2,PortF2

TX/RX19

PortC3,PortF3

TX/RX20

PortC4,PortF4

TX/RX21

PortC5,PortF5

TX/RX22

PortC6,PortF6

TX/RX16

PortC7,PortF7

TX/RX17

如果只用端口D和G,那么它们与器件的连接方法与端口A相同。

同样,如果使用端口E和H,它们与器件连接方法同端口B的相同,端口F的与端口C的相同。

如果相机在每个周期内仅输出1个像素,那么就使用分配给像素A的端口;如果相机在每个周期内输入2个像素,那么使用分配像素A和像素B的端口;如果在每个周期内输出3个像素,那么使用分配给像素A、B和C的端口;依次类推至相机每周期输出8个像素,那么分配给A~H的8个端口都将被使用。

2.CameraLink接口模块设计

2.1功能描述

该模块主要根据被测FPGA发来的图像地址信号将DDR2中的指定图像数据读取出来,并且分五路发送给CameraLink接口,由CameraLink图像采集卡接收并传给上位机显示。

2.2接口描述

CameraLink图像采集端口模块的接口信号如图所示:

图CameraLink图像采集端口示意图

表各端口的接口定义

端口名

端口类型

信号类型

描述

来源/去向

Cpsl_Reset_iN

输入

STD_LOGIC

异步复位时钟,低电平有效

时钟同步模块

Cpsl_CamLinkClk_i

输入

STD_LOGIC

主时钟85MHz

Cpsl_DdrClk_i

输入

STD_LOGIC

DDR2访问时钟

被测FPGA

Cpsv_DeBlkEn_i

输入

STD_LOGIC_VECTOR(6DOWNTO0)

地址使能信号,选择从A,D1,D2,D3,D4,D5,G中哪一块输出

Cpsl_CMOSFsyn_i

输入

STD_LOGIC

帧同步信号

Cpsl_CMOSLsyn_i

输入

STD_LOGIC

行同步信号

Cpsv_AXaddr_i

输入

STD_LOGIC_VECTOR(3DOWNTO0)

A块中的地址选择信号

Cpsv_D1Xaddr_i

输入

STD_LOGIC_VECTOR(10DOWNTO0)

D1块中的地址选择信号

Cpsv_D2Xaddr_i

输入

STD_LOGIC_VECTOR(10DOWNTO0)

D2块中的地址选择信号

Cpsv_D3Xaddr_i

输入

STD_LOGIC_VECTOR(10DOWNTO0)

D3块中的地址选择信号

Cpsv_D4Xaddr_i

输入

STD_LOGIC_VECTOR(10DOWNTO0)

D4块中的地址选择信号

Cpsv_D5Xaddr_i

输入

STD_LOGIC_VECTOR(10DOWNTO0)

D5块中的地址选择信号

Cpsv_IXaddr_i

输入

STD_LOGIC_VECTOR(3DOWNTO0)

I块中的地址选择信号

DS90CR287

DS90CR287

Cpsv_CamDataA_o

输出

STD_LOGIC_VECTOR(11DOWNTO0)

第一路Cameralink图像采集输出数据

Cpsl_CamFvalA_oP

输出

STD_LOGIC

第一路帧有效信号,高电平有效

Cpsl_CamDvalA_oP

输出

STD_LOGIC

第一路数据有效信号,高电平有效

Cpsl_CamLvalA_oP

输出

STD_LOGIC

第一路行有效信号,高电平有效

Cpsl_CamPwrDwnA_o

输出

STD_LOGIC

第一路CameraLinkPowerDown

Cpsl_CamClkA_o

输出

STD_LOGIC

第一路CameraLink时钟

Cpsv_CamDataB_o

输出

STD_LOGIC_VECTOR(11DOWNTO0)

第二路Cameralink图像采集输出数据

Cpsl_CamFvalB_oP

输出

STD_LOGIC

第二路帧有效信号,高电平有效

Cpsl_CamDvalB_oP

输出

STD_LOGIC

第二路数据有效信号,高电平有效

Cpsl_CamLvalB_oP

输出

STD_LOGIC

第二路行有效信号,高电平有效

Cpsl_CamPwrDwnB_o

输出

STD_LOGIC

第二路CameraLinkPowerDown

Cpsl_CamClkB_o

输出

STD_LOGIC

第二路CameraLink时钟

Cpsv_CamDataC_o

输出

STD_LOGIC_VECTOR(11DOWNTO0)

第三路Cameralink图像采集输出数据

Cpsl_CamFvalC_oP

输出

STD_LOGIC

第三路帧有效信号,高电平有效

Cpsl_CamDvalC_oP

输出

STD_LOGIC

第三路数据有效信号,高电平有效

Cpsl_CamLvalC_oP

输出

STD_LOGIC

第三路行有效信号,高电平有效

Cpsl_CamPwrDwnC_o

输出

STD_LOGIC

第三路CameraLinkPowerDown

Cpsl_CamClkC_o

输出

STD_LOGIC

第三路CameraLink时钟

Cpsv_CamDataD_o

输出

STD_LOGIC_VECTOR(11DOWNTO0)

第四路Cameralink图像采集输出数据

Cpsl_CamFvalD_oP

输出

STD_LOGIC

第四路帧有效信号,高电平有效

Cpsl_CamDvalD_oP

输出

STD_LOGIC

第四路数据有效信号,高电平有效

Cpsl_CamLvalD_oP

输出

STD_LOGIC

第四路行有效信号,高电平有效

Cpsl_CamPwrDwnD_o

输出

STD_LOGIC

第四路CameraLinkPowerDown

Cpsl_CamClkD_o

输出

STD_LOGIC

第四路CameraLink时钟

Cpsv_CamDataE_o

输出

STD_LOGIC_VECTOR(11DOWNTO0)

第五路Cameralink图像采集输出数据

Cpsl_CamFvalE_oP

输出

STD_LOGIC

第五路帧有效信号,高电平有效

Cpsl_CamDvalE_oP

输出

STD_LOGIC

第五路数据有效信号,高电平有效

Cpsl_CamLvalE_oP

输出

STD_LOGIC

第五路行有效信号,高电平有效

Cpsl_CamPwrDwnE_o

输出

STD_LOGIC

第五路CameraLinkPowerDown

Cpsl_CamClkE_o

输出

STD_LOGIC

第五路CameraLink时钟

app_af_wren

输出

STD_LOGIC

MIG缓存地址和命令的fifo写使能信号高电平有效

DDR2控制器

app_af_addr

输出

STD_LOGIC_VECTOR(30DOWNTO0)

MIG地址总线

app_af_cmd

输出

STD_LOGIC_VECTOR(2DOWNTO0)

MIG读写命令控制信号

clk0_tb

输入

STD_LOGIC

MIG用户界面同步时钟

app_af_afull

输入

STD_LOGIC

缓存地址和命令的fifo快满信号

rd_data_valid

输入

STD_LOGIC

读出数据有效信号,与有效数据同步

rd_data_fifo_out

输入

STD_LOGIC_VECTOR(63DOWNTO0)

MIG用户界面读数据总线

CameraLink接口信号时序如图所示:

图CameraLink图像采集电路的时序图

2.3功能实现

Cameralink图像采集接口电路主要包含两个子模块,如图所示,数据读取分发模块负责从DDR2中读取处理好的CMOS图像,并按指定的数据编排要求分发给5路CAMERALINK数据缓冲输出模块,数据缓冲输出模块完成5路CAMERALINK数据的缓冲,并按指定时序要求发送给DS90CR287。

图CameraLink图像采集软件流程框图

2.3.1数据读取分发模块

数据读取分发模块负责在帧行同步信号的控制下,按照地址使能和地址信号从DDR2中读取处理好的CMOS图像数据,并按指定的数据编排要求发送给cameralink数据缓冲输出模块。

该模块也分为两个子模块:

地址映射模块和读取DDR模块。

地址映射模块的主要功能是根据被测FPGA给的行地址转化成对应DDR的行起始地址,转化完成后把DDR地址发给DDR读取模块,DDR读取模块负责把该行的10240个像素(12bit)全部读取到五路缓冲模块中。

2.3.2数据缓冲输出模块

缓冲模块总共有五路,把一行图像数据平均分到五路缓冲后输出。

每路CameraLink缓冲模块包括2个双口RAM,采用乒乓读写的工作模式,一个双口RAM读DDR数据的同时另一个双口RAM发送数据。

双口RAM配置为两端口独立时钟模式,以隔离DDR时钟和CamerLink数据域的时钟。

另外,两端口可以配置为不同的数据位宽,以方便实现DDR2数据位宽64位到16位数据位宽的变换。

由于CamerLink输出时12位的,因此在款冲模块处还要有一个16位位宽转换位12位位宽的子模块来完成位宽的转换。

2.4modelsim仿真结果

图modelsim仿真结果

如图,被测FPGA每来一个行同步,CameraLink模块获取行地址后读取DDR2中的数据写入缓存模块,等到下一个行同步来的时候把所读的数据从缓存模块中输出。

实际要求的是每个行同步来后要读取一行数据,大小为2048x12bit,为了缩小仿真时间,仿真时没一行的数据长度为:

80x12bit。

图五路CameraLink仿真输出

如图,当下个行同步来的时候缓存数据输出,输出的数据时连续的。