版icfb的使用说明.docx

《版icfb的使用说明.docx》由会员分享,可在线阅读,更多相关《版icfb的使用说明.docx(29页珍藏版)》请在冰豆网上搜索。

版icfb的使用说明

icfb的使用说明

实验室上机

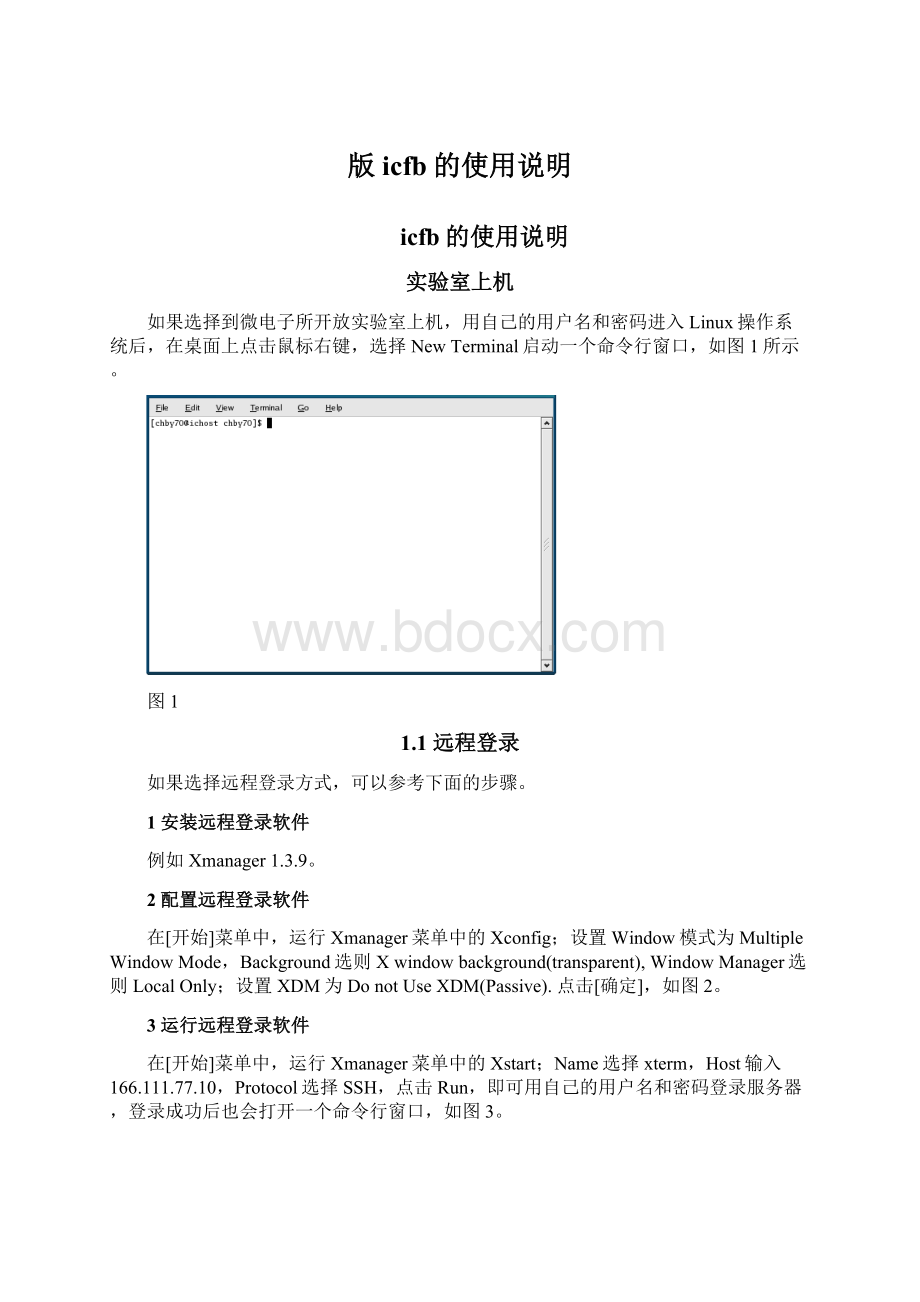

如果选择到微电子所开放实验室上机,用自己的用户名和密码进入Linux操作系统后,在桌面上点击鼠标右键,选择NewTerminal启动一个命令行窗口,如图1所示。

图1

1.1远程登录

如果选择远程登录方式,可以参考下面的步骤。

1安装远程登录软件

例如Xmanager1.3.9。

2配置远程登录软件

在[开始]菜单中,运行Xmanager菜单中的Xconfig;设置Window模式为MultipleWindowMode,Background选则Xwindowbackground(transparent),WindowManager选则LocalOnly;设置XDM为DonotUseXDM(Passive).点击[确定],如图2。

3运行远程登录软件

在[开始]菜单中,运行Xmanager菜单中的Xstart;Name选择xterm,Host输入166.111.77.10,Protocol选择SSH,点击Run,即可用自己的用户名和密码登录服务器,登录成功后也会打开一个命令行窗口,如图3。

图2

图3

1.2文件上传或下载

可以用自己的用户名和密码访问ftp:

//166.111.77.10,用于上传或下载自己的数据和文档。

注意,对于上传的网表(例如inv.sp)等文件,最好都运行一下dos2unix命令以确保文件转换为Unix格式,方法是在命令行窗口中输入命令dos2unixinv.sp,如图4。

图4

2创建工作环境

如果是第一次使用,需要按以下步骤创建工作环境。

如果是继续以前的工作,则直接按2.2节的步骤进入工作目录,启动设计软件即可。

2.1创建工作目录

创建工作目录:

在命令行窗口中输入命令mkdirproject。

创建验证目录:

在命令行窗口中输入命令mkdirproject/verify。

注意,所有设计工作、软件启动都在目录~/project下进行,所有版图验证工作都在目录~/project/verify下进行,不要在其它目录下进行。

设置SMIC工艺库环境:

输入命令cp~chby1/project/cds.lib~/project,如图5。

图5

2.2启动设计软件

进入工作目录:

输入命令cdproject。

启动设计软件icfb:

输入命令icfb&,弹出如图6所示的CIW窗口。

点击菜单FileExit可以退出icfb软件。

图6

2.3创建设计库

创建自己的设计库:

在CIW窗口中点击菜单FileNewLibrary;在弹出的对话框中,LibraryName输入库的名字(例如pa),TechnologyFile选择Attachtoanexistingtechfile,点击OK;在新弹出的对话框中,TechnologyLibrary选择工艺库smic18mm,点击OK,如图7。

图7

至此工作环境和设计库创建完毕,接下来可以在自己的库pa下面创建、编辑各个电路单元。

注意,一个设计项目里的所有电路单元(cell)都在同一个库(library)下面创建,建议不要再创建其它的设计库。

2.4查看设计软件帮助

查看Cadence的帮助文档可以输入命令cdsdoc&,弹出如图8所示的窗口。

图8

3设计流程实例

本节结合一个反相器的实例来简单说明整个设计流程。

如果电路设计与仿真采用Hspice软件,则可以跳过3.1和3.2节,但要注意在3.5节LVS设置中的差异。

3.1电路设计

1创建或打开电路原理图

新建电路原理图(schematic)单元:

在CIW窗口中点击菜单FileNewCellview;在弹出的对话框中,LibraryName选择自己的设计库pa,CellName输入电路单元的名字(例如inv),Tool选择Composer-Schematic,点击OK,如图9。

弹出如图11所示的编辑窗口。

如果之前已经创建过,则直接打开电路原理图单元:

点击菜单FileOpen;在弹出的对话框中,LibraryName选择pa,CellNames选中inv,ViewName选择schematic,点击OK,如图10。

点击菜单WindowClose可以退出编辑窗口,如图11。

图9

图10

2编辑电路原理图

调入单元:

点击菜单AddInstance;在弹出的对话框中点击Browse,在新弹出的小对话框中选择要添加的单元,点击Close;然后输入合适的器件参数,点击Hide,如图12。

器件在工艺库smic18mm中;global电源/地、激励源、一些理想元件等在库analogLib中。

添加互连线:

点击菜单AddWire(narrow)。

添加端口:

点击菜单AddPin;在弹出的对话框中,PinName输入端口结点名(例如A),Direction选择合适的类型,点击Hide,如图12。

在编辑过程中注意随时保存:

点击菜单DesignCheckandSave。

图11

图12

编辑完成后的电路原理图如图13所示。

3创建或打开电路符号图

创建电路符号图(symbol)单元:

在编辑窗口中点击菜单DesignCreateCellviewFromCellview;在弹出的对话框中点击OK;在新弹出的对话框中选择各个端口的摆放位置(例如A在左、Y在右),点击OK,如图14。

图13

图14

如果之前已经创建过,则可直接打开电路符号图单元:

点击菜单DesignOpen,在弹出的对话框中,LibraryName选择pa,CellNames选中inv,ViewName选择Symbol,点击OK,如图15。

4编辑电路符号图

在弹出的编辑窗口中自动生成一个简单电路符号图,可以编辑修改它,如图16。

在编辑过程中注意随时保存,点击菜单DesignCheckandSave。

注意,创建电路符号图之后,在编辑其它电路原理图单元时就可以调用该电路单元,如图18。

图15

图16

3.2电路仿真

1创建或打开仿真原理图

新建或打开一个用作仿真平台(testbench)的电路原理图(schematic)单元,另取一个单元名字(例如inv_tb),方法同3.1节,如图17。

图17

2编辑仿真原理图

调入要仿真的电路单元inv,添加激励及负载等外围元件,方法同3.1节,如图18,注意保存。

编辑完成后如图20所示。

图18

3启动仿真软件

在图20所示的编辑窗口中点击菜单ToolsAnalogEnvironment,启动电路仿真软件Spectre。

软件会自动创建一个目录simulation作为仿真目录。

注意,所有电路仿真工作都在自动创建的目录~/simulation下进行,不要在其它目录下进行。

点击菜单SessionQuit可以退出Spectre软件,如图19。

图19

图20

4设置仿真条件

如果之前已经设置并保存过仿真条件,可以直接调出:

点击菜单SessionLoadState,选择合适的存档(例如state1),点击OK,如图21所示。

然后可以在此基础上修改仿真条件。

图21

如果是第一次仿真,或者要修改仿真条件,则按以下步骤进行。

设置工艺库及工艺角:

点击菜单SetupModelLibraries;在弹出的对话框中点击Browse,在新弹出的对话框中选中工艺库文件ms018_v14p_spe.lib,点击OK;Section输入工艺角(例如tt),点击Add/Delete可以添加/移除工艺库,点击Enable/Disable可以启用/禁用已添加的各个工艺库(例如把ms018_rf_v1p1_spe.lib禁用掉),点击Change,最后点击OK,如图22。

设置激励源:

点击菜单SetupStimuli;在弹出的对话框中,对Inputs及GlobalSources中的每个激励源进行设置,每设置完一个激励源后选中Enabled并点击Change,最后点击OK,如图22。

设置仿真类型:

点击菜单AnalysesChoose;在弹出的对话框中,Analysis选择tran,StopTime输入5n,选中Enabled,点击OK,如图22。

设置输出变量:

点击菜单OutputsToBePlottedSelectOnSchematic;在弹出的编辑窗口中,点击要输出的结点或元件(例如结点in和out),如图23。

图22

图23

可以保存仿真条件设置:

点击菜单SessionSaveState;在弹出的对话框中,SaveAs输入名字(例如state1),点击OK,如图21所示,以便以后可以直接调出该设置。

5查看仿真结果

点击菜单SimulationNetlistandRun运行仿真,弹出仿真进度显示窗口,仿真结束后弹出如图24所示的结果查看窗口,可以查看仿真结果。

点击菜单FileExit可以关闭结果查看窗口。

图24

3.3版图设计

1创建或打开版图

新建版图(layout)单元:

在CIW窗口中点击菜单FileNewCellview;在弹出的对话框中,LibraryName选择设计库pa,CellName输入版图单元的名字inv,Tool选择Virtuoso,点击OK,如图25。

弹出如图26所示的编辑窗口和一个图层窗口。

如果之前已经创建过,则直接打开版图单元:

点击菜单FileOpen;在弹出的对话框中,LibraryName选择pa,CellNames选中inv,ViewName选择layout,点击OK,如图25。

点击菜单WindowClose可以退出编辑窗口。

注意,图层窗口无法单独关闭,不必管它,在退出CIW窗口时它会自动关闭。

图25

2编辑版图

设置显示:

在编辑窗口中点击菜单OptionsDisplay;在弹出的对话框中,选中File输入文件名,点击SaveTo/LoadFrom可以保存/调出显示设置;建议在XSnapSpacing和YSnapSpacing输入0.01,DisplayLevels在Stop输入5,最后点击OK,如图27。

在图层窗口中,点击AV/NV可以显示/隐藏所有图层,点击AS/NS可以允许/禁止select所有图层,鼠标左键用于选中某一图层,鼠标中键用于显示/隐藏某一图层,鼠标右键用于允许/禁止select某一图层,如图26。

图26

图27

调入单元:

点击菜单CreateInstance,在弹出的对话框中点击Browse,在新弹出的小对话框中选择要添加的单元,点击Close;然后输入合适的器件参数,点击Hide,方法与3.1节相同。

所有Pcell单元都在工艺库smic18mm中。

添加图形:

选中相应的图层,点击菜单CreateRectangle或Path等。

添加端口:

选中相应的金属层,点击菜单CreateLabel;在弹出的对话框中,PinName输入端口结点名(例如gndd!

),Height输入合适的尺寸,点击Hide,如图27。

在编辑过程中注意随时保存:

点击菜单DesignSave。

编辑完成后的版图如图28所示。

注意,创建一个版图之后,在编辑其它版图单元时就可以调用该版图单元。

图28

3.4版图DRC验证

1启动DRC软件

在编辑窗口中点击菜单CalibreRunDRC,启动版图验证软件Calibre做DRC,如图28。

假如菜单中没有Calibre,也可以在命令行窗口中输入命令calibre-gui&,启动Calibre软件,如图29,然后点击DRC。

图29

弹出如图30所示的DRC窗口和一个调入规则设置存档的对话框。

在DRC窗口中点击FileExit可以退出Calibre软件。

2设置DRC规则

如果之前已经设置并保存过DRC规则,可以直接调出:

在图30的对话框中直接点击OK即可。

然后可以在此基础上修改DRC规则设置。

图30

如果是第一次做DRC,或者要修改DRC规则,则按以下步骤进行。

设置DRC规则:

在DRC窗口中点击Rules;在Calibre-DRCRunDirectory输入验证目录verify,在Calibre-DRCRulesFile点击[…],在弹出的对话框中找到目录~chby1//rules/drc/calibre,选中规则文件SmicDRL2TM5P_cal018_mixlog_p1mt6_Sali.drc,点击Open,如图31。

图31

点击Inputs;在TopCell输入要做DRC的版图单元名字inv,选中Exportfromlayoutviewer,Files输入要导出的gds文件名,如图32。

图32

可以保存DRC规则设置:

点击菜单FileSaveRunset,在弹出的对话框中输入存档路径和文件名(例如drc_runset),点击OK,如图33。

以便以后可以直接调出该设置,如图30。

图33

3查看DRC结果

点击RunDRC运行DRC,弹出验证进度显示窗口,验证结束后弹出如图34所示的RVE窗口。

在弹出的RVE窗口中,点击菜单ViewShowEmptyChecks,使这一项不要被选中,然后可以点击鼠标左键查看错误说明,或点击鼠标右键选择HighlightResult,在编辑窗口中会高亮显示错误区域,点击菜单HighlightClearHighlights可以清除高亮显示,如图34。

点击菜单FileExit可以关闭RVE窗口。

图34

3.5版图LVS验证

1启动LVS软件

版图DRC通过之后,在图28的编辑窗口中点击菜单CalibreRunLVS,启动版图验证软件Calibre做LVS。

或者在如图29中点击LVS。

弹出如图35所示的LVS窗口和一个调入规则设置存档的对话框。

在LVS窗口中点击FileExit可以退出Calibre软件。

2设置LVS规则

如果之前已经设置并保存过LVS规则,可以直接调出:

在图35的对话框中直接点击OK即可。

然后可以在此基础上修改LVS规则设置。

如果是第一次做LVS,或者要修改LVS规则,则按以下步骤进行。

设置LVS规则:

在LVS窗口中点击Rules;在Calibre-LVSRunDirectory输入验证目录verify,在Calibre-LVSRulesFile点击[…],在弹出的对话框中找到目录~chby1/rules/lvs/calibre/SmicSP6_cal018_log_p1mtx_sali,选中规则文件SmicSP6.1P_cal018_log_p1mtx_sali.lvs,点击Open,如图36。

图35

图36

点击Inputs;Layout设置参见图32;Netlist设置如图37,在TopCell输入要做LVS的电路单元名字inv,选中Exportfromlayoutviewer,Files输入要导出的spice网表文件名。

注意,如果电路设计采用Hspice软件,则在TopCell输入要做LVS的子电路(subckt)名字inv,不要选中Exportfromschematicviewer,Files输入自己编写的spice网表路径及文件名(例如inv.sp)。

可以保存LVS规则设置:

点击菜单FileSaveRunset,在弹出的对话框中输入存档路径和文件名(例如lvs_runset),点击OK,如图38。

以便以后可以直接调出该设置,如图35。

图37

图38

3查看LVS结果

点击RunLVS运行LVS,弹出验证进度显示窗口,验证结束后弹出如图39所示的RVE窗口。

在弹出的RVE窗口中,可以点击鼠标左键查看错误说明,或点击鼠标右键选择HighlightResult,在编辑窗口中会高亮显示错误区域,如果没有错误则显示绿色图标,点击SourceNetlist可以弹出窗口查看电路的spice网表,如果在网表中点击结点或元件,编辑窗口中会出现相应的高亮显示,如图40,在编辑窗口中点击菜单CalibreClearHighlights可以清除所有高亮显示。

点击菜单FileExit可以关闭RVE窗口。

图39

图40

3.6版图后仿真

1启动PEX软件

版图LVS通过之后,在图28的编辑窗口中点击菜单CalibreRunPEX,启动版图验证软件Calibre做PEX提取版图的网表。

或者在如图29中点击PEX。

弹出如图41所示的PEX窗口和一个调入规则设置存档的对话框。

在PEX窗口中点击FileExit可以退出Calibre软件。

图41

2设置PEX规则

如果之前已经设置并保存过PEX规则,可以直接调出:

在图41的对话框中直接点击OK即可。

然后可以在此基础上修改PEX规则设置。

如果是第一次做PEX,或者要修改PEX规则,则按以下步骤进行。

设置PEX规则:

在PEX窗口中点击Rules;在Calibre-PEXRunDirectory输入验证目录verify,在Calibre-PEXRulesFile点击[…],在弹出的对话框中找到目录~chby1/rules/pex/calibre/,选中规则文件SmicSP5T_RF3T_cal018_mix_p1mt6_sali.lvs_XRC,点击Open,如图42。

图42

点击Inputs;Netlist设置如图43,在TopCell输入要做LVS的电路单元名字inv,选中Exportfromschematicviewer,Files输入要导出的spice网表文件名。

注意,如果电路设计采用Hspice软件,则在TopCell输入要做PEX的子电路(subckt)名字inv,不要选中Exportfromschematicviewer,Files输入自己编写的spice网表路径及文件名(例如inv.sp)。

点击Outputs;Netlist设置如图44,Format选择HSPICE,File输入导出的HSPICE网表的名称。

可以保存PEX规则设置:

点击菜单FileàSaveRunset,在弹出的对话框中输入存档路径和文件名(例如lvs_runset),点击OK,如图45。

以便以后可以直接调出该设置。

图43

图44

图45

3查看PEX结果,进行后仿真

点击RunPEX运行PEX,结束后弹出如图46所示的窗口,可以看到从版图生成的网表。

点击菜单FileExit可以关闭窗口。

图46

进入PEX运行目录下,将上述过程得到的基于版图的网表导出,共有三个文件,分别为:

*list,*list.pex,*list.*.pxi,其中*list为顶层文件。

在上述设计中“*”为“inv”,list为inv的子电路,如图46所示。

使用~chby1目录下的hspice文件夹中的SPICE模型对上述网表进行仿真,即可完成后仿真。