脉冲宽度测量仪xxx.docx

《脉冲宽度测量仪xxx.docx》由会员分享,可在线阅读,更多相关《脉冲宽度测量仪xxx.docx(8页珍藏版)》请在冰豆网上搜索。

脉冲宽度测量仪xxx

EDA技术课程设计

题目:

脉冲宽度测量仪

专业班级:

电子信息工程

姓名:

xxxxxxxxx

学号:

0xxxxxxxxxxxx8

指导老师:

xxxxx

2012年5月20日

EDA程序课程设计任务书

一、主要任务:

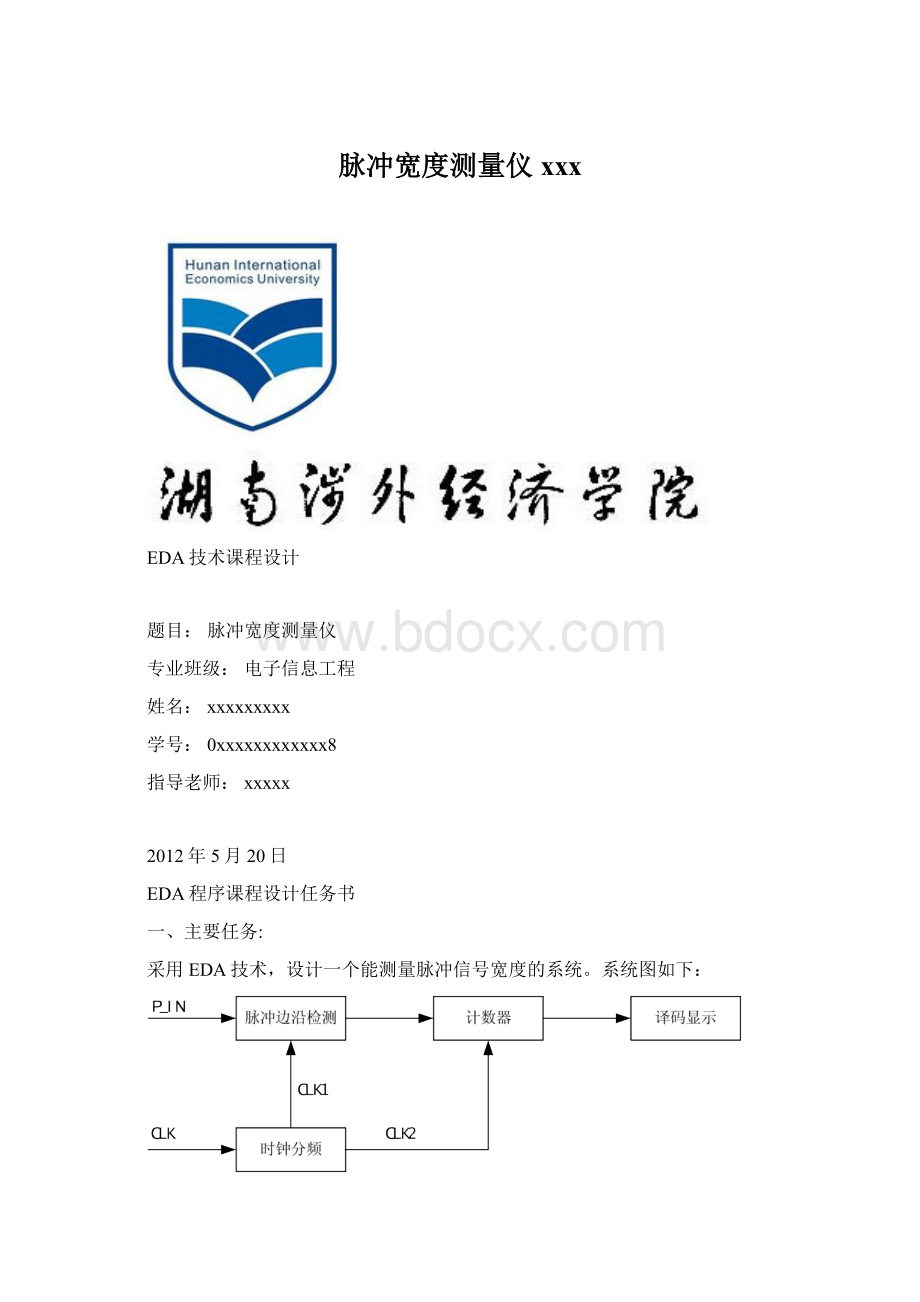

采用EDA技术,设计一个能测量脉冲信号宽度的系统。

系统图如下:

二、基本要求:

(1)脉冲信号宽度的测量精度为±1ms。

(2)脉冲信号宽度的测量范围为0~10s。

(3)调试过程中可以用按键模拟脉冲信号。

(4)测量值用5位数码管显示(可以采用静态显示)。

(5)输入信号为标准TTL电平。

(6)调试中既可以采用正脉冲,也可以采用负脉冲(任选其一)。

(7)必须先进行前仿真,并打印出仿真波形。

(8)按要求写好设计报告(设计报告内容包括:

引言,方案设计与论证,总体设计,各模块设计,调试与数据分析,总结)。

目录

引言……………………………………………………………4

第一章总体设计思想4

1.基本原理4

2.设计框图4

第二章设计步骤和调试过程5

1、总体设计电路5

(1)脉冲检测模块5

(2)计数模块5

(3)译码显示模块5

第三章模块设计和相应模块程序5

1、检测程序模块5

2、计数程序模块6

第四章设计电路图9

第五章实验调试结果10

第六章结论及心得体会11

参考资料11

引言:

随着我国脉冲测量仪器市场的迅猛发展,特别是十二五时期,转变经济增长方式这一主基调的确定,与之相关的核心生产技术应用与研发必将成为业内企业关注的焦点。

技术工艺的优劣直接决定企业的市场竞争力。

了解国内外脉冲测量仪器生产核心技术的研发动向、工艺设备、技术应用对于企业提升产品技术规格,提高市场竞争力十分关键。

本报告通过详细的介绍脉冲宽度测量仪的设计方法,为客户提供脉冲测量仪器行业主要技术应用现状、技术研发、工艺设备配套、高端技术应用等多方面的信息,对于企业了解各类脉冲测量仪器产品生产技术及其发展状况十分有益

第一章总体设计思想

1.基本原理

根据设计要求,系统的输入信号有:

系统时钟信号CLK,系统复位信号CLR,脉冲输入信号P_IN。

当计数输出端检测到P_IN端有脉冲输入时检测模块就会输出1,否则为0,输给计数模块的EN端,当各位累计到9时,会向十位进位

以此类推到万位.最后由数码管显示脉冲的宽度(数码管的读数).

2.设计框图

系统组成方框图如下所示,它由外部输入模块、检测模块和显示模块三部分组成。

检测模块是整个系统的核心,它由计数模块、控制模块、计量模块和

显示模块构成。

图1.1系统框图

第二章设计步骤和调试过程

1、总体设计电路

(1)脉冲检测模块

当有检测到P_IN端有脉冲输入(P_IN=1)时,EN_OUT=1输送到计数器的EN端。

(2)计数模块

计数模块是对检测到的脉冲进行计数,计算出脉冲的宽度。

(3)译码显示模块

对输入的脉冲宽度进行显示出来。

第三章模块设计和相应模块程序

1、检测程序模块

--basofmeasure;

libraryieee;

useieee.std_logic_1164.all;

entitymeasureis

port(

P_IN:

instd_logic;

EN_OUT:

outstd_logic);

endmeasure;

architecturebehaveofmeasureis

begin

process(P_IN)

begin

if(P_IN='1')thenEN_OUT<='1';--实现检测,若有脉冲就输出为1

elseEN_OUT<='0';--,否则为0

endif;

endprocess;

endbehave;

2、计数程序模块

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitycountis

port(

EN:

instd_logic;

CLK:

instd_logic;

CLR:

instd_logic;

CQ:

outstd_logic;

Qout:

buffer:

std_logic_vector(3downto0)

);

endcount;

architectureartofcountis

begin

process(CLK,CLR,EN,QOUT)

Begin

ifCLR='1'thenQout<="0000";

elsifCLK'eventandCLK='1'then

ifEN='1'then

Qout="1001"thenQout<="0000";

elseQout<=Qout+'1';

endif;

endif;

endif;

ifQout="1001"then

CQ<='1';

else

CQ<='0';

endif;

endprocessU1;

endart;

第四章设计电路图

图4.1原理图构建

第五章实验调试结果

为验证所设计程序是否正确,将程序下载进行硬件测试。

在QuartusⅡ开发环境中进行管脚锁定,连接好数码管驱动电路,然后将目标文件下载到器件

多次数据测试,显示正常,基本实现本实验的要求,下面是波形仿真图:

图5.1波形仿真图

第六章结论及心得体会

这次设计真的让我学到了很多,增加了我们对EDA的认识,增深了我们对EDA的理解深度和运用的能力,学在其中,乐在其中。

在这其中我也碰到很多困难,最大的是在调试,在调试了很久,在朋友的帮助下,原来是括号的问题,调试时,怎么样把两个模块连接在一起,原理图怎么连接,朋友也告诉我格式的重要性,没有好的写格式的习惯,在括号上是很难找出错误的,真的发现自己学的还不够。

在解决问题的技巧上,我觉得最大的就是遇到问题一定要问,而且一定要懂,看懂直到自己能写为止;还有就是“细心”,特别在写比如architectureartofcountis后面不加分号等,还是一句最重要的还是得多写,养成好的习惯,慢慢就开始学会了。

通过这次课程设计,让自己从完全不知到开始会写,每写一句都会有成就感,特别是在调试成功之后,那种感觉真的很好,还要感谢帮助我的老师和同学,没有他们,我的程序和调试也不可能这么快完成,谢谢你们。

参考资料:

[1]潘松著.EDA技术实用教程(第二版).北京:

科学出版社,2005.

[2]康华光主编.电子技术基础模拟部分.北京:

高教出版社,2006.

[3]阎石主编.数字电子技术基础.北京:

高教出版社,2002