EDA实验一38译码器的设计.docx

《EDA实验一38译码器的设计.docx》由会员分享,可在线阅读,更多相关《EDA实验一38译码器的设计.docx(14页珍藏版)》请在冰豆网上搜索。

EDA实验一38译码器的设计

《电子设计自动化》实验报告

实验一实验名称:

3-8译码器的设计

专业及班级:

姓名:

学号:

一、实验目的:

1.掌握组合逻辑电路的设计方法。

2.掌握VHDL语言的基本结构及设计的输入方法。

3.掌握VHDL语言的基本描述语句的使用方法。

二、实验步骤(附源代码及仿真结果图):

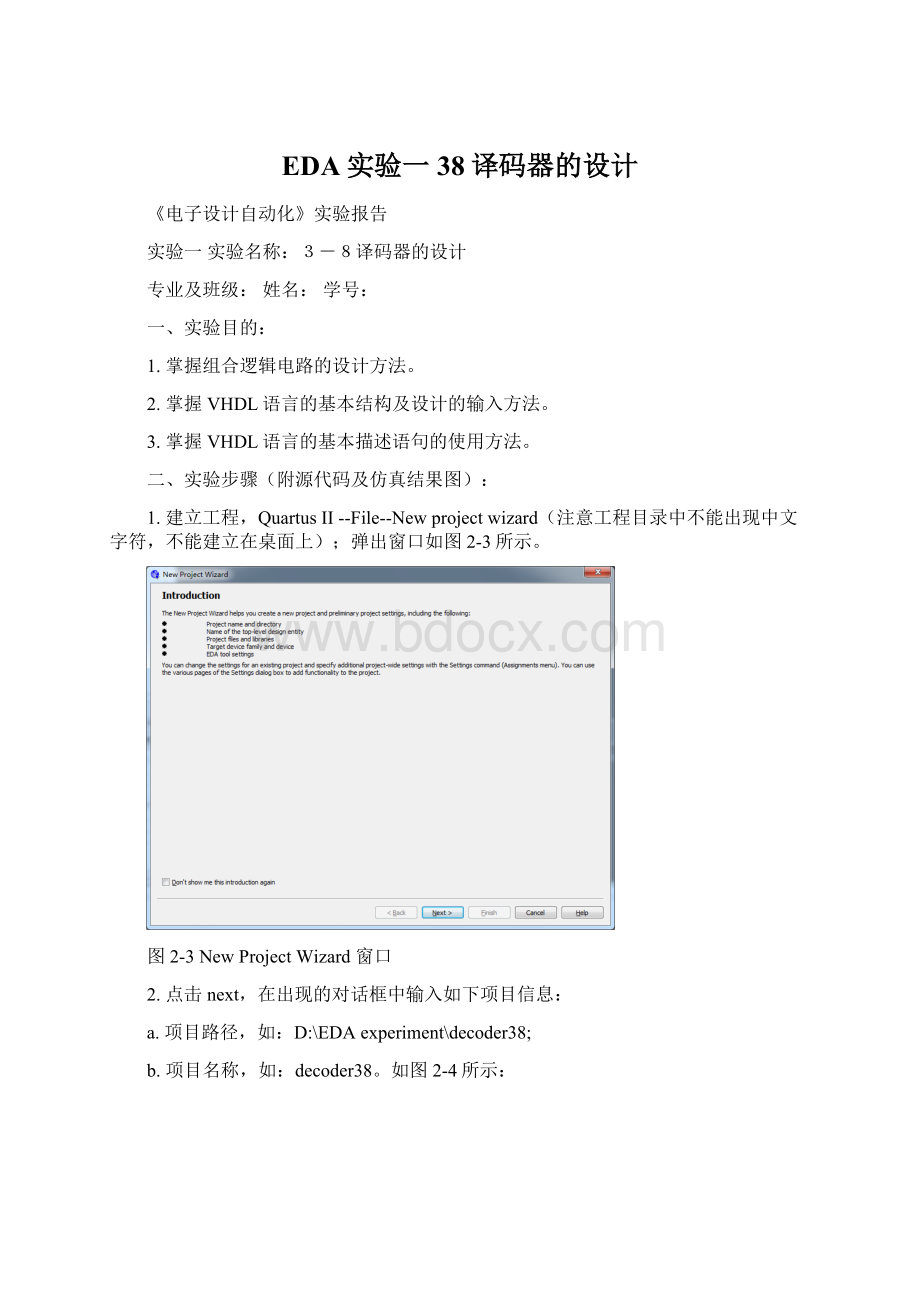

1.建立工程,QuartusII--File--Newprojectwizard(注意工程目录中不能出现中文字符,不能建立在桌面上);弹出窗口如图2-3所示。

图2-3NewProjectWizard窗口

2.点击next,在出现的对话框中输入如下项目信息:

a.项目路径,如:

D:

\EDAexperiment\decoder38;

b.项目名称,如:

decoder38。

如图2-4所示:

图2-4项目路径和项目名称对话框

3.点击2次next后,出现如图2-5所示的对话框:

a.Devicefamily中选择CycloneIVE;

b.Availabledevices中选择EP4CE115F29C7.

图2-5器件选择窗口

4.点击next后,出现EDA工具设置对话框。

在Simulation一行中,ToolName选择ModelSim-Altera,Fomat(s)选择VHDL,如图2-6所示。

图2-6EDA工具设置对话框

5.点击next,出现如图2-7所示的对话框:

图2-7新建项目汇总对话框

6.点击Finish后,出现如图2-8所示的界面:

图2-8decoder38项目界面

7.点击File->New->VHDLFile,如图2-9所示。

点击ok关闭对话框。

图2-9新建VHDL文件窗口

8.在文本编辑框内键入如下程序:

LIBRARYieee;

USEieee.std_logic_1164.ALL;

ENTITYdecoder38IS

PORT(

A,B,C,G1,G2A,G2B:

INSTD_LOGIC;

Y:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDdecoder38;

ARCHITECTUREBehaviorOFdecoder38IS

SIGNALindata:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

indata<=C&B&A;

PROCESS(indata,G1,G2A,G2B)

BEGIN

IF(G1='1'ANDG2A='0'ANDG2B='0')THEN

CASEindataIS

WHEN"000"=>Y<="11111110";

WHEN"001"=>Y<="11111101";

WHEN"010"=>Y<="11111011";

WHEN"011"=>Y<="11110111";

WHEN"100"=>Y<="11101111";

WHEN"101"=>Y<="11011111";

WHEN"110"=>Y<="10111111";

WHEN"111"=>Y<="01111111";

WHENOTHERS=>Y<="XXXXXXXX";

ENDCASE;

ELSE

Y<="11111111";

ENDIF;

ENDPROCESS;

ENDBehavior;

9.将文件保存为decoder38.vhd后,开始编译,点击Processing->StartCompilation,编译成功后,出现如图2-10所示界面:

图2-10编译成功界面

10.再次新建一个vhdl文件,键入如下的modelsim测试程序:

LIBRARYieee;

USEieee.std_logic_1164.ALL;

ENTITYdecoder38_tbIS

ENDdecoder38_tb;

ARCHITECTUREBehaviorOFdecoder38_tbIS

COMPONENTdecoder38

PORT(

A,B,C,G1,G2A,G2B:

INSTD_LOGIC;

Y:

OUTSTD_LOGIC_VECTOR(7DOWNTO0));

ENDCOMPONENT;

SIGNALA:

STD_LOGIC:

='0';

SIGNALB:

STD_LOGIC:

='0';

SIGNALC:

STD_LOGIC:

='0';

SIGNALG1:

STD_LOGIC:

='1';

SIGNALG2A:

STD_LOGIC:

='0';

SIGNALG2B:

STD_LOGIC:

='0';

SIGNALY:

STD_LOGIC_VECTOR(7DOWNTO0);

CONSTANTCLK_PERIOD:

TIME:

=10ns;

BEGIN

A<=notAafterCLK_PERIOD;

B<=notBafter20ns;

C<=notCafter40ns;

U1:

decoder38portmap(A=>A,B=>B,C=>C,G1=>G1,G2A=>G2A,G2B=>G2B,Y=>Y);

ENDbehavior;

11.将文件保存为decoder38_tb.vhd,编译通过。

12.点击Tools->Options->General->EDAToolOptions,在ModelSim-Altera下,选择你安装ModelSim-Altera的文件夹下的win32aloem文件夹,如图2-11所示。

点ok退出对话框。

图2-11选项对话框

13.点击Tools->RunSimulationTools->RTLSimulation,调出ModelSim-Altera软件,如图2-12所示。

图2-12ModelSim-Altera界面

14.在ModelSim-Altera界面下,选择File->New->Project,出现如图2-13所示的对话框:

图2-13新建项目对话框

输入项目名称,如decoder,点击ok出现如图2-14所示的界面。

图2-14添加到项目界面

15.选择AddExistingFile,将源代码decoder38.vhd和测试文件decoder38_tb.vhd一同加入项目。

添加文件类型选择VHDL,添加界面如图2-15所示:

图2-15添加文件界面

16.点击Compile->CompileAll。

17.在Library标签栏下,展开work下的decoder38_tb,如图2-16所示。

双击behavior,将自动进入仿真界面,如图2-17所示。

图2-16library界面

图2-17ModelSim-Altera仿真界面

18.点击Simulate->RuntimeOptions,弹出对话框如图2-18所示。

在DefaultRun文本框中,输入100ms。

图2-18RuntimeOptions对话框

19.在屏幕中间object标签栏中选择所有要观察的信号,右键,Add->ToWave->SelectedSignals,点击工具栏中的Run图标,可以观测到仿真结果,如图2-19所示。

可以通过工具栏中的ZoomIn,ZoomOut对仿真窗口进行调节。

图2-19三八译码器仿真结果

20.分配管脚:

在QuartusII界面下,点击Processing->Start->StartAnalysis&Elaboration,在弹出的对话框中点击ok。

21.点击Assignments->PinPlanner,打开PinPlanner对话框,如图2-20所示。

图2-20PinPlanner对话框

22.分别用SW0、SW1、SW2三个拨码开关对应A、B、C三个输入信号,SW3、SW4、SW5对应G1、G2A、G2B三个输入信号,LEDR0~LEDR7分别对应Y0~Y78个输出信号,查表1和表3,分配好引脚号,如图2-21所示。

图2-21引脚分配界面

23.将提供的USB电缆线一端接到DE2-115开发板的USBBlaster端口,一端连接计算机的USB接口,连接12V电源,然后开启DE2-115电源开关。

24.点击Tools->Programmer,打开Programmer界面,如图2-22所示。

图2-22Programmer界面

25.点击HardwareSetup,弹出如图2-23所示对话框。

在Currentlyselectedhardware下拉菜单中选择USB-Blaster[USB-0]。

点击Close关闭对话框

图2-23HardwareSetup对话框

26.如果Programmer对话框中没有decoder38.sof,点击AddFile按钮,在项目路径下选择decoder38.sof。

27.点击start,将sof文件载入到FPGA芯片中。

从而完成整个设计过程。

如图2-24所示。

图2-24将程序载入FPGA成功界面

28.在DE2-115开发板上通过拨码开关和LED灯验证整个设计的有效性。

要注意的是,闲置的管脚一定要置输入三态(Asinputtri-stated)。

因为必须确保该开发板当前没用到的Flash芯片与FPGA之间以高阻态相隔,否则会发生损坏芯片的危险!

如果一开始开发板上所有LED灯都是亮的话,可按以下步骤进行处理:

a.点击Assignments->Device,在弹出的对话框中点击DeviceandPinOptions;

b.选择UnusedPins,在Reserveallunusedpins下拉菜单中选择Asinputtri-stated。

点击ok两次关闭对话框。

c.重新编译,下载。

三、实验中发现的问题:

1、程序代码输入后,但是编译有错误,经检查后发现在该语句Y:

OUTSTD_LOGIC_VECTOR(7DOWNTO0))中最后有两个括号,但是因为马虎,少输入一个括号导致编译错误;

2、修改上面的错误后编译,仍然出现错误,多次检查后未发现错误,询问老师后得知需要改一个文本文件中的代码,修改完毕编译,错误得以解决,程序正常运行;

3、没有采用实验报告册的测试程序,而是经老师帮助直接运用了工具栏中的仿真软件进行仿真的,但是仿真过程不大熟悉,先是没有找到run键,然后对于输入信号的赋值操作容易出错,所以还需要多次做实验室操作该软件才行;

4、上机之前由于对实验没有仔细研究,因此编入程序时没有多大感悟,所以以后应该提前预习。