第2章单片机硬件结构2.docx

《第2章单片机硬件结构2.docx》由会员分享,可在线阅读,更多相关《第2章单片机硬件结构2.docx(22页珍藏版)》请在冰豆网上搜索。

第2章单片机硬件结构2

第四节并行输入/输出端口

一、概述

89C51单片机有四个8位并行I/O端口,记作P0、P1、P2和P3。

P0口为三态双向口,可驱动8个TTL电路,P1、P2、P3口为准双向口(作为输入时,口线被拉成高电平,故称为准双向口),其负载能力为4个TTL电路。

每一条I/O线都能独立地用作输入或输出。

每个端口都包括一个锁存器(即特殊功能寄存器P0—P3),一个输出驱动器和输入缓冲器,作为输出时数据可以锁存,作输入时数据可以缓冲,但这四个通道的功能不完全相同。

因为P1、P2、P3有固定的内部上拉电阻,所以有时称它们为准双向口。

当用做输入时被拉高,低则要靠外部电路拉低。

而P0则是真双向口,因为作为输入时它是悬浮的。

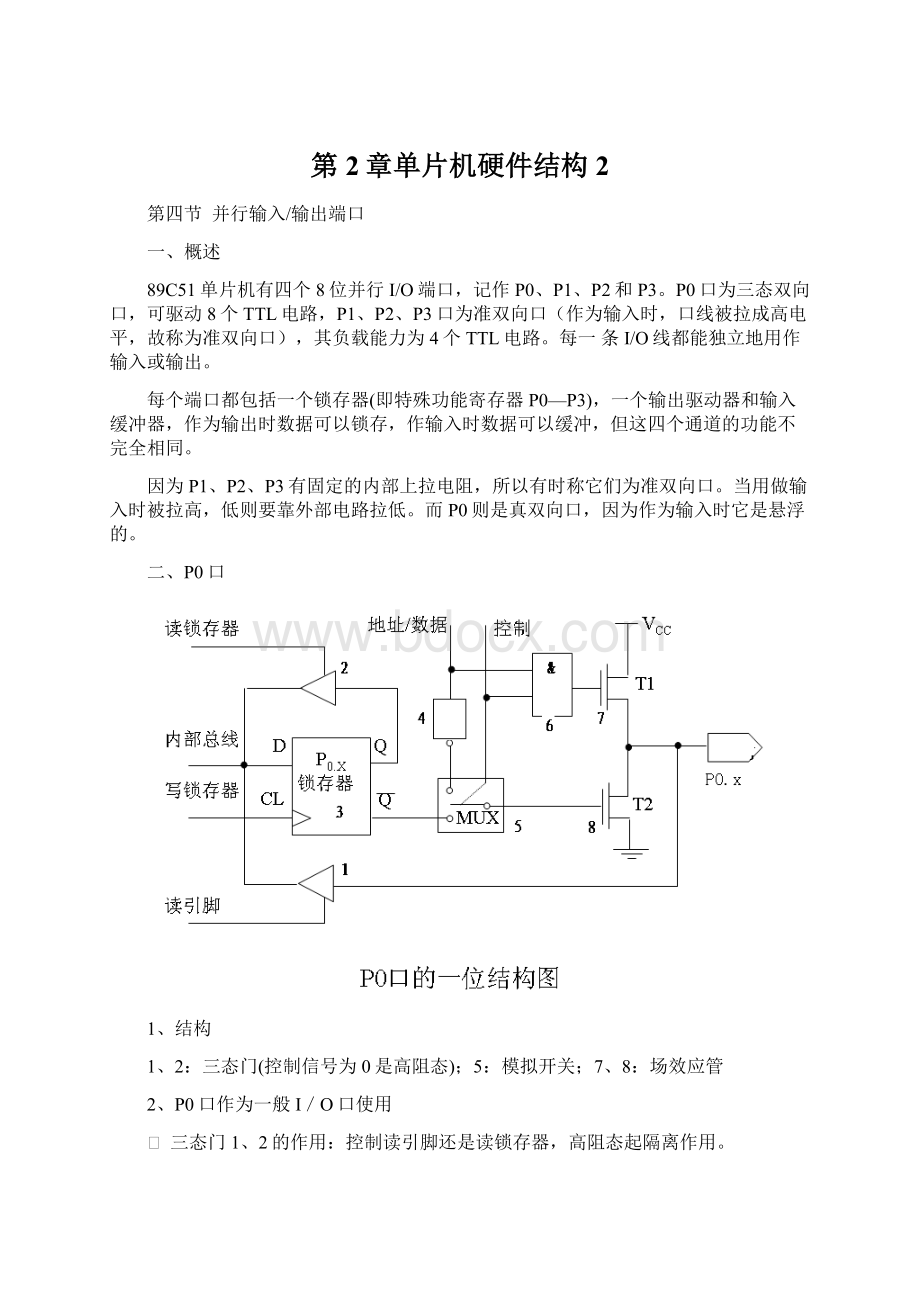

二、P0口

1、结构

1、2:

三态门(控制信号为0是高阻态);5:

模拟开关;7、8:

场效应管

2、P0口作为一般I/O口使用

Ø三态门1、2的作用:

控制读引脚还是读锁存器,高阻态起隔离作用。

ØMUX由指令控制。

Ø当8051组成的系统,CPU对片内存储器和I/O口读写时,开关MUX处于下面位置,它把T2输入与锁存器的

端接通;

Ø当指令是读、写片外程序或数据,MUX控制置高电平,开关与上面接通。

ØCL=0时锁存,锁存总线信号。

Ø读引脚为1,读引脚,读锁存器为高阻态;读锁存器为1,读锁存器,读引脚为高阻态。

1)P0口用作I/O输出口

一般的数据输出情况:

当CPU执行输出指令时,写脉冲加在D锁存器的CP上,这样与内部总线相连的D端的数据取反后就出现在端口,又经输出级FFT(T2)反相,在P0端口上出现的数据正好是内部总线的数据。

注意:

数据到端口,如输出为“1”,由于T1、T2均不导通,因此无法保证端口为高电平,如接一个上拉电阻,可以保证为高电平。

图中的缓冲器1用于CPU直接读端口数据。

当执行一条由端口输入的指令时,“读引脚”脉冲把该三态缓冲器1打开,这样,端口上的数据经过缓冲器1读入到内部总线。

这类操作由数据传送指令实现。

从图中还可看出,在读入端口引脚数据时由于输出驱动FET(T2)并接在引脚上,如果FET(T2)导通就会将输入的高电平拉成低电平,以致于产生误读。

在端口进行读操作时,如果在前面刚好输出了一个“0”(低电平),则T2是导通的,不管端口是否为低电平,读到的均为“0”。

因此,读端口前一般应先向端口锁存器写入“l”。

保证T2截止。

注意:

Ø如果给端口写1时,T1、T2均不导通,无法保证端口输出为高电平;

Ø读引脚时,没有将T2关闭,端口输入1读到的是0,因此读端口前要保证T2是关闭的,最好给T2写1。

Ø读P0口D锁存器:

8051有几条输出指令功能特别强,属于“读-修改—写”指令。

例如,执行—条“ANLP0,A”指令的过程是:

不直接读引脚上的数据,而是CPU先读P0口D锁存器中的数据,当“读锁存器”信号有效.三态缓冲器2开通,Q端数据送入内部总线和累加器A中的数据进行“逻辑与”操作,结果送P0端口锁存器。

此时,锁存器的内容(Q端状态)和引脚是—致的。

(有时由内部总线输出时,锁存器内容与端口内容可能不一致,以端口接一三极管基极为例,即P口输出为1,但P口实际不是高电平,读锁存器可以保证与运算时P口为1)

3、P0口作为地址/数据总线使用

CPU执行相应指令时(如MOVX指令、EA=0时MOVC指令)片外存储器读写时,控制线C=l,开关MUX拨向反相器输出端。

P0口做地址/数据总线分时使用,先输出地址,然后输入或读入数据。

分为两种情况。

1P0口输出地址/数据总线:

MUX开关把CPU内部地址/数据线经反向器与驱动场效应管FET(T2)栅极接通。

2P0口输入数据:

这种情况也是先输出地址,然后将外存储器地址中的内容通过“读引脚”信号进入内部总线。

4、总结:

●P0既可作一般I/O端口用使用,又可作地址/数据总线使用。

●I/O输出时,必须外接上拉电阻,才能保证高电平可靠输出;

●作I/O输入时,必须先向对应的锁存器写入“1”,使T2截止,才能保证输入的正确。

●当P0口被地址/数据总线占用时,就无法再做I/O口使用了。

●作I/O口时是准双向总线,扩展时是双向总线。

三、P1口

1、P1口某位结构

P1口是一个准双向口。

2、工作原理

作通用I/O口使用。

其电路结构见图,输出驱动部分与P0口不同、内部有上拉负载电阻与电源相连。

编程时输入低8位地址

在8052中,P1.0作定时器2的外部计数触发输入端T2,P1.1作定时器2的外部控制输入端。

3、特点

当P1口输出高电平时、能向外提供拉电流负载,所以不必再接上拉电阻;在端口用作输入时,也必须先向对应的锁存器写入“1”,使T截止。

四、P2口

P2口既可以作通用I/O口,也可以作扩展时地址的高8位。

1、P2口某位结构与工作原理

和P1结构较相似,多了一个模拟开关和控制线。

内部有上拉电阻,故作I/O口时不用再接上拉电阻。

2、作通用I/O口

作通用I/O口时,模拟开关打道下端,注意输出信号是从锁存器的Q端,因此在模拟开关的后面加了一个非门。

复位后模拟开关自动和下面接通,不需要任何控制,直接作为I/O口使用。

1、作扩展地址的高8位

当用到读或写片外扩展存储器或器件的指令时,由指令将模拟开关打到上方,地址高8位信号便可以输出。

注意地址是只输出而不读入,由控制器发指令,从某个地址读数据或给某个地址写数据。

五、P3口

1、作用:

P3口是一个多功能端口:

第—功能:

通用I/O口

第二功能:

其他功能(见右表)

2、结构及工作原理

P3口与P1口的差别在于多了一个与非门和缓冲器,正是这两个部分,使得P3口除了具有P1口的准双向I/O功能之外,还可以使用各引脚所具有的第二功能。

与非门的作用实际上是一个开关,决定是输出锁存器上的数据还是输出第二功能的信号。

复位后第二功能输出端和锁存器输出端Q都是高电平,此时用作I/O口或第二功能都不需要在设置,可以直接应用。

3、P3口作为通用I/O口使用

当作为I/O口时,第二输出功能端保持高电平。

打开与非门,所以D锁存器输出端Q的状态可通过与非门送至FET场效应管输出,这是作通用I/O口输出的情况。

当P3口作为输入使用(即CPU读引脚状态)时。

同P0—P2口一样,应由软件向口锁存器写“1”,即使得锁存器Q端保持为1,与非门0输出为0,FET场效应管截止,引脚端可作为高阻输入。

当CPU发出读命令时,使缓冲器的“读引脚”信号有效,三态缓冲器开通,于是引脚的状态经两个缓冲器到CPU内部路线。

4、P3口用作第二功能使用

当某位被用作第二功能时,该位的D锁存器Q应被内部硬件自动置1,使与非门对第二输出功能端是畅通的。

第二功能输入:

第二功能输入时,读引脚无效。

缓冲器2的作用是避免第二输入功能和端口直连,相互影响。

六、端口的负载能力和接口要求(重要)

P0口的输出级与P1—P3口的输出级在结构上是不同的,因此,其负载能力与接口要求也各不相同。

ØP0口无上拉电阻,每一位输出可驱动8个LS型TTL负载(>800μA)。

ØP1—P3口的输出级接有内部上拉负载电阻,每一位输出可驱动4个LS型TTL负载。

注意:

对于我们在实验和课设中使用的AT89C51和AT89C52,它的最大引脚负载能力如下:

每条引脚最大灌电流(引脚低电平)10mA;

且P0口输入电流之和<26mA,P1、P2、P3各口之和<15mA;

所有端口之和<71mA。

使用时要注意不要超过最大允许电流。

一般通过电阻与端口连接。

对于80c51单片机(CHMOS),端口能提供几毫安的输出电流,故当作输出口去驱动一个普通晶体管的基极(或TTL电路输入端)时,应在端口与晶体管基极间串联一个电阻,以限制高电平输出时的电流。

第五节定时器/计数器(Timer/Counter)

一、概述

1、作用:

在工业检测、控制中,很多场合都要用到计数或者定时功能。

例如对外部脉冲进行计数、产生精确的定时时间、作串行口的波特率发生器等。

2、资源:

8051有两个;8052有3个。

3、可以用作定时器,也可以用作计数器。

4、计满时溢出,并发出中断信号。

二、结构与工作原理

1、计数原理及特点:

1)其核心是16位加法计数器,(高8位为TH×,低8位为TL×);

2)当对内部固定周期的脉冲信号计数时是定时器,对外部输入脉冲信号计数时是计数器;

3)每接收到一个计数脉冲,加法计数器的值就加1;

4)按不同的工作方式,可以作为16位计数器,也可以作为8位计数器。

当计满时发生溢出,申请中断,并又从0开始继续计数。

5)定时器不管是定时还是计数,都不占用CPU时间,只有在溢出中断时才占用CPU时间。

6)定时最短分辨时间:

每一个机器周期计一个数,最短分辨时间为一个机器周期;

7)计数最短分辨时间:

计数时检测过程是有负跳变计数。

在每个机器周期的S5P2采样,要判断负跳变,在1个机器周期检测到高电平,下一个机器周期检测到低电平有效,故需要两个机器周期,所以最短分辨时间是2个机器周期,允许的最高计数频率为晶振频率的1/24。

当89C51采用12MHz晶振时,计数频率最高不超过500KHz。

计数电平保持时间>1个机器周期。

2、结构

其中TH1,TL1位定时器/计数器1的加法器高8位与低8位,TH0,TL0位定时器/计数器0的加法器高8位与低8位。

TCON为控制寄存器;TMOD为方式控制寄存器。

2、

工作模式寄存器TMOD

8位分为两组,高四位控制T1,低4位控制T0。

地址89H,不能位寻址。

对TMOD的各个位的说明:

a、GATE位:

门控位。

1)GATE=1时,T0、T1是否计数要受到外部引脚输入电平的控制,下面详讲。

2)GATE=0,即不使能门控功能,定时计数器的运行不受外部输入引脚INT0、INT1的控制。

b、C/

位:

计数器模式和定时器模式的选择位。

C/

=0,为定时器模式,每个机器周期进行计数1个。

当89C51采用12MHz晶振时,一个机器周期为1μs,计数频率为1MHz。

从计数值可以求得计数的时间,所以称为定时器模式。

(怎么求?

)

C/T=1,为计数器模式,计数器对外部输入引脚T0(P3.4)或T1(P3.5)的外部脉冲(负跳变)计数。

M1M0:

四种工作方式的选择位

M1M0

方式

工作方式

00

0

13位定时器/计数器(TH的8位和TL的低5位)

01

1

16位定时器/计数器

10

2

具有自动重装初值的8位定时器/计数器

11

3

定时/计数器0被拆成两个独立的8位计数器TL0和TH0。

4、控制寄存器TCON

地址88H,可位寻址。

其中有4个位控制定时器/计数器,其他4个位控制中断,在中断部分讲。

控制位介绍:

a、TF0、TF1分别是定时器/计数器T0、T1的溢出标志位,加法计数器计满溢出时置1,申请中断,在中断响应后自动0。

TFx产生的中断申请是否被接收,还需要由中断是否开放来决定。

b、TR1、TR0分别是定时器/计数器T1、T0的运行控制位,可以理解为开关,通过软件置1后,定时器/计数器才开始工作,置0停止,在系统复位时被清0。

(IT1、IT0是中断方式选择,IE1、IE0是中断标志,在中断部分讲)

5、定时器初值的确定:

加法计数器是计满溢出时才申请中断,所以在给定时器/计数器赋初值时,不能直接输入所需的计数值,而输入的是计数器计数的最大值与这一计数值的差值,最大值与方式有关,M为计数器模值,该值和计数器工作方式有关。

在方式0时M为

213=8192;在方式1时M为216=65536;在方式2和方式3时M为28=256。

设最大值为M,计数值为N,初值为X,则X的计算方法如下:

计数状态:

X=M-N

定时状态:

X=M-定时时间/T,T为机器周期,T=12÷晶振频率。

例:

晶振频率为24MHz,定时10ms,初值应设为多少?

X=65536-10000/0.5=45536=B1E0H

三、四种工作方式

1、工作方式0(M1=0、M0=0)

在方式0下,T0和T1工作在13位的定时/计数器方式,由THx的高8位和TLx的低5位组成,计数长度M=213=8192。

当T0的13位计数器加到全部为1以后,再加1就产生溢出,这时置TCON的TF0为1,同时把计数器全部变0,然后从0开始继续计数。

注意:

1)当TR0=1时,GATE=0,与门始终开启,控制开关导通;

GATE=1时,

=1时与门开启。

(

外部中断0引脚P32;若是T1则用

)。

作用:

是T0的外部中断信号,当GATA=1时,定时器/计数器的开始与停止由外部中断信号控制,如果中断信号是一个外部脉冲信号,就很容易测得脉冲信号的宽度。

2)初值也是13位二进制数,将高8位赋值给TH0,低5位前面补足3个0凑成8位赋给TL0。

例如,如要求计数值为1000,则初值为

x=M-1000=8192-1000

=1C18H=1110000011000→1110000000011000B=E018H

则赋初值时,TH0=0E0H,TL0=18H。

(不提倡用方式0)

2、工作方式1(M1=0、M0=1)

方式1和方式0的工作原理基本相同,唯一不同是T0和T1工作在方式1时是16位的计数/定时器。

计数长度M=216=65536

方式1时。

16位的初值直接拆成高低字节,分别送入THx和TLx即可。

3、工作方式2(M1=1、M0=0)

工作方式0和工作方式1的最大特点就是计数溢出后,计数器为全0,因而循环定时或循环计数应用时就存在反复设置初值的问题,这给程序设计带来许多不便,同时也会影响计时精度。

在做定时时钟时,就不容易计时准确。

工作方式2就针对这个问题而设置,它具有自动重装载功能,即自动加载计数初值,所以也称为自动重加载工作方式。

特点:

1)16位计数器分为两部分,即以TLx为计数器,以THx作为预置寄存器,初始化时把计数初值分别加载至TLx和THx中;

2)当计数溢出时,由预置寄存器THx以硬件方法自动给计数器TL0重新装载初值。

经常用于串行通信中的波特率发生器。

可以用于精确定时。

4、工作方式3(M1=1、M0=1)

1、定时/计数器0被拆成两个独立的8位计数器TL0和TH0。

2、TL0是一个完整的8位定时/计数器;定时/计数器0的各控制位和引脚信号全归它使用。

其功能和操作与方式0或方式1完全相同。

3、TH0借用定时/计数器1的控制位TR1和TF1,只能作为简单的定时器使用,即计数溢出时置位TF1,TR1则负责控制TH0定时的启动和停止。

4、定时/计数器T0可以构成二个8位定时器或者一个8位定时器和一个8位计数器。

(不能作为两个计数器)

5、T1可以工作在方式0、1、2,方式3为停止。

注意:

不能响应中断;不能用TR1控制开、停。

设置以后一直循环工作;设置T1工作在方式3,则T1停止工作。

T1一般工作在方式2时,做波特率发生器。

才将T0设置成方式3。

四、定时器/计数器的应用步骤

1、综合考虑设计对象,合理安排资源,选择合适的定时器和工作方式。

如有串行通信,T1就要做波特率发生器,只能用T0做定时或计数。

2、设置工作方式:

解决采用那一个定时器/计数器,采用那种工作方式,是否采用外部中断来控制。

3、计算初值,因为定时器/计数器工作方式都是计满溢出,因此要得到需要的定时时间或预定的数量,就要给置初值。

4、设置中断。

5、开启中断和计数器,计数溢出,在中断程序中要注意先置初值的低位,在置高位。

因为溢出后定时器马上从0开始计数。

6、是否在中断时关闭定时器和中断,根据程序功能要求决定。

第六节中断系统

一、概述

1、查询传送方式

在输入时,需要查询外设的输入数据是否准备好;

在输出时,需要查询外设是否把上一次CPU输出的数据处理完毕。

查询传送方式:

通过查询外设的状态信息,确信外设已处于“准备好”,计算机才发出访问外设的指令,实现数据的传送。

状态信息:

一般为1位二进制码。

优点:

通用性好,可以用于各类外设和CPU间的数据传送。

缺点:

CPU在完成一次数据传送后要等待很长时间才能进行下一次的传送。

在等待过程中,CPU不能进行其他操作,所以效率比较低。

2、中断方式

1)中断的概念

在执行程序的过程中,由于某种外界的原因,必须尽快终止当前的程序执行,而去执行相应的处理程序,待处理结束后,在回来继续执行被终止的程序。

这个过程叫中断。

2)中断技术的优点:

提高CPU的效率;提高实时数据的处理时效;故障处理

3)中断系统的功能:

中断优先权排队;实现中断嵌套;自动响应中断;实现中断返回。

3、几个中断的概念

1)中断系统

实现中断功能的部件称为中断系统,又称中断机构。

2)中断源

产生中断的请求源称为中断源。

注意有几个中断源,都是如何控制的。

3)中断请求

中断源向CPU提出的处理请求,称为中断请求或中断申请。

注意中断被响应后中断申请信号的清除。

4)中断响应过程

CPU暂时中止正在做的事情,完成准备工作后转去处理中断事件的过程。

注意满足那些条件才响应中断申请,响应后要完成那些准备工作。

5)中断服务

对事件的整个处理过程,称为中断服务(或中断处理)。

6)中断返回

中断处理完毕,再返回到原来被中止的地方,称为中断返回。

二、89C51的中断系统

1、中断资源

AT89C51有5个中断源,具有二个中断优先级;

AT89C52有6个中断源,具有二个中断优先级。

可实现二级中断服务程序的嵌套。

(优先级中断普通级)

每个中断源均可软件编程为高优先级或低优先级中断,允许或禁止向CPU请求中断。

AT89C51中有以下中断源:

中断源的特点:

1)外部中断有两种申请方式,一种是低电平触发,一种是负跳变触发。

2)其它中断都是高电平中断。

3)串行通信中断是发送和接收共用一个特殊功能寄存器。

2、控制中断的寄存器

1)寄存器TCON

8F8E8D8C8B8A8988

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

TF0、TF1分别是定时器/计数器T0、T1的溢出标志位,

加法计数器计满溢出时置1,申请中断,在中断响应后自动复0。

IT0、IT1:

外部中断0、1触发方式选择位

0:

低电平触发;1:

负跳变触发

IE0、IE1:

外部中断0、1中断请求标志,负跳变触发后置1,申请中断;

外部中断工作过程:

(T0为例)

ØIT0=0,选择低电平触发,由P3.2口输入低电平,经非门变为高电平,经或门由高电平申请中断;

Ø若IT0=1,负跳变触发,CPU检测到P3.2口输入从高变低的负跳变,给寄存器IE0置1,经或门由高电平申请中断。

注意:

1)低电平触发,不能自动复0;

2)负跳变触发,中断响应后自动复0;

3)用负跳变触发可以用来计数

2)寄存器SCON中的中断标志位

TI:

串行口发送中断请求标志。

CPU将一个数据写入发送缓冲器SBUF时,就启动发送。

每发送完一帧串行数据后,硬件置位TI。

但CPU响应中断时,并不清除TI,必须在中断服务程序中由软件对TI清0。

RI:

串行口接收中断请求标志。

在串行口允许接收时,每接收完一个串行帧,硬件置位RI。

同样,CPU响应中断时不会清除RI,必须在中断服务程序中由软件对RI清0。

3)中断允许寄存器IE

AFHADHACHABHAAHA9HA8H

EA

--

ET2

ES

ET1

EX1

ET0

EX0

A8H

该寄存器可以位寻址。

置1允许中断,清0关闭中断

EX0、EX1:

外部中断0、1允许位

ET0、ET1:

定时器/计数器T0、T1中断允许位

ES:

串行口中断允许位

EA:

中断总允许位

以上控制EA理解为总开关;其它位理解成控制各中断的分开关;总开关与各分开关均为串联关系。

4)中断优先级控制寄存器IP

在51系列中可以设2个中断优先级。

BDHBCHBBHBAHB9HB8H

-

-

PT2

PS

PT1

PX1

PT0

PX0

B8H

该寄存器可以位寻址。

置1为优先级,置0为普通级。

由软件置1或清0。

最多只能设置两个优先级。

PX0、PX1:

外部中断0、1允许位

PT0、PT1:

定时器/计数器0、1中断允许位

PS:

串行口中断允许位

PT2:

定时器/计数器2中断允许位,52中使用。

3、中断响应过程及特点

1)中断响应顺序

Ø在不同级别的响应申请中,优先响应高优先级的申请;

Ø在同一响应级别的中断申请中,按查询次序响应前边的。

Ø同一级别的中断申请不能打断正在执行的中断,高级别的中断申请可以打断正在执行的低一级的中断。

2)中断程序存放的起始地址:

各个中断源的中断入口地址均已由系统规定,中断程序必须严格按规定的地址存放,不能改动。

中断源

INT0

C/T0

INT1

C/T1

串行口

入口地址

0003H

000BH

0013H

001BH

0023H

由于两中断入口地址之间只有8个单元,当中断程序大于8个时,在入口地址处跳转指令。

3)中断响应过程(如图所示)

Ø每个机器周期的S5P2都顺序采样每一个中断源;

Ø将采样值在下一个机器周期的S6P1和S6P2期间按优先顺序进行查询;

Ø在第三个机器周期的S1P1响应中断,跳到规定的中断地址执行中断程序。

对于顺利的中断响应,其最短的响应时间为3个机器周期。

在查询时遇到下列情况则不执行该次中断响应:

(1)CPU正在处理相同或更高级的中断请求;

(2)现在的机器周期不是执行指令的最后一个机器周期;

(3)正在执行的指令是RETI或对寄存器IE、IP的写操作指令。

(执行这些指令后,至少再执行一条指令后才会响应中断)。

最多5个周期。

(这样估计,最长指令4周期,因此相应中断的时间也就是3-8个机器周期,一般是3-4个机器周期,要求精确计算时间时要考虑,如抢答器等)

4)CPU响应中断时完成工作

Ø把当前PC值存储,保护断点。

Ø将相应的中断服务程序的入口地址送入PC。

Ø对有些中断源,CPU会自动清除中断标志。

Ø跳转到中断入口地址执行中断服务程序。

Ø进入中断后,如果中断中用到累加器A,程序状态寄存器PSW和工作寄存器,要将这些内容推入堆栈。

Ø执行到返回指令RETI,中断服务程序结束,恢复中断前PC内容,A、PSW内容弹出堆栈,返回到原来断点继续执行。

4、中断的返回与中断信号的撤除

1)中断的返回

Ø在中断服务程序中,最后一条指令必须为中断返回指令RETI。

ØCPU执行该指令时,一方面清除中断响应时所置位的“优先级生效”触发器,另一方面