Successive approximation ADC.docx

《Successive approximation ADC.docx》由会员分享,可在线阅读,更多相关《Successive approximation ADC.docx(10页珍藏版)》请在冰豆网上搜索。

SuccessiveapproximationADC

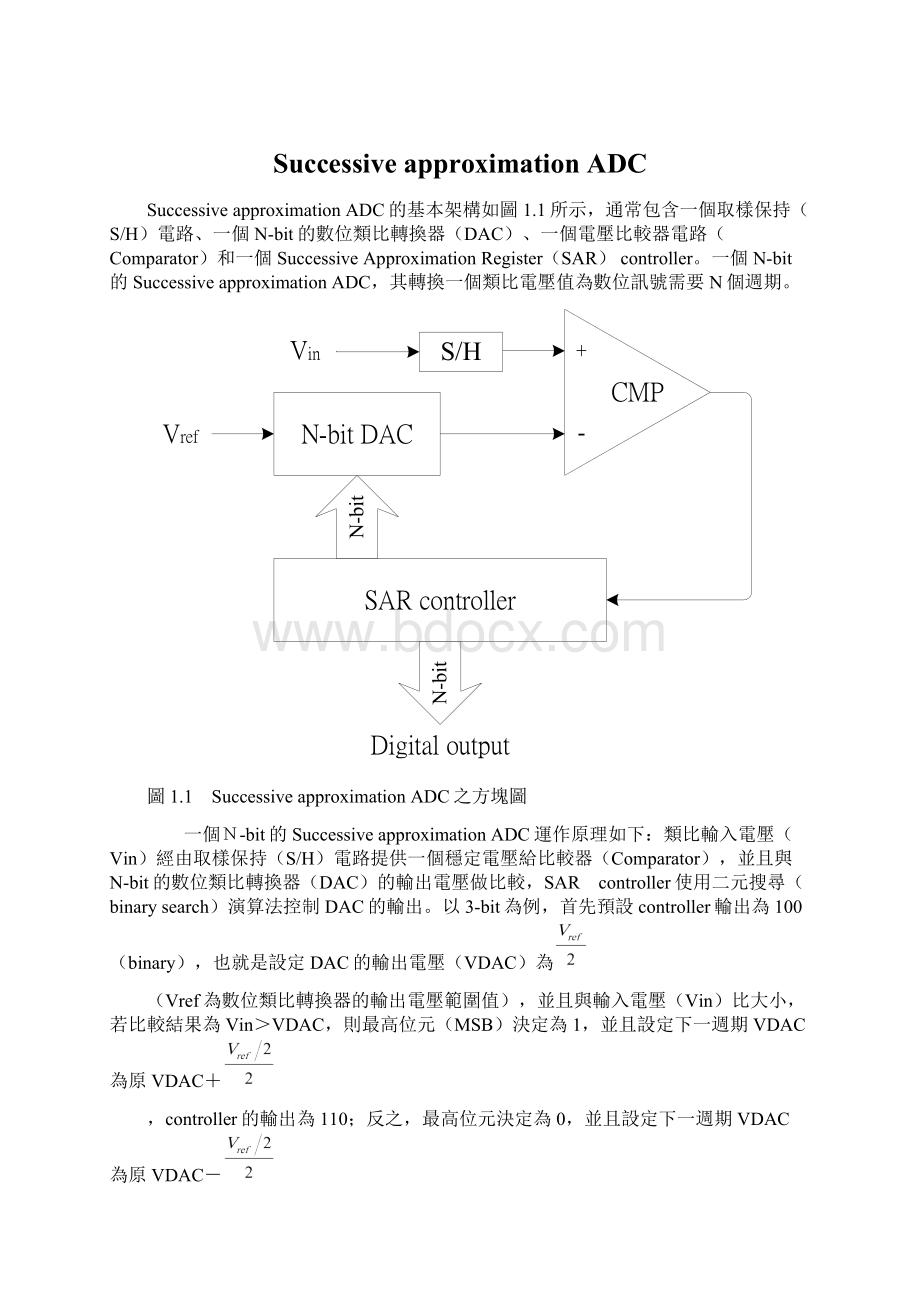

SuccessiveapproximationADC的基本架構如圖1.1所示,通常包含一個取樣保持(S/H)電路、一個N-bit的數位類比轉換器(DAC)、一個電壓比較器電路(Comparator)和一個SuccessiveApproximationRegister(SAR)controller。

一個N-bit的SuccessiveapproximationADC,其轉換一個類比電壓值為數位訊號需要N個週期。

圖1.1 SuccessiveapproximationADC之方塊圖

一個N-bit的SuccessiveapproximationADC運作原理如下:

類比輸入電壓(Vin)經由取樣保持(S/H)電路提供一個穩定電壓給比較器(Comparator),並且與N-bit的數位類比轉換器(DAC)的輸出電壓做比較,SAR controller使用二元搜尋(binarysearch)演算法控制DAC的輸出。

以3-bit為例,首先預設controller輸出為100(binary),也就是設定DAC的輸出電壓(VDAC)為

(Vref為數位類比轉換器的輸出電壓範圍值),並且與輸入電壓(Vin)比大小,若比較結果為Vin>VDAC,則最高位元(MSB)決定為1,並且設定下一週期VDAC為原VDAC+

,controller的輸出為110;反之,最高位元決定為0,並且設定下一週期VDAC為原VDAC-

,controller的輸出為010。

然後再與輸入電壓(Vin)比大小,若比較結果為Vin>VDAC,則次位元決定為1,並且設定下一週期VDAC為原VDAC+

,controller的輸出為X11;反之,次位元決定為0,並且設定下一週期VDAC為原VDAC-

,controller的輸出為X01。

最後再一次與輸入電壓(Vin)比大小,若比較結果為Vin>VDAC,則最低位元(LSB)決定為1,並且controller的輸出為XX1;反之,最低位元決定為0,controller的輸出為XX0。

由此可以得到successiveapproximationADC的最後結果,DAC的輸出電壓會逼近於輸入電壓,並且N個位元就須執行N個週期(Ncycles)。

圖1.2為SARADC以3-bit為例實踐二元搜尋演算法的流程圖,圖1.3為3-bitSARADC之轉換過程。

在clock=1的時候,Vin與

比大小,並產生MSB=1;clock=2時,Vin與

比大小,並產生次位元為0;clock=3時,Vin與

比大小,並產生LSB=1,則此ADC之輸出為101(binary),並且歷時3個週期。

圖1.2 二元搜尋演算法之流程圖

圖1.3 3-bitSARADC之轉換過程

接下來為JanCraninckx所提出之電路的想法,由前述電路,可知SARADC是藉由輸入電壓(Vin)與輸出電壓(VDAC)比較所得的結果,來決定controller的運作方式,進而去改變VDAC的值,這裡我們表示成VinVDAC,則上式可改成

VinVDAC

Vin

+

++

(假設輸入為最大值)

Vin

+

+

++

+

Vin-

--

+

++

VQPVQN

則此電路藉由同時改變VQP與VQN的值,並且比較兩者之大小,來決定controller的運作方式,而VQP與VQN的差值會趨近於零,同樣的,N個位元就須執行N個週期(Ncycles)。

圖1.4為此電路的二元搜尋演算法之流程圖,圖1.5為其轉換圖,在clock=1時,VQP與VQN比

圖1.4charge-sharingSARADC運作流程圖

圖1.5charge-sharingSARADC之轉換過程

大小,也就是Vin與

比大小,並產生MSB=1;clock=2時,Vin-

與

+

比大小,並產生次位元為0;clock=3時,Vin-

+

與

+

-

比大小,並產生LSB=1,則此ADC之輸出為101(binary),並且歷時3個週期。

完整電路實現如圖1.6所示,包含一個取樣保持(S/H)電路、一個N-bit的數位類比轉換器(DAC)、一個電壓比較器電路(Comparator)和一個SuccessiveApproximationRegister(SAR)controlblock。

此電路使用被動式電荷分享(passivecharge-sharing)取代傳統的主動式電荷重佈(activechargeredistribution),來取樣輸入訊號以及實現二元搜尋(binarysearch)演算法。

在ADC開始運作之前,reset訊號先行灌入,使得取樣電容CSP與CSN的值預先清除為零,並且ST導通,SS斷開,則CTP與CTN上儲存了輸入訊號INP與INN的值。

當轉換動作開始之後,ST斷開,SS導通,因為CSP、CSN、CTP與CTN的電容值相同,則儲存在CTP與CTN上的電荷會平均分布到CSP與CSN上,換言之,此時儲存在CSP與CSN上的電壓值為輸入電壓的一半。

而此兩者電壓值在第一個轉換週期時,會先進入比較器比大小,所得之結果將控制controlblock的運作,來決定cp[0…N-2]與cn[0…N-2]是否導通,並產生數位輸出B[0…N-1]。

CU為capacitorarray的單元電容(unitcapacitor),其capacitorarray電路如圖1.7所示,在SARADC中其功能用做DAC,所有電容在ADC轉換之前被預先充電(pre-charge)至供應電壓(Vdd),而後三個電容使用電荷分享(chargesharing)的方法將電荷依序分配給這三個電容,使其分別儲存C.

、C.

與C.

的電荷量,並且在ADC轉換

圖1.6基本charge-sharingSARADC架構

圖1.7Capacitorarray電路

期間,根據controlblock的輸出訊號cp[0…N-2]與cn[0…N-2]來決定capacitorarray的電荷與輸入取樣電荷相加或相減,則在VQP和VQN上的總電荷可表示成CS.VIN/2±CU.VDD。

當clock=1時,VQP與VQN比大小,若比較結果為VQP>VQN,則cp[0]=0,cn[0]=1,相當於CU與S/H電路反接,VQP上的總電荷變為CS.VINp/2-16C.VDD,VQN上的總電荷變為CS.VINn/2+16C.VDD,ADC的輸出B[0]=1;反之,cp[0]=1,cn[0]=0,VQP上的總電荷變為CS.VINp/2+16C.VDD,VQN上的總電荷變為CS.VINn/2-16C.VDD,ADC的輸出B[0]=0。

當clock=2時,改變之後的VQP與VQN比大小,若比較結果為

>

,則cp[1]=0,cn[1]=1,VQP上的總電荷變為CS.

-8C.VDD,VQN上的總電荷變為CS.

+8C.VDD,ADC的輸出B[1]=1;反之,cp[1]=1,cn[1]=0,VQP上的總電荷變為CS.

+8C.VDD,VQN上的總電荷變為CS.

-8C.VDD,ADC的輸出B[1]=0。

依此類推,可依序求出ADC每一個位元的輸出。