NANDFlash调研.docx

《NANDFlash调研.docx》由会员分享,可在线阅读,更多相关《NANDFlash调研.docx(19页珍藏版)》请在冰豆网上搜索。

NANDFlash调研

NANDFlash调研

一、NANDFlash

1.12DNANDFlash

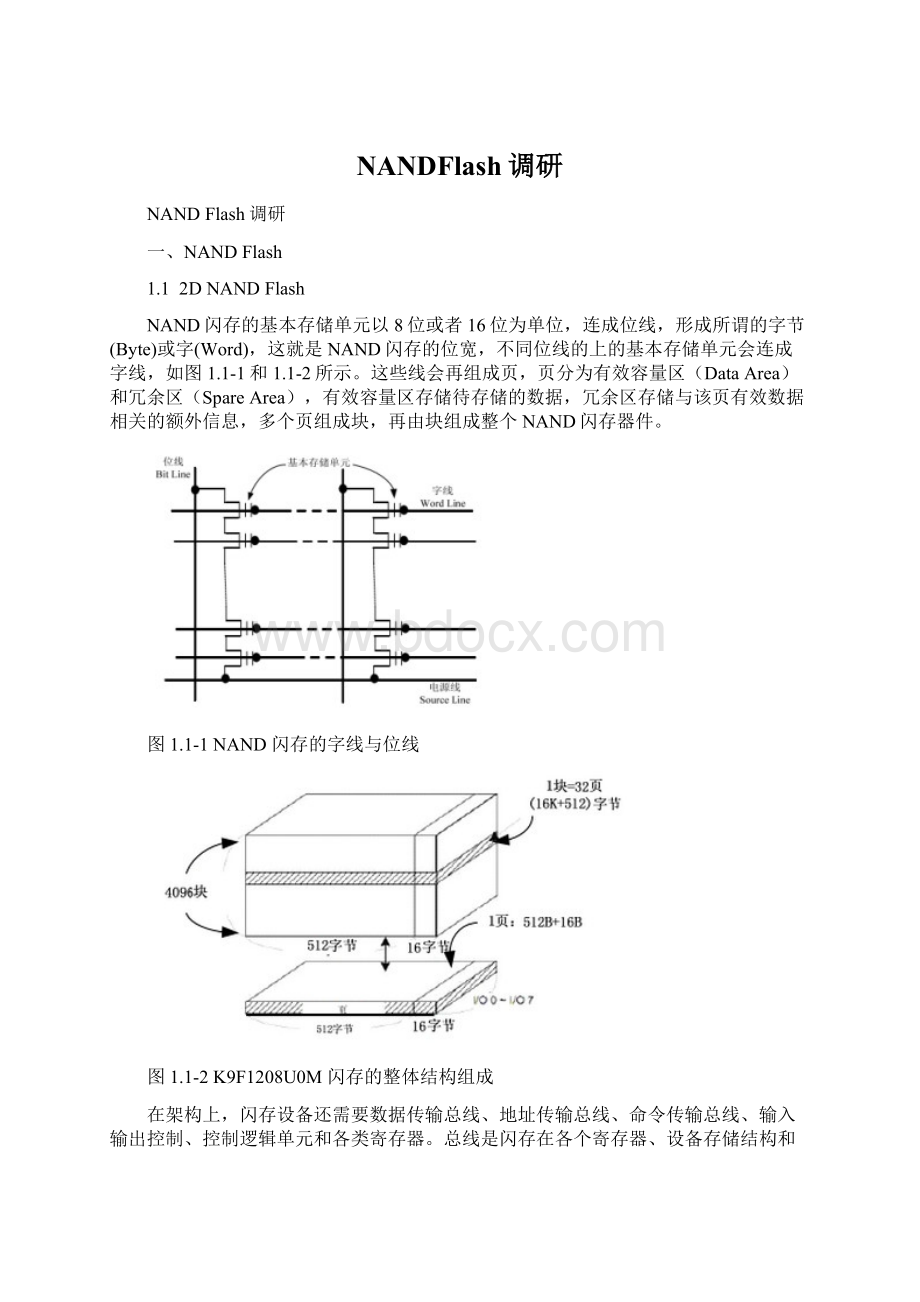

NAND闪存的基本存储单元以8位或者16位为单位,连成位线,形成所谓的字节(Byte)或字(Word),这就是NAND闪存的位宽,不同位线的上的基本存储单元会连成字线,如图1.1-1和1.1-2所示。

这些线会再组成页,页分为有效容量区(DataArea)和冗余区(SpareArea),有效容量区存储待存储的数据,冗余区存储与该页有效数据相关的额外信息,多个页组成块,再由块组成整个NAND闪存器件。

图1.1-1NAND闪存的字线与位线

图1.1-2K9F1208U0M闪存的整体结构组成

在架构上,闪存设备还需要数据传输总线、地址传输总线、命令传输总线、输入输出控制、控制逻辑单元和各类寄存器。

总线是闪存在各个寄存器、设备存储结构和输入输出端之间传送数据、地址或命令的传输线束。

其中,地址传输总线又分为行地址总线和列地址总线两种。

行地址包含了逻辑单元号、块号和页号;列地址指向要获取或更改的数据的起始点所对应的页偏移。

输入输出控制是闪存对外交流数据命令等信息的控制部件。

控制逻辑单元负责根据输入命令和状态寄存器进行对应的操作,如数据传输和设备擦写等。

在设备工作中,为了暂时存储数据、地址和命令,闪存提供了多种寄存器。

每个逻辑单元有一个命令寄存器(CommandRegister)和一个地址寄存器(PageRegister)。

命令寄存器和地址寄存器分别用来暂时存储最后得到的命令和地址。

此外,每个逻辑单元会有一个状态寄存器(StatusRgister)来储存一些必要的状态值。

从工作流程上来看NAND闪存结构如图1.1-3所示:

图1.1-3NAND闪存设备工作结构示意图

1.23DNANDFlash

图1.2-12DNANDFlah架构图

2DNANDFlash已经是一种较为成熟的高密度存储器技术,图1.2-1为其架构图。

它的基本结构是图中的NANDString。

每根NANDString上串联了若干浮栅晶体管,每个浮栅晶体管的浮栅是否存有电子分别表示”0”和”1”的状态。

在读操作过程中,一条NANDString中未选中字线(ML)加高电压保证相应浮栅晶体管一定导通,选中字线施加话当电平,存“1”浮栅晶体管可导通,存“0”浮栅晶体管不导通,然后选中位线(BL)施加一个读电压,未选中位线施加0V电压。

这样,选中的浮栅管若存储数据是“1”,则选中位线到地有一条放电通路,位线电压放电到一个低电平;若浮栅晶体管存储数据是“0”,则选中位线没有放电通路,保持在之前的预充电高电平。

选中位线上最终读出电压的不同即可用来区分“1”和“0”的状态。

图1.2-2为Samsung提出的3DHorizontalNANDFlash三维结构,图中红色竖直线为局部字线,蓝色竖直线为局部位线,灰色水平线为浮栅品体管共用的导通沟道。

图1.2-2(a)3DHorizontalNANDFlash三维结构图(b)浮栅晶体管顶视图

3DHorizontalNANDFlash比2DNANDFlash堆叠了更多层,每次操作时需要额外的层选信号SSL控制。

图1.2-3中展示了SSL的控制方式,图中处阴影中的浮栅晶体管(“off”管)始终处于导通状态,而阴影外的浮栅晶体管(“on”管)只有在施加高电的时候才导通。

这样,要选择某一层,只有在扣应状态为“on”的浮栅晶体管的控制栅上都施加高电平后,这一层才能被选通。

图1.2-3(a)SSL层选选通管电路图(b)SSL操作表

为了克服3DHorizontalNANDFlash利浮栅晶体管去完成层选的这一大弊病,Toshiba提出了3DVerticalNANDFlash的架构。

图1.2-4、1.2-5为该三维结构示意图,它由三个选通信号共同完成浮栅晶体管的选择过程:

BL(BitLine),UpperSG,ControlGate。

其中,BL与传统2DNANDFlash中位线功能相近,ControlGate负责同时选通多层NANDFlash中的控制栅,而UpperSG负责具体选择工作的层,是层选信号。

相对3DHorizontalNANDFlash,3DVerticalNANDFlash已将一条NANDString中用于选层的浮栅晶体管数量减小到了一个,大大提升了存储效率。

图1.2-4(a)3DVerticalNANDFlash结构图(b)浮栅晶体管顶视图

图1.2-53DVerticalNANDFlash电路图

图1.2-6VerticalGateNANDFlash的布局

图1.2-6展示了VerticalGateNANDFlash的布局,

图1.2-73DNANDFlashX截面

8层3DNANDFlashX截面如图1.2-7所示

图1.2-83DNANDFlashY截面

8层3DNANDFlashY截面如图1.2-8所示

二、接口标准

目前市场上的NAND闪存的三种不同接口标准:

普通接口、ONFI(OpenNandFlashInterface)标准和ToggleDDR标准。

2.1普通接口

普通接口是最早的NAND闪存数据通信接口,异步模式,数据传输速度为40MB/s,部不带有ECC(ErrorCorrectingCodes)模块。

2.2ONFI接口标准

2.2.1概述

ONFI(OpenNANDFlashInterface)标准是由英特尔,镁光,海力士,群联电子,SanDisk,索尼,飞索半导体为首宣布统一制定的连接NAND闪存和控制芯片的接口标准,当初制定ONFI标准的主要目的是统一当时混乱的闪存标准。

ONFI1.0制定于2006年12月,容主要是制定闪存的物理接口、封装、工作机制、控制指令、寄存器等规,增加对ECC的支持,传输带宽从传统的Legacy接口的40MB/s提升到50MB/s,性能提升幅度不大,不过其主要目的还是统一闪存接口规,减轻产品厂商的开发压力。

ONFI2.0标准诞生于2008年2月,2.0标准将带宽速度提高到133MB/s以满足高速设备对闪存性能的需求,在该版本中,主要是通过两项技术来提高传输速度。

第一项就是在DRAM领域里常用的DDR(DoubleDataRate,双倍数据率)信号技术。

第二项是使用源同步时钟来精确控制锁存信号,使其能够达到更高的工作频率。

ONFI2.1标准于2009年1月发布,带宽提升到166MB/s和200MB/s(工作模式不同速度不同),8KBpage数据传输延时降低,改良电源管理降低写入操作能耗,加强ECC纠错能力,新增“SmallDataMove”与“ChangeRowAddress”指令。

ONFI2.2发表于2009年10月,增加了LUN(逻辑单元号)重置、增强页编程寄存器的清除和新的ICC测量和规。

LUN重置和页编程寄存器清除提升了拥有多个NAND闪存芯片设备的处理效率,ICC规则简化了下游厂家的测试程序。

ONFI2.3在2010年8月的闪存峰会上发布,在2.2标准的基础上加入了EZ-NAND协议。

EZ-NAND是ErrorZeroNAND的简写,这一协议将NAND闪存的纠错码管理由主控芯片中转移到闪存自身,以减轻主控芯片负担。

ONFI3.0在2011年3月发布,接口带宽提升到400MB/s,需求的针脚数更少让PCB走线更加方便,从目前披露的资料来看,ONFI3.0采用更短的信道、更宽的信号间距,并加入片终止技术,使其传输带宽能够达到400MB/s。

2.2.2引脚分配

ONFI2.0引脚分配

(1)8-bitdataaccess

图2.2.2-1

(2)16-bitdataaccess

图2.2.2-2

2.2.3信号描述

表2.2.3-1

表2.2.3-2

2.2.4存储结构

图2.2.4-1为一个对象memory结构的例子。

该例中,有两个逻辑单元,每个逻辑单元有两层(plane-NAND中存储阵列,每个阵列包含若干个Block)。

一个device包含一个或多个对象(target)。

一个对象由一个CE_n信号控制。

一个对象位于一个或多个逻辑单元(LUN-LogicalUnit)。

一个逻辑单元(LUN)是可独立执行命令并报告状态的最小单元。

特别是,独立的LUN可以并行运行任意的命令序列。

例如,允许在LUN0上开始一个Page编程操作,然后在该操作完成前,可以在LUN1上开始执行一个读命令。

一个block是LUN的闪存阵列中可擦除的最小数据单元。

LUN中block的数量没有明确的限制。

一个block包含若干个pages。

一个page是执行读和编程操作的最小可编址单元。

一个page由若干个字节或字组成。

每个page中用户数据字节的数量,不含括备用数据区(sparedataarea),应该是2的次幂。

每个block的page数量应该是32的整数倍。

每个LUN应该至少有一个page寄存器。

Page寄存器在数据被转移到闪存阵列的一个page之前,或数据被从闪存阵列的一个page转移出来之后,用来零时存放数据。

Page寄存器中的字节或字的位置被称为列。

对这种结构,由两种机制可以达到并行操作的目的。

同一时间可以有多个命令发送到不同的LUNs。

为了在一个LUN中达到更进一步的并行操作,可以使用多层(multi-plane)操作来执行并行的额外dependent操作。

图2.2.4-1存储器结构

2.2.5寻址

有两种地址类型:

列地址和行地址。

列地址用来访问一个page中的字节或字。

行地址用于寻址page,block或LUN。

当列地址和行地址都被请求时,列地址始终首先在一个或多个8位地址周期中被发送,行地址在接下来的一个或多个8位地址周期中被发送。

一些功能可能只需要行地址,像块擦除(BlockErase),这种情况下不用发送列地址。

对于列寻址和行寻址,第一个地址周期总是包含最低地址位,而最后一个地址周期总是包含最高地址位。

如果行地址和列地址的最高位没有用,则要求最高位清除为0。

行地址的结构如图2.2.5-1,最低地址位在右,而最高地址位在左。

图2.2.5-1行地址结构

多层地址包含图2.2.5-2所示的block地址的最低位。

当在LUN上执行一个多层命令序列时,以下规则应适用于多层地址:

图2.2.5-2Plane地址位置

1、层地址位(planeaddressbit(s))应区别于多层命令序列中的其他任何多层操作。

、Page地址应该和多层命令序列中的其他任何多层操作相同

2.3ToggleDDR接口标准

NAND闪存市场的主要占用者三星和东芝在2010年推出了它们的ToggleDDR1.0标准,ToggleDDRNAND采用双向DQS信号控制读写操作,信号的上升与下降沿都可以进行资料的传输,能使传输速度翻倍,接口带宽为133MB/s,而且没有置同步时钟发生器(即NAND还是异步设计),因此其功耗会比同步NAND更低。

2010年8月,最新的ToggleDDR2.0接口标准发布,传输带宽上升到400MB/s。

2.3.1

2.3.2

2.3.3

2.3.4

2.3.5尚未找到更多资料

三、芯片资料

3.1ONFI接口

镁光256GbNANDFlash芯片介绍

芯片型号:

MT29F32G08CBACA

该芯片是一款典型的大容量NANDFlash存储颗粒,支持OpenNANDFlashInterface(ONFI)2.1的接口标准,采用ONFINANDFlash的操作协议。

该芯片采用Multiple-levelCell(MLC)技术,根据不同的容量,一个芯片部封装了多个DIE(LUN),每个DIE由两个Plane构成,一个Plane可以分成2048个Block,每个Block由256页组成,一个页的大小为8KB+448B的组织结构方式。

在性能方面,一个Page页的读延迟在50us左右,页编程时间为900us,块擦除时间长达3ms。

每个块的标称擦除寿命达到5000次。

一个NANDFlash物理芯片可以由多个DIE(或者称之为LUN)的单元构成,每个DIE会有一套独立的上述提及的控制信号线。

一个DIE中会存在若干个Plane,每个Plane有许多Block单元组成,一个Block单元是一个最小的擦除单位,并且有数量较多的Page页构成,每次写的最小单元就是一个Page页。

对于容量较小的芯片,芯片厂商只会封装一个DIE,每个DIE的部结构如图3.1-1所示:

图3.1-1芯片MT29F32G08CBACA部结构

对于镁光512Gb芯片,一个DIE部集成了两个Plane,通过一套控制信号线和寄存器控制部的两个Plane同时并发工作。

值得一提的是,多个DIE(LUN)可能会共享一套控制信号线,因此,在物理上多个DIE会被封装成一个Target。

需要注意的是,同一个Target部的DIE虽然共享了物理信号线,但是寄存器都是相互独立的。

因此,从结构上来看,一个NANDFlash的部架构可以只由一个DIE(LUN)构成,如图3.1-2所示:

图3.1-2NANDFlash部架构

也可以在一个芯片中集成多个DIE(LUN),每个DIE拥有一套独立的物理信号线,如图3.1-3所示:

图3.1-3每个DIE拥有一套独立的物理信号线

在高密的封装中,没有那么多的物理信号线,那么同一个Target中会集成多个DIE(LUN),如果图3.1-4所示:

图3.1-4同一个Target中集成多个DIE

无论如何去封装,每个DIE(LUN)中的基本结构是相同的。

NANDFlash中一个DIE(LUN)中的存储单元通常由多个Plane构成,其结构如下:

图3.1-5NANDFlash中单个DIE中的存储结构

图3.1-5所示的一个Page页大小为8KB,考虑到sparearea的448字节空间,因此需要14位地址访问一个page页,即地址信号的最低14位为页地址。

一个block块部有256个page页,需要8位地址(Pageaddress,PA)信息去访问一个block块部的不同page页。

一个Plane部存在2048个block块,需要11位(Blockaddress,BA)去访问一个Plane中的不同block块。

一个DIE(LUN)中存在2个Plane,需要一位地址位去访问一个DIE中的不同Plane。

因此,40位地址信息的定义如表3.1-1所示:

表3.1-140位地址信息

CA0~CA13为页偏移访问地址信息,PA0~PA7为页地址信息,BA8为DIE中的Plane选择地址位,BA9~BA19为DIE中的块地址信息,另外,LA0为一个Target中的DIE(LUN)选择地址位,在该NANDFlash芯片中,一个Target中可以集成2个DIE。

在每个Plane单元中都存在两个寄存器:

一个为cache寄存器;另一个为data寄存器。

Cache寄存器的作用是缓存NANDFlash控制器输入的数据,而data寄存器的作用是提升数据读取和写入的性能,数据传输和数据加载之间的操作。

在数据读取和数据写入的过程中,都提供了流水并发操作模式,这类模式都充分利用了这个data寄存器。

3.2ToggleDDR接口

三星4GbD-dieNANDFlashSingle-Level-Cell(1bit/cell)芯片介绍。

芯片型号:

K9F4G08U0D、K9K8G08U0D、K9K8G08U1D、K9WAG08U1D

接口:

ToggleDDR2.0

引脚分配:

图3.2-1芯片引脚分配

图3.2-2引脚功能

命令、地址、输入数据的时间特性

图3.2-3命令、地址、输入数据的时间特性

时序图:

(1)命令锁存周期

图3.2-4

(2)地址锁存周期

图3.2-5

(3)输入数据锁存周期

图3.2-6

(4)读操作

图3.2-7