用SpectreVerilog进行模数混仿.docx

《用SpectreVerilog进行模数混仿.docx》由会员分享,可在线阅读,更多相关《用SpectreVerilog进行模数混仿.docx(12页珍藏版)》请在冰豆网上搜索。

用SpectreVerilog进行模数混仿

用SpectreVerilog进行模数混仿,以Sigma-DeltaADC为例

loghere

loghere@

SpectreVerilog模数混仿,模拟部分用Spectre,数字部分用Verilog-XL.所以还需要安装

CadenceLDV软件,其内含Verilog-XL仿真器.

这里以自行设计的二阶全差分Sigma-DeltaADC为例,详细介绍用SpectreVerilog的仿真过

程.所用工艺库为TSMC0.18u,电源电压:

1.8V.

1.准备

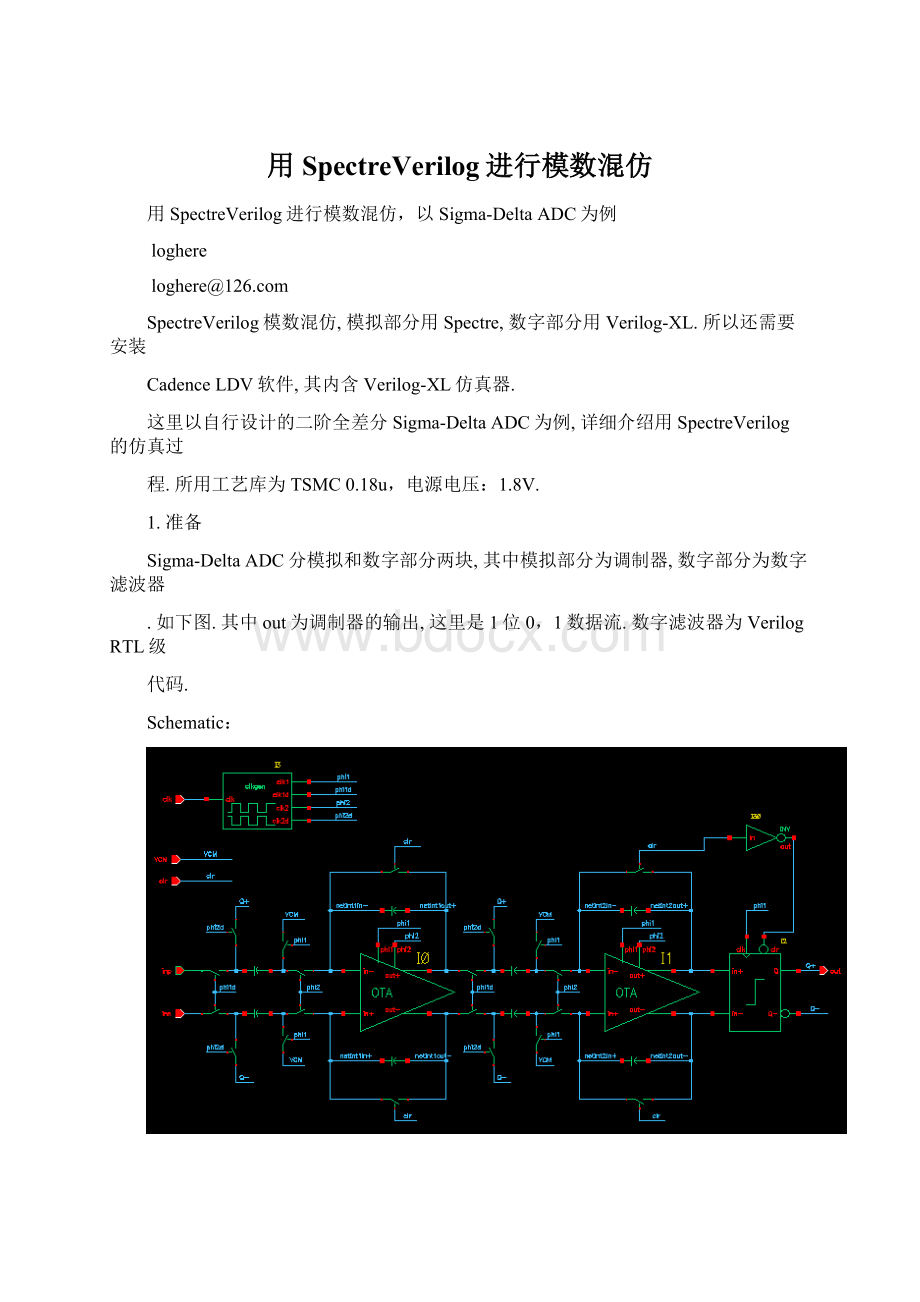

Sigma-DeltaADC分模拟和数字部分两块,其中模拟部分为调制器,数字部分为数字滤波器

.如下图.其中out为调制器的输出,这里是1位0,1数据流.数字滤波器为VerilogRTL级

代码.

Schematic:

Symbol:

VerilogCode:

moduleDigitalFilter(in2out,out,clk,clr,in);

outputin2out;

output[`wordsize-1:

0]out;

inputclk;

inputclr;

inputin;

regin2out;

wireclk_half1,clk_half2;

……

Endmodule

同时为了直观的观看输出结果,因此把输出的数字字转化为模拟量,这里用Verilog-A做一

个理想的DA转换器。

因此最好事先用Spectre仿真模拟部分,用ModelSim或Verilog-XL等仿真数字部分.这里假

定我们已有:

1)模拟部分的原理图(包括Symbol);

2)数字部分的Verilog代码,DigitalFilter.v,模块名:

DigitalFilter(in2out,out,clk,

clr,in);

3)数字部分的TestBench代码,DigitalFilter_TB.v,模块名:

DigitalFilter_TB.

下图为最终的系统图:

2.创建数字模块的Symbol

1)新建一个Cell,ViewName为symbol,Tool:

Composer-Symbol.

2)画Symbol.简单地,画一个矩形框,添加几个Lable,然后添加Pin.

3)添加Pin.左边输入,右边输出.对于多位的pin可以用如out<7:

0>的样式作为pin的名字.

注意:

与模拟部分相连的多位Pin最好不要用一个pin,而要用多个.如下图.

4)创建对应的Verilog文件.在symbol编辑器中,Design菜单->CreatCellView->FromCellView.

会弹出的对话框,Tool/DataType一栏选择Verilog-Editor,则ToViewName会变为functional.

点击OK,会弹出错误对话框,点No.自动弹出VI编辑器,可以看到已经生成Verilog代码的空壳.

代码文件的路径在VI编辑器的标题栏上.下面要做的就是把我们的数字模块(不是TestBench)的

代码填进去.如果不想用VI编辑器,也可以用其他文本编辑器.复制代码时最好不要动自动生成

的代码.经测试,所有代码最好放在一个文件中.

这一步之后,数字部分就会有functional和symbol两个View。

这样基于Verilog代码的Symbol就创建完了.

3.创建理想DAC

这里用Cadence自动生成的理想DAC。

同步骤2,首先创建Symbol,如下图:

类似步骤2,Design菜单->CreatCellView->FromCellView.Type选择VerilogA-Editor

OK,弹出对话框,可以直接按OK,默认设置。

弹出新的对话框,选择DigitaltoAnalogConverter,然后Next。

设置位数,电压范围等参数。

如下图:

Next之后,会出现VerilogA代码,再Save和Finish。

完毕。

4.创建顶层原理图.

1)新建步骤1中所说的顶层Schematic视图,这里名为MixSim,把模拟的Symbol和上面建立的

数字块Symbol放到新建的原理图中,并连好线.模拟块输入端的激励源都要加上.

2)添加数字块的Pin.把数字块中除了和模拟块相连的输入端添加Pin.这里的数字块输入端

信号与模拟块共用,因此没有输入Pin。

5.创建config视图

1)新建Cell,名字和步骤4中的原理图名字一致.Tool选择Hierarchy-Editor,则ViewName

会自动为config.OK,

2)在新出现的NewConfiguration窗口中View:

文本框为空,填入:

schematic,注意大小写.

点击下方的UseTemplate…,->Name一栏选择:

spectreVerilog,OK,

3)再OK关闭NewConfiguration.点击Cadencehierarchyeditor窗口的保存按钮,关闭退出.

4)这时MixSim有两个View:

config,schematic.打开config,会提示打开模式,直接OK,

则原理图会被打开,并可以进行修改。

6.建立仿真环境

1)打开config视图,菜单Tools->AnalogEnvironment,打开ADE.

2)ADE,菜单Setup->simulator,Simulator选择spectreVerilog,OK.

3)ADE,菜单Setup->Stimuli->Analog,弹出Setup窗口,选中GlobalSources,把电源电压

填上,这一步和spectre一样,另外别忘了添加模型库.不再赘述.

4)添加数字块的测试向量.ADE,菜单Setup->Stimuli->Digital,弹出VI编辑窗口,窗口的

标题栏和信息栏都有测试向量的文件路径,可以直接修改它.系统自动生成了一个initial块,

这个initial块不能改动.现在就可以把Testbench中的代码复制到这个文件中了.注意:

`timescale不要复制,模块名和端口定义不要复制,模块实例引用不要复制.也就是只能复制

initial块和always块以及parameter语句.同时注意到,系统生成的的initial块中把输入信号

初始化为零,因此复制进来的语句一定要避免在0时刻给这些信号赋值.本例数字块的输入与

模拟块共用,因此不用添加代码。

5)打开Config视图,菜单Tools->MixSignalOpts.,会新增加一个Mixed-Signal菜单栏。

菜单Mixed-Signal->InterfaceElements->Library…

主要修改两个参数d2a-vh,d2a-vl,他们是输出数字信号的0,1电压

把ModelIO选为Input,修改a2d_v0,a2d_v1,他们是模拟转数字的阈值电压,这里为0.6V和

1.2V

7.仿真.

仿真过程与Spectre一样,设置瞬态仿真时间,输出节点电压。

这是ADC仿真结果图:

由于搭建整个仿真环境比较复杂,因此经常会出错,需要耐心调试,尤其是Verilog代码错误,

仿真器只说有错,但不知道错在何处,很不爽.

本教程仅适用于初学者,同时请高手指点一二,错误和走弯路都在所难免,谢谢。