逻辑门电路.docx

《逻辑门电路.docx》由会员分享,可在线阅读,更多相关《逻辑门电路.docx(28页珍藏版)》请在冰豆网上搜索。

逻辑门电路

第二章逻辑门电路

逻辑符号表示的电路功能须通过具体器件才能实现,各种类型的门电路就是实现逻辑功能的基本单元。

门电路既有双极型晶体管(BJT)组成的三极管-三极管逻辑(TTL)集成门电路,亦有单极型金属氧化物绝缘栅型场效应管(MOSFET)构成的互补型(CMOS)集成门电路。

两种最常用的晶体三极管是双极型晶体三极管和绝缘栅型场效应晶体三极管。

双极型晶体三极管是晶体管-晶体管逻辑电路(TTL)的基础,金属氧化物绝缘栅型场效应管则是CMOS集成电路的基础。

实现与,或,非三种基本逻辑运算以及复合逻辑运算的数字电路称为与门﹑或门﹑非门﹑与非门﹑或非门等等。

2.1二极管的开关特性

不同于模拟器件,数字逻辑器件中的半导体器件一般都工作在开关状态。

掌握和了解这些半导体器件的开关特性,对于掌握和了解门电路的组成和工作原理,正确选择和使用门电路是很重要的。

2.1二极管的开关特性

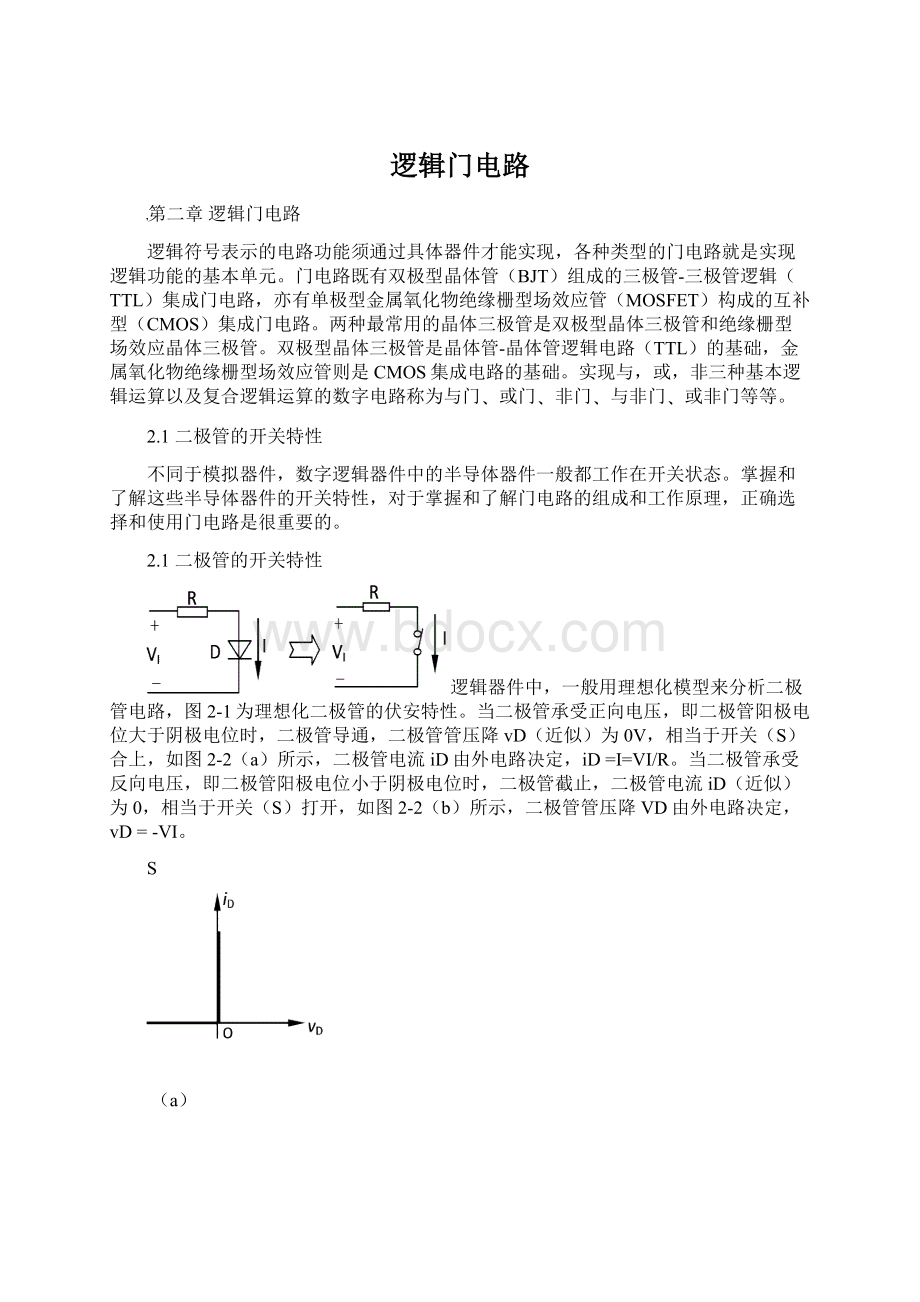

逻辑器件中,一般用理想化模型来分析二极管电路,图2-1为理想化二极管的伏安特性。

当二极管承受正向电压,即二极管阳极电位大于阴极电位时,二极管导通,二极管管压降vD(近似)为0V,相当于开关(S)合上,如图2-2(a)所示,二极管电流iD由外电路决定,iD=I=VI/R。

当二极管承受反向电压,即二极管阳极电位小于阴极电位时,二极管截止,二极管电流iD(近似)为0,相当于开关(S)打开,如图2-2(b)所示,二极管管压降VD由外电路决定,vD=-VI。

S

(a)

S

图2-1理想化二极管的伏安特性

(b)

图2-2二极管等效开关

由上述分析可知,二极管的通(导通)和断(截止)取决于加到二极管上的电压极性。

但二极管从一种开关工作状态变为另一种开关工作状态,即从截止变为导通,以及从导通变为截止,都需要时间,即二极管具有相应的开关特性。

这里所指的二极管开关特性是一种动态特性。

如图2-3所示,二极管从截止变为导通至少需要经过ton时间,二极管电流iD才能达到最大值IF(=VF/R),ton称为(二极管开关)开通时间。

二极管从导通变为截止至少需要经过toff时间,二极管电流iD才能从最大反向电流IR恢复到零,二极管真正变为截止,toff称为(二极管开关)关断时间。

开通时间和关断时间之和ton+toff称为(二极管开关的)开关时间。

图2-3二极管开关特性

2.2三极管的开关特性

数字逻辑电路中,三极管(BJT)一般工作在饱和导通或截止两种开关工作状态。

在图2-4电路中,若iB小于等于零,则iC小于等于ICEO(穿透电流),三极管工作在截止状态。

忽略ICEO,此时三极管相当于一个开关打开,iC=0,vCE=vO=VCC。

为使三极管可靠截止,必须满足三极管截止条件iB≤0。

iB越小,称三极管截止深度越深。

因此输入电压vI必须小于等于三极管死区电压VBE,即vI≤VBE。

在图2-4电路中,若iB足够大,则iC受集电极负载电阻RC影响达到饱和值ICS(集电极饱和电流)。

此时,三极管相当于一个开关合上,忽略三极管饱和压降VCES,有iC=ICS=VCC/RC,vCE=vO=VCES=0。

将IBS=ICS/β=VCC/βRC称为基极临界饱和电流,则三极管饱和条件为iB>IBS。

iB=IBS称为临界饱和,iB越大则称为饱和深度越深。

显然,为满足饱和条件>IBS,输入电压vI必须满足:

vI>RBIBS+VBES。

由以上分析可知,三极管具有可控的稳态开关特性,三极管的开与关和控制电压(vI)有关,vI大于某一电平,三极管开关合上;vI小于某一电平,三极管开关打开。

三极管作为开关,与二极管开关类似,也有相应的动态开关特性,即也有开关时间等动态参数,如图2-5所示。

由图2-5可见,当vI从低电平VIL(三极管截止)跳变为高电平VIH,三极管并不马上饱和导通,而是需要经过一段开通时间ton(IC从0上升到0.9ICS),三极管才能真正饱和导通,三极管开关才算合上。

产生这一段时间的原因有两个。

一是vI=VIL时发射极反偏,空间电荷区较宽,有较多的空间电荷,当vI跳变为VIH,便形成正向基极电流流入基区,抵消势垒区中的电荷,空间电荷区变窄,发射极逐渐正偏,发射到基区并扩散到集电极的载流子被集电极收集,形成集电极电流。

将vI跳变为VIH,iC由0上升到0.1ICS这段时间称为延迟时间td。

二是注入基区载流子有一电荷积累过程,才能形成IC=0.9ICS所需载流子浓度分布,将iC由0.1ICS上升到0.9ICS这段时间称为上升时间tr。

所以开通时间ton是这两个时间之和。

同理,当vI从高电平VIH(三极管饱和)跳变为低电平VIL,三极管也并不马上截止,而是需要经过一段关断时间toff(iC从ICS下降到0.1ICS),三极管才能真正截止,三极管开关才算关断。

造成这一段时间的原因也有两个。

一是vI=VIH时集电极正偏,基区,集电区具有iC=ICS所需的载流子浓度分布,饱和越深由浓度分布形成的存储电荷越多。

vI跳变为低电平VIL,这些存储电荷首先需要释放,将这存储电荷释放时间(iC从ICS下降到0.9ICS)称为存储时间ts。

二是基区中对应于iC=0.9ICS的存储电荷也需要释放,将这些存储电荷释放时间(iC从0.9ICS下降到0.1ICS)称为下降时间tf。

显而易见,关断时间toff是这两个电荷释放时间之和。

2.3基本逻辑门电路

1.二极管与门电路

采用二极管开关组成的与门电路如图2-10(a)所示。

图中三个二极管D1、D2、D3的阳极连接在一起,称为二极管共阳极,这些二极管的阳极经同一个限流电阻R接电源VCC,并作为门电路的输出端L,输出电压VO。

三个输入A、B、C分别接二极管阴极,输入电压分别为VA、VB、VC。

在二极管共阳极结构中,二极管阴极电位最低的二极管优先导通,即VA、VB、VC中哪个电压最小哪个二极管导通。

设输入电压(VA、VB、VC)高电平为5伏,低电平为0伏,电源电压(VCC)为5伏。

当输入中有一个为低电平(譬如VA=0V,VB=VC=5V),对应二极管(D1)优先导通,如图2-11(a),忽略二极管导通压降,输出电压VO=0V。

流过限流电阻R的电流(VCC/R)全部流入这一个二极管(D1),其它二极管(D2,D3)因受反向电压而截止。

图(b)和图(c)分别是输入中有两个为低电平和三个输入全为低电平的工作情况。

此时流过限流电阻R的电流被分流。

图(d)是三个输入全为高电平的工作情况。

将以上各种工作情况下的输入输出电平列表,得表2-1。

若将表2-1中电平用逻辑值表示,所得到的表称为真值表。

在正逻辑体制下,0表示低电平,1表示高电平,得图2-10(a)所示电路正逻辑体制下的真值表,如表2-2。

由表2-2可知,输入中有0(低电平)输出就为0(低电平),只有输入全部是1(高电平)输出才是1(高电平),即具有“见0为0,全1为1”的与逻辑特点。

显然,这是一个(三输入)与门电路,图2-10(b)给出了(三输入)与门的逻辑符号。

2.二极管或门电路

采用二极管开关组成的或门电路如图2-12(a)所示,(b)图为或门逻辑符号。

图中三个二极管D、D2、D3的阴极连接在一起,称为二极管共阴极,这些二极管的阴极经同一个限流电阻R接地,公共阴极作为门电路的输出端L,输出电压VO。

三个输入A、B、C分别接二极管阳极,输入电压分别为VA、VB、VC。

在二极管共阴极结构中,二极管阳极电位最高的二极管优先导通,即VA、VB、VC中哪个电压最高哪个二极管导通。

当A、B、C中有一个高电平(譬如,VA=5V,VB=VC=0V),高电平对应的二极管(D1)导通,低电平对应的二极管(D2、D3)截止,忽略二极管导通压降,输出高电平(VO=5V)。

当A、B、C中有两个高电平(譬如,VA=VB=5V,VC=0V),高电平对应的二极管(D、,D2)导通,低电平对应的二极管(D3)截止,忽略二极管导通压降,输出高电平(VO=5V)。

当A、B、C全为高电平(VA=VB=VC=5V),所有的二极管(D1,D2,D3)均导通,输出高电平(VO=5V)。

以上输入中至少有一个是高电平,输出是高电平。

当A、B、C全为低电平(VA=VB=VC=0V),则所有的二极管(D1、D2、D3)均截止,输出低电平(VO=0V)。

将各种输入输出电平情况列表,得表2-4所示的电平表。

用正逻辑体制表示逻辑电平,表2-4转化为表2-3所示的真值表,即图2-12(a)所示电路是一个正或门电路。

若采用负逻辑体制,表2-4转化为表2-2所示的真值表,即图2-12(a)所示电路是一个负与门电路。

3.三极管反相器(非门)

由三极管构成的反相器(非门)如图2-13所示。

当输入电压为高电平vI=VIH时,三极管T饱和导通,输出为低电平vO=VOL=VCES。

对小功率管来说,三极管饱和压降VCES≈0.3V。

而当输入电压为低电平vI=VIL时,三极管T截止,输出为高电平vO=VOH=VCC=5V。

忽略三极管开关时间,输入输出电压具有反相关系,如(b)图示。

图(c)所示逻辑符号中输出端的小圈就是表示反相关系。

低电平用逻辑值“0”表示,高电平用逻辑值“1”表示,以上分析结果可用真值表(表2-5)表示。

在图2-14中,给出了vI变化时vO发生相应变化的关系曲线,称之为电压传输特性。

输入不同电压,三极管工作在三种不同工作状态。

图中V1,V2是这三种工作状态的分界线。

输入电压小于V1,三极管工作在截止状态,此时输入电压称为输入低电平,记为VIL。

输入电压大于V2,三极管工作在饱和状态,此时输入电压称为输入高电平,记为VIH。

为使三极管工作在开关状态,必须满足以下关系:

VIL≤V1

VIH≥V2。

否则,输出电平的逻辑值会变得含糊不清。

反相器在不同负载条件下有不同的带负载能力。

如图2-15所示,三极管工作在截止状态时,电流流出(非)门电路称为拉电流,对应负载称为拉电流负载。

决定图示电路带拉电流负载能力(即输出高电平电流IOH)的主要因素是输出电阻和高电平值。

随拉电流增大,RC上电压增大,输出(高电平)电压下降。

三极管工作在饱和状态时,电流流入(非)门电路称为灌电流,对应负载称为灌电流负载。

决定图示电路带灌电流负载能力(即输出低电平电流IOL)的主要因素是三极管基极电流和低电平值。

随灌电流增大,三极管饱和程度减小,甚至脱离饱和,进入放大状态,从而使管压降增大,输出(低电平)电压上升。

2.4TTL逻辑门电路

三极管-三极管逻辑(TTL)电路是用BJT工艺制造的数字集成电路,目前国内产品型号为CT74和54系列,对应以前产品型号CT1000系列。

本节以TTL与非门为例,介绍TTL电路的一般组成、原理、特性和参数。

1.TTL与非门内部结构和工作原理

TTL与非门内部基本结构如图2-18(a)所示,多发射极管T1为输入级,T2为中间级,T3和T4组成输出级。

NPN型多发射极管T1的基极类似于图2-16中多个二极管(发射结)的共阳极,当A、B、C中有一个或一个以上为低电平,对应发射结正偏导通,VCC经R1为T1提供基极电流。

设输入低电平VIL=0.3V,输入高电平VIH=3.6V,VBE=0.7V,则T1基极电位VB1=1V,T2因没有基极电流而截止,因此T3也截止。

因为T2截止,VCC经R2为T4提供基极电流,T4导通输出高电平VOH(=VCC–IB4R2-VBE4–VD),由于IB2很小,忽略该电流在R2上