z25GHz的高频电路设计技巧Word格式文档下载.docx

《z25GHz的高频电路设计技巧Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《z25GHz的高频电路设计技巧Word格式文档下载.docx(20页珍藏版)》请在冰豆网上搜索。

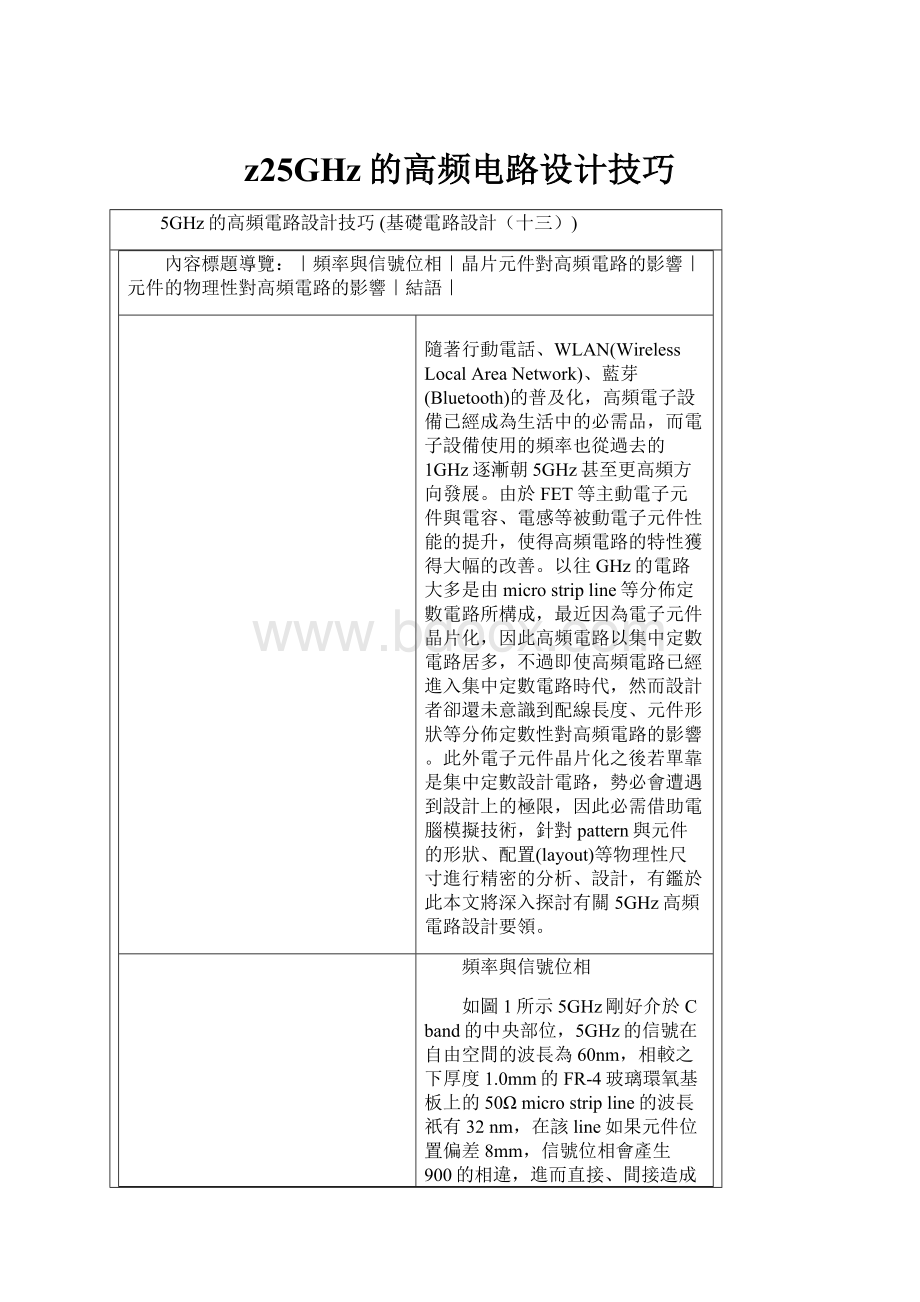

(MHz)

Q的代表值

自我共振頻率(MHz)

直流阻抗(Ω)

測試頻率(MHz)

100

300

500

800

1000

min.

typ.

max.

HK16081NOS

1.0±

0.3

8

14

30

40

70

90

10000

>13000

0.05

0.015

HK16081N2S

HK16085N6□

10

25

33

42

46

4000

5800

0.18

0.09

HK16086N8□

43

47

5600

0.22

0.11

HK16088N2□

26

34

44

48

3500

5200

0.24

0.13

HK1608R15□

50

13

19

16

--

1.2

0.73

HK1608R18□

18

12

400

700

1.3

0.85

HK1608R22□

600

1.5

0.95

表1HK1608系列高頻積層chipinductor的規格摘要

圖2是忽略阻抗成份單純的並聯共振電路。

如果從自我共振頻率計算寄生容量時,寄生容量約為0.125pF左右。

圖3是50Ω插入並聯(series)與分路(shunt)時的模擬(simulation)電路,圖4與圖5分別是並聯(series)與分路(shunt)時的通過特性圖。

為了簡化比較因此上述特性圖使用祇有電感值(inductance)成份的特性表示,而無寄生容量的特性。

由圖5可知插入分路(shunt)與祇有電感成份時,兩者並無太大差異;

相較之下圖4的插入並聯(series)的場合,會以共振頻率為中心出現極大的差異。

換言之若將電感當作偏壓(bias)電路的扼流圈(chokecoil)使用時,寄生容量的影響會比較少,不過若將電感當作matching調整等,亦即所謂的特性調整用途時,寄生容量的影響就會變大。

圖2chipinduct的等價電路

圖3電感串聯與分路的模擬電路

圖4電感串聯電路的通過特性

圖5電感並聯電路的通過特性

幾乎所有的chipcondenser廠商未在產品型錄或是資料表(datasheet)記載該元件的自我共振頻率,因此必需利用類似MCSIL(MurataChipS-parameter&

ImpedanceLibrary)進行chipcondenser的等價電路值。

圖6是MCSIL的畫面。

雖然chipinductor的等價電路為並聯共振電路,不過圖7的chipcondenser卻是串聯共振電路。

接著利用村田公司MCSIL軟體,分析太陽誘電公司1680typeGRM18系列GRM1884C1H1R0CZ01高頻積層chipinductor的自我共振特性,其結果如下所示:

‧自我共振頻率:

5785MHz。

‧阻抗值C:

0.93pF。

‧電感值L:

0.81nH。

圖8是50Ω插入並聯(series)與分路(shunt)時的模擬(simulation)電路;

圖9與圖10分別是並聯(series)與分路(shunt)時的通過特性圖。

為了簡化比較因此用祇有電感值(inductance)成份的特性方式表示,也就是說測試結果並無無寄生容量的特性。

由圖10的測試結果可知50Ω插入分路(shunt)時,會以共振頻率為中心出現極大差異,相較之下50Ω插入並聯(series)時,若與祇有電容(capacitor)成份比較,雖然並未出現很大差異,不過在共振頻率附近的損失卻明顯減少。

由此可知若將電容單純當作藕合電容(couplingcondenser)使用時,電感成份的影響會比較少,相較之下或若將電容當作matching特性調整使用時,電感成份的影響則明顯增加。

圖6MCSIL的實際畫面

圖7chipcondenser的等價電路

圖8電容串聯與分路的模擬電路

圖9電容串聯電路的通過特性

圖10電容並聯電路的通過特性

此外GND(Ground)的設計對高頻電路具有關鍵性的影響,如果未正確設計GND,其結果不單是增幅器等主動電路受到影響,經常連filter等被動電路也無法獲得預期的性能。

以如圖11所示的microstrip電路為例,通常多層電路板內側表層會成為基準的接地層(Groundlayer),封裝於電路板表層的元件接地,則是利用小直徑viahole與內層連接。

為了確認與內側表層連接的表層patter是否屬於GND,因此不斷變更厚0.8的FR4玻璃環氧基板上的viahole直徑,並利用模擬分析探討viahole的阻抗(impedance)特性,亦即所謂電抗(reactance)特性。

圖12是模擬電路,圖13是模擬分析後的阻抗特性。

由分析結果可知viahole具有微量的電抗成份,因此多層電路板表面的GND會比照微量的電抗成份,從內側基準的接地層浮現,如圖13所示viahole的直徑越大,電抗成份相對的越小。

此外頻率越高電抗也越大,如果將viahole視為inductor,並計算等價性電感值其結果為:

0.067Nh@R=0.5mm

基板材質:

FR4。

基板厚度:

0.8mm。

頻率:

5GHz。

根據實驗結果顯示基板厚度越薄,viahole直徑越大且複數設置時,基本上可以有效減緩電抗。

圖11連接表、裏層GND的viahole

圖12viahole的simulation電路

圖13viahole的頻率阻抗特性

晶片元件對高頻電路的影響

接著要介紹chipinduct、chipcondenser以及viahole對5GHzLAN電路的影響,該電路使用Agilent公司的ATF-55143半導體,ATF-55143元件屬於低雜訊強化模式(enhancementmode)的模擬型HEMT(HighElectronMobilityTransistor)。

ATF-55143的輸入為2GHz,VDS=2.7V,IDS=10mA時的特性如下所示:

‧三次IMD的interceptpoint為24.2dBm。

‧1dB壓縮(compression)輸出為14.4dBm。

‧噪訊值(noisefigure)為0.6dB。

‧Gain為17.7dB。

ATF-55143最大的特徵是它的強化模式(enhancementmode),因為一般depletionmode的HEMT,gate電位必需比source的電位低,因此必需設置如圖14(a)所示的gate偏壓(bias)用負電源,或是如圖14(b)所示在source與GND之間插入電阻,使source電位比gate電位高。

而ATF-55143的強化模式(enhancementmode)不需借助其它電子元件,就可使gate電位高於source電位。

具體方法如14(C)所示將source連接於GND,如此便可用正的單電源同時提供偏壓給gate與drain。

圖14HEMT的偏壓方式

接著根據資料表(datasheet)記載的VDS=2.0V,IDS=15mA的S參數與噪訊參數,進行以下三種模擬(simulation)分析:

‧模擬分析1:

使用理想性電子元件,具體而言是GND使用理想性被動電子元件,且HEMT

連接的GND也是理想性。

圖15是可作定數調整的模擬電路;

圖16是噪訊

形態(noisefigure)測試結果;

圖17是Gain測試結果;

圖18是輸出入VSWR測試結果。

根據上述測試結果可知雖然上述測試屬於模擬分析架構,不過卻可獲得很好的特性。

圖15定數調整用模擬電路

圖16理想性元件與GND的噪訊型態測試結果

圖17理想性元件與GND的Gain測試結果

圖18理想性元件與GND的VSWR

‧模擬分析2:

實測值更換成L(電感)與C(電容),同時將viaholeGND也列入考慮,並假設特性會惡化。

圖14電路的L(電感)與C(電容)假設是使用太陽誘電公司的HK1608系列或是GRM18系列的chipinduct與chipcondenser元件,因此必需更換成共振電路,此外還利用viahole將HEMT的source與GND連接進行模擬分析。

chipinduct的寄生容量全部都是0.1pF,chipcondenser串聯電感值(inductance)全部都是0.8nH,基板為厚0.8mm的FR4。

圖19是模擬電路;

圖20是噪訊形態(noisefigure)測試結果;

圖21是Gain測試結果;

圖22是輸出入VSWR的測試結果。

上述測試結果若與圖16~18的測試結果比較時,很顯然的是所有的特性都朝低頻方向偏離惡化,換言之所有的特性都無法使用。

圖19實際L、C與viaholeGND的模擬電路

圖20實際L、C與viaholeGND的噪訊型態測試結果

圖21實際L、C與viaholeGND的測試結果

圖22實際L、C與viaholeGND的VSWR

模擬分析3:

電路的基本結構不變,祇是將定數調整盡量接近理想條件的特性。

圖23是調整後的電路;

圖24是噪訊形態(noisefigure)測試結果;

圖25是Gain測試結果;

圖26是輸出入VSWR的測試結果。

根據測試結果顯示雖然代表marker的5.25GHz附近的值與理想條件非常接近,不過各特性都成為窄頻帶。

‧

圖23考慮實際L、C值的模擬電路

圖24實際L、C值,relayout電路的噪訊型態測試結果

圖25考慮實際L、C值,relayout電路的Gain

圖26考慮實際L、C值與relayout電路的VSWR

元件的物理性對高頻電路的影響

圖23的電路除了viahole之外,其它部份都可視為集中定數進行模擬分析,換言之對5GHz電路而言除了viahole之外,其它部份都應該被視為分佈定數電路處理,如果希望更加提升精度時,必需追加考慮的要素分別如下所示:

‧組裝元件的land之間的連接pattern。

‧元件的物理尺寸。

‧元件與GND之間連接部位的viahole。

以及元件的外形也需列入考量,因為隨著頻率增高,元件組裝位置的變動誤差可能會造成特性上的變化,為了減少上述的影響,例如1608元件最好改用1005大小的元件,1005元件則可以改用0603大小的元件,除此之外同時還需設法提高元件組裝時的位置精度。

改用尺寸較小的電子元件除了可以降低元件的物理性尺寸的影響,還可使電路更容易被當作集中定數特性處理。

當模擬分析結束後開始著手實際電路試作與調整時,盡量依照量產型的基板形狀與尺寸製作,並裝入量產型的筐體內進行特性確認與調整,如果電路基板上方與筐體之間存有寬闊的空間時,該空間會形成導波管效應,尤其是電路基板上設有增幅器之類的主動性電路時,寬闊的空間往往成為引發異常共振的主要原因,而且寬闊的空間會使filter、switch等被動性電路輸出入之間的絕緣(isolation)惡化。

由於頻率越高波長越短,越容易穿透狹窄空間,所以5GHz的電路需要考慮的問題比2GHz的電路更多更瑣碎。

如上所述若將LAN當作microstrip之類的分佈定數電路,基本上祇需用SmithChart與電算機就可完成設計,不過如果是集中定數(亦即chip類元件)與分佈定數(亦即pattern等等)混載的電路,就必需利用其它設計工具(tools)作模擬分析。

例如設計收發信機等大規模電路時,一般會先制定leveldiagram,進行Gain分配分析等前置作業。

不過最近的模擬器(simulator)例如Eagleware公司的GENESYSV8會依照各電路方塊圖,自行定義噪訊形態(noisefigure)、Gain、IP3、P1dB,並進行系統整體的各種特性與spurious特性分析。

圖27是使用GENESYSV8的模擬器,將高頻收發信機電路以block方式輸入,進行系統分析時的畫面。

圖27GENESYSV8模擬器分析高頻收發信機電路系統時的畫面

結語

以往除了微波爐之外幾乎所有的GHz高頻電子產品幾乎都屬於軍事用品的領域,因此設計者對所謂的GHz高頻電路非常陌生,其中又以電子元件種類的差異,所形成集中定數電路與分佈定數電路特性對高頻電路微妙的影響,更是設計者必需面臨的前所未有衝擊。

除此之外利用模擬器進行系統整體的特性分析,已經成為設計高頻電路時無法或缺的手段。