基于FPGA的数字时钟课程设计Word文件下载.docx

《基于FPGA的数字时钟课程设计Word文件下载.docx》由会员分享,可在线阅读,更多相关《基于FPGA的数字时钟课程设计Word文件下载.docx(25页珍藏版)》请在冰豆网上搜索。

按键(进行模式的选择和调时)

0]TS

模式的选择

EN

使能(复位或计时选择)

D

调节时间的时钟

3、计时:

进行调整时间,正常计时;

(1)正常计时;

(2)调整秒计时;

(3)调整分计时;

(4)调整时计时;

input

分钟计时输出

秒钟计时输出

时钟计时输出

0]DATA_M

0]DATA_S

0]DATA_H

4、选择输出:

进行时间高低位的变换及循环扫描输出:

(1)进行时间高低位的变换;

(2)进行时间的循环扫描;

循环扫描时钟

分钟计时输入

秒钟计时输入

时钟计时输入

0]SEG

进行数码管的选通

[3:

0]OUT

时间的输出

5、译码:

对时间进行七段数码管的译码:

0]DATA_IN

时间的输入

[7:

0]LED

七段译码的输出

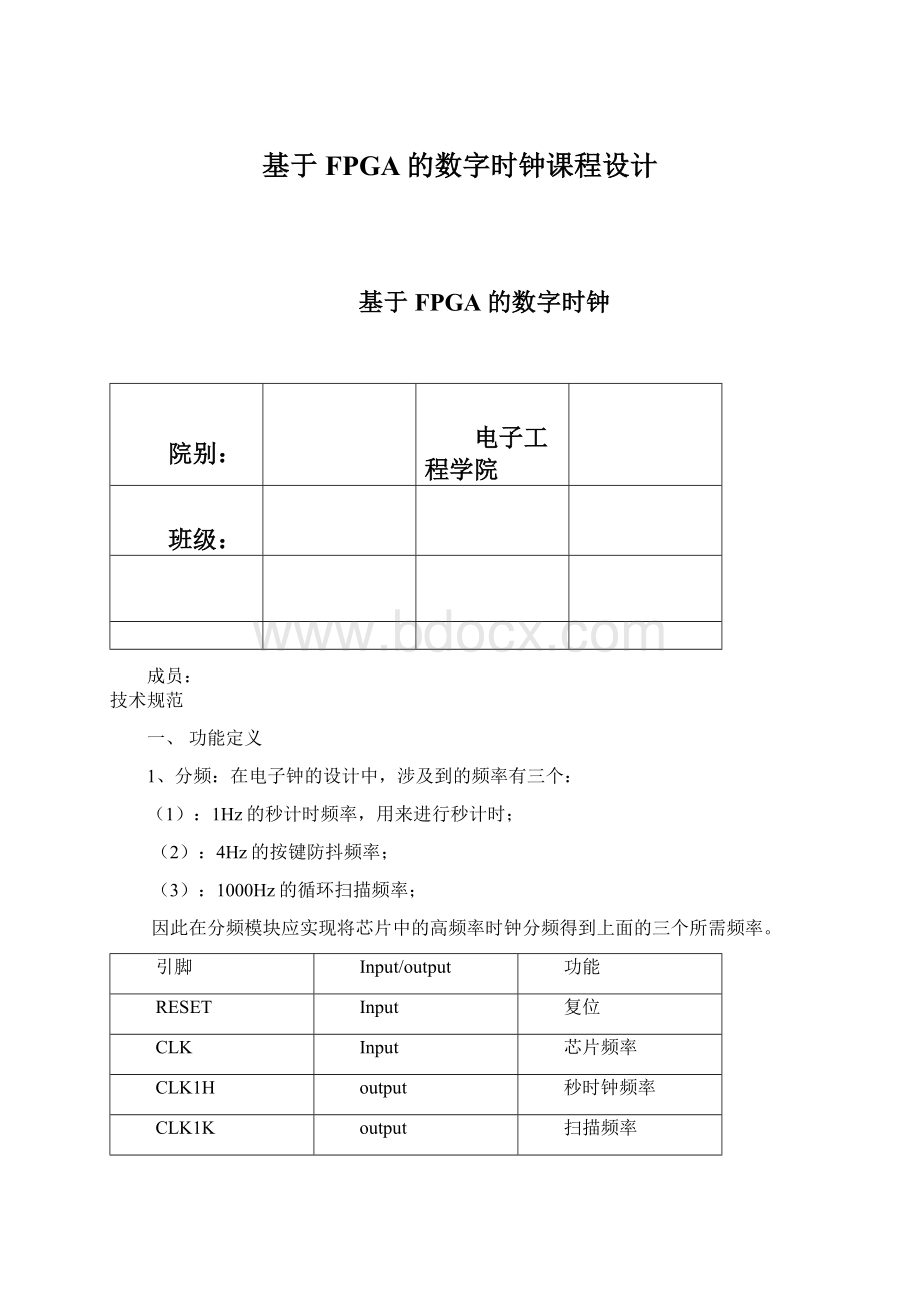

二、总引脚定义

设计思路:

一、总体设计思路图:

二、功能引脚定义

1、总体引脚

(1)K[1]:

输入,控制是否进入调整模式,调时模式或调分模式。

(2)K[2]:

输入,根据K1的选择进行加1调时。

(3)CLK:

输入,1赫兹,控制秒钟的频率。

(4)CLK1K:

输入,1K赫兹,控制时间的连续扫描输出。

(5)[7:

0]LED:

输出,七段显示译码管的输入。

(6)[5:

0]SEG:

输出,控制六个数码管的是否接通。

(7)SC:

输入,时间复位。

2、

(1)控制模块:

输出控制信号和时分秒计时。

控制信号控制时分秒是否正常计时。

K[1]:

K[2]:

SC:

[5:

0]SEC:

复位秒计时。

0]MIN:

复位、调时分计时。

0]HOUR:

复位、调时时计时。

KEN:

控制是否进行正常及时、进入调时复位状态。

(2)计时模块

秒计时:

输出正常的秒计时或复位计时。

分计时:

输出正常的分计时或复位计时或调时计时。

时计时:

输出正常的时计时或复位计时或调时计时。

(3)时间扫描模块:

利用高频率的时钟不断地循环扫描是分秒计时,以便循环译码;

输出控制信号,控制数码管是否有效;

此模块同时进行时间的高地位的计算与输出。

输入,计时时间。

CLK1K:

输入,1K赫兹,高时钟进行扫描。

0]OUT:

进行时间的输出。

0]SEG:

输出,进行数码管的选通控制。

(4)七段译码管:

对时分秒的高低位进行译码输出显示。

电路设计源代码及生成模块图

总模块:

moduleDZZ_ZH(KEY,RESET,CLK,LED,SEG);

output[7:

0]LED;

output[5:

0]SEG;

input[1:

0]KEY;

inputRESET;

inputCLK;

reg[6:

reg[5:

wireWCLK1H,WCLK1K;

wire[5:

0]WMIN,WSEC;

wire[4:

0]WHOUR;

wireWEN,WD,WB;

wire[1:

0]WTS;

wireWCO1,WCO2;

wire[3:

0]WOUT;

0]WDATA_S,WDATA_M;

0]WDATA_H;

wireWCLK4H;

DZZ_FPA1(.CLK(CLK),.CLK1H(WCLK1H),.CLK1K(WCLK1K),.RESET(RESET),.CLK4H(WCLK4H));

DZZ_TA2(.KEY(KEY),.RESET(RESET),.HOUR(WHOUR),.MIN(WMIN),.SEC(WSEC),.TS(WTS),.D(WD),.EN(WEN),.CLK4H(WCLK4H));

DZZ_SA3(.DATA_S(WSEC),.SEC(WDATA_S),.CLK(WCLK1H),.KEN(WEN),.CO(WCO1),.TS(WTS),.D(WD));

DZZ_MA4(.DATA_M(WMIN),.MIN(WDATA_M),.CLK(WCO1),.KEN(WEN),.CO(WCO2),.D(WD),.TS(WTS));

DZZ_HA5(.DATA_H(WHOUR),.HOUR(WDATA_H),.CLK(WCO2),.D(WD),.KEN(WEN),.TS(WTS));

DZZ_SLA6(.DATA_S(WDATA_S),.DATA_M(WDATA_M),.DATA_H(WDATA_H),.OUT(WOUT),.CLK1K(WCLK1K),.B(WB),.SEG(SEG));

DZZ_YMA7(.DATA_IN(WOUT),.LED(LED),.D(WB));

Endmodule

一、分频:

moduleDZZ_FP(CLK,CLK1H,CLK1K,RESET,CLK4H);

outputCLK1H,CLK1K,CLK4H;

inputCLK;

inputRESET;

regCLK1K,CLK1H,CLK4H;

reg[12:

0]CNT1;

reg[24:

0]CNT2;

reg[22:

0]CNT3;

always@(posedgeCLKornegedgeRESET)

begin

if(!

RESET)

begin

CNT1<

=13'

b0000_0000_0000_0;

CLK1K<

=0;

end

elseif(CNT1==13'

b1000_0010_0011_0)

begin

CNT1<

CLK1K<

=~CLK1K;

end

else

=CNT1+1'

b1;

end

CNT2<

=25'

b0000_0000_0000_0000_0000_0000_0;

CLK1H<

elseif(CNT2==25'

b1011_1110_1011_1100_0100_0000_0)

CNT2<

CLK1H<

=~CLK1H;

=CNT2+1'

CNT3<

=23'

b0000_0000_0000_0000_0000_000;

CLK4H<

elseif(CNT3==23'

b1011_1110_1011_1100_0100_000)

CNT3<

CLK4H<

=~CLK4H;

=CNT3+1'

endmodule

二、控制模块代码:

moduleDZZ_T(KEY,RESET,HOUR,MIN,SEC,TS,D,EN,CLK4H);

output[4:

0]HOUR;

0]MIN;

0]SEC;

outputD;

output[1:

0]TS;

outputEN;

inputCLK4H;

reg[4:

regEN;

regD;

reg[1:

always@(negedgeRESETorposedgeCLK4H)

HOUR=5'

b00000;

MIN=6'

b000000;

SEC=6'

TS=2'

b00;

EN=0;

D=0;

else

EN=1;

if(!

KEY[1])

TS=TS+1'

TS=TS;

KEY[0])

begin

D=1;

//guanjian

三、计时调整时间模块代码:

(1)小时计时和小时计时的调整:

moduleDZZ_H(DATA_H,HOUR,CLK,D,KEN,TS);

input[4:

0]DATA_H;

inputD;

inputKEN;

regCLK1;

always@(TS)

if(TS==2'

b11)

CLK1=D;

else

CLK1=CLK;

always@(posedgeCLK1ornegedgeKEN)

KEN)

HOUR<

=DATA_H;

if(TS==2'

b00)

if(HOUR<

=5'

b10110)

begin

HOUR<

=HOUR+1'

end

else

elseif(TS==2'

if(HOUR<

b10110)

begin

HOUR<

end

else

end

=HOUR;

(2)分计时和分计时的调整:

moduleDZZ_M(DATA_M,MIN,CLK,KEN,CO,D,TS);

outputCO;

input[5:

0]DATA_M;

regCO;

regCLK1;

b10)

MIN<

=DATA_M;

if(MIN<

=6'

b111010)

MIN<

=MIN+1'

CO<

=1;

if(MIN<

MIN<

=MIN;

(3)秒计时和秒计时的调整:

moduleDZZ_S(DATA_S,SEC,CLK,KEN,CO,TS,D);

output[5:

input[5:

0]DATA_S;

inputKEN;

input[1:

inputD;

reg[5:

regCO;

regCLK1;

b01)

SEC<

=DATA_S;

if(SEC<

SEC<

=SEC+1'

if(SEC<

SEC<

=SEC;

四、选择模块:

moduleDZZ_SL(DATA_S,DATA_M,DATA_H,OUT,SEG,CLK1K,B);

output[3:

0]OUT;

outputB;

input[4:

inputCLK1K;

reg[3:

regB;

reg[5:

reg[2:

0]SLECT;

parameter

S0=3'

b000,

S1=3'

b001,

S2=3'

b010,

S3=3'

b011,

S4=3'

b100,

S5=3'

b101;

always@(posedgeCLK1K)

case(SLECT)

S0:

OUT<

=DATA_H/6'

b1010;

SEG<

b011111;

B<

SLECT<

=S1;

S1:

=DATA_H%6'

b101111;

B<

=S2;

S2:

=DATA_M/6'

b110111;

=S3;

S3:

=DATA_M%6'

b111011;

=S4;

S4:

=DATA_S/6'

b111101;

=S5;

S5:

=DATA_S%6'

b001010;

b111110;

=S0;

default:

SLECT<

SEG<

b111111;

endcase

五、译码:

moduleDZZ_YM(DATA_IN,LED,D);

input[3:

0]DATA_IN;

reg[7:

S0=4'

b0000,

S1=4'

b0001,

S2=4'

b0010,

S3=4'

b0011,

S4=4'

b0100,

S5=4'

b0101,

S6=4'

b0110,

S7=4'

b0111,

S8=4'

b1000,

S9=4'

b1001;

always@(DATA_IN)

if(D)

case(DATA_IN)

S0:

LED=8'

b11111101;

S1:

b01100001;

S2:

b11011011;

end

S3:

b11110011;

S4:

b01100111;

S5:

b10110111;

S6:

b10111111;

S7:

b11100001;

S8:

b11111111;

end

S9:

b11110111;

end

default:

LED=8'

b00000000;

endcase

else

b11111100;

b01100000;

b11011010;

b11110010;

b01100110;

b10110110;

b10111110;

b11100000;

b11111110;

b11110110;

default:

综合布局布线报告

总体设计模块:

分频、计时、译码;

计时:

控制、秒计时、分计时、时计时、循环选择;

作业心得体会

在本次的作业报告中我学会了如何使用modesim和quartus软件进行电路的验证和仿真。

在电路的设计初始时刻,我没有按照设计电路时从上到下的设计方法,而是盲目的进行对电路的模块进行设计。

结果在最后的设计综合的时候,设计的各个模块不能进行顺利的综合和仿真。

在电子钟的设计中我对时钟的理解不是很透彻,因此在进行计时的时候出现了很多的问题。

在进行时分秒的计时时,我对时间的如何进位没有很好的理解,在计时时出现了很多问题,最后在同学的帮助下得到了很好的解决。

在对按键的使用中我也出现了很困惑的问题。

调整时间的时候,我使用了按键的触发,结果在时间调整计时的时候老是出现时间的快速跳动和不确定性。

最后我引入了按键的扫描时钟,使用4Hz的频率来扫描按键的高低电平,然后利用按键的高低电平来触发调整计时的触发频率,这样很好的解决了按键的抖动问题。

在使用verilogHDL进行电路代码的书写时,应该首先总