CD4511引脚图及功能文档文档格式.docx

《CD4511引脚图及功能文档文档格式.docx》由会员分享,可在线阅读,更多相关《CD4511引脚图及功能文档文档格式.docx(8页珍藏版)》请在冰豆网上搜索。

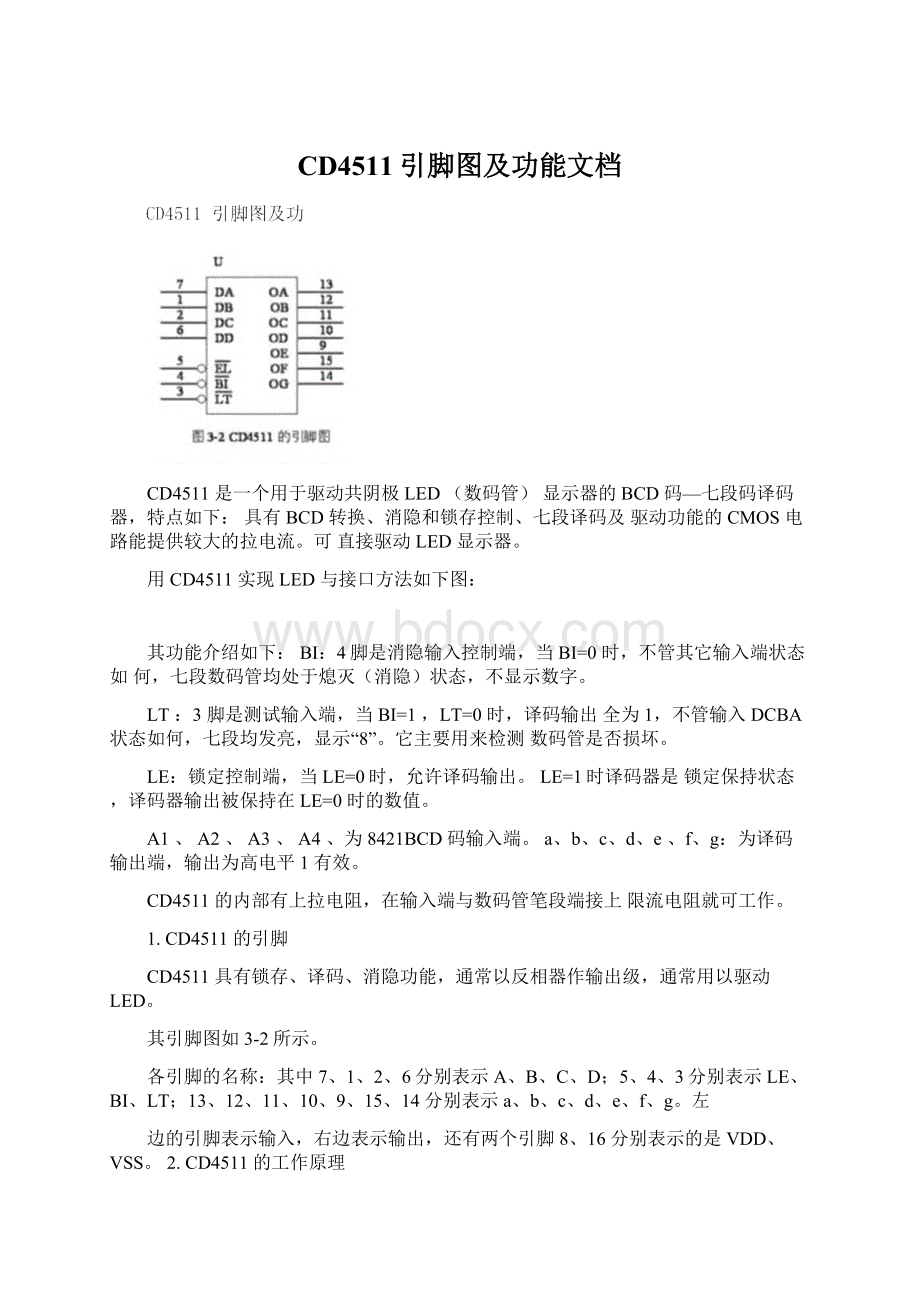

1.CD4511的引脚

CD4511具有锁存、译码、消隐功能,通常以反相器作输出级,通常用以驱动LED。

其引脚图如3-2所示。

各引脚的名称:

其中7、1、2、6分别表示A、B、C、D;

5、4、3分别表示LE、BI、LT;

13、12、11、10、9、15、14分别表示a、b、c、d、e、f、g。

左

边的引脚表示输入,右边表示输出,还有两个引脚8、16分别表示的是VDD、VSS。

2.CD4511的工作原理

1.CD4511的工作真值表如表3-2

2.锁存功能

译码器的锁存电路由传输门和反相器组成,传输门的导通或截止由控制端LE的电平状态。

当LE为“0”电平导通,TG2截止;

当LE为“1”电平时,TG1截止,TG2导通,此时有锁存作用。

如图3-3

(3)译码

CD4511译码用两级或非门担任,为了简化线路,先用二输入端与非门对输入数

据B、C进行组合,得出、、、四项,然后将输入的数据A、D一起用或

非门译码。

(4)消隐

BI为消隐功能端,该端施加某一电平后,迫使B端输出为低电平,字形消隐。

消隐控制电路如图3-4所示。

消隐输出J的电平为

J==(C+B)D+BI

如不考虑消隐BI项,便得J=(B+C)D

据上式,当输入BCD代码从1010---1111时,J端都为“1”电平,从而使显示器中的字形消隐。

输

入

出

LE

BI

LI

D

C

B

A

a

b

c

d

e

f

g

显示

X

1

8

消隐

2

3

4

5

6

7

9

锁存

锁存

表3-2CD4511的真值表

CD4518/CC4518是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器,其功能表如真值表所示。

每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。

由表可知,若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK端置“0”;

若用CL℃K信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”。

RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET端置“0”时,CD4518才开始计数。

CD4518采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;

当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;

当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;

当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。

这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态。

若将第一个加计数器的输出端Q4A作为第二个加计数器的输入端ENB的时钟脉冲信号,便可组成两位8421编码计数器,依次下去可以进行多位串行计数。

CD4520/CC4520为二进制加计数器,由两个相同的内同步4级计数器构成。

计数器级为D型触发器,具有内部可交换CP和EN线,用于在时钟上升沿或下降沿加计数。

在单个单元运算中,EN输入保持高电平,且在CP上升沿进位。

CR线为高电平时,计数器清零。

计数器在脉动模式可级联,通过将Q3连接至下—计数器的EN输入端可实现级联,同时后者的CP输入保持低电平。

引脚功能:

引脚

符号

功能

19

CLOCK

时钟输入端

715

RESET

消除端

210

ENABLE

计数允许控制端

3456

Q1A-Q4A

计数输出端

11121314

Q1B-Q4B

VSS

地

16

VDD

电源正

CD4518CD4520引脚图

CD4518逻辑图

CD4520逻辑图

真值表功能:

CL℃K

ACTION

上升沿

加计数

下降沿

不变

Q0~Q4=0

CD4518CD4520时序图

典型应用电路:

纹波串联4个计数器正极性边缘触发

极限参数:

DCSupplyVoltageRange,(VDD)

-0.5Vto+20V

(VoltageReferencedtoVSSTerminals)

InputVoltageRange,AllInputs输入电压范围,所有投入

-0.5VtoVDD+0.5V

DCInputCurrent,AnyOneInput直流输入电流

±

10mA

OperatingTemperatureRange工作温度范围

-55℃to+125℃

StorageTemperatureRange(TSTG)储存温度范围

-65℃to+150℃

逻辑符号

引出端排列(倫视)

简要说明

CC4060由一振荡粉和14级一进鶴串行计数器位组成,掇药髀的结构可以是RC或晶撮电路.CR为高电平时,墮罰清军且振箔器使用无效.所有的计数Il位均为主从触发器,⅛CPl(和CpII)的下降沿计效器以二进制进行卄数.在时仲眛冲线上使用斯密对时钟上升和下修时间无限制.

CT4060提供了16引线多≡N⅝双列直插(D)、熔封阳晝双列直插(J),塑料双列直插(P)和陶整片状載体(04种封装形式.

推荐工作条件

电涼电压范围3V~15V

辙入电压范PlOV~VDO

工作温度范HS

M类-551~1251

E类-40C~85t

粗限值

电慷电压-Q5V~18V

输入电压-o.5v~VDo+αsv

输人电IS土IOmA

Jt存温度-65C~ISOt

CC4060MDOC4060MJ

CC060EJCOWa)EP

引出堆功能符号

Ql2~Q∣4

L

□

Γ

Z

_

:

Cp1α,o-α,oQ4~-svaovss

时钟输人崩

时怦输出端

反相时钟输出端

什数那输出端

第14级计数器反相输岀端

正电源

CC406OMCCC406OEC

功健衰

人

西

CX

H

清除

I

卄«

保持

321∞:

»

\

«

∏J

Ie

IeJ

h

Wi

9IollISU)

BJlJiBHLflL√r