数字电路实验Multisim仿真汇总.docx

《数字电路实验Multisim仿真汇总.docx》由会员分享,可在线阅读,更多相关《数字电路实验Multisim仿真汇总.docx(58页珍藏版)》请在冰豆网上搜索。

数字电路实验Multisim仿真汇总

数字电路实验Multisim仿真汇总

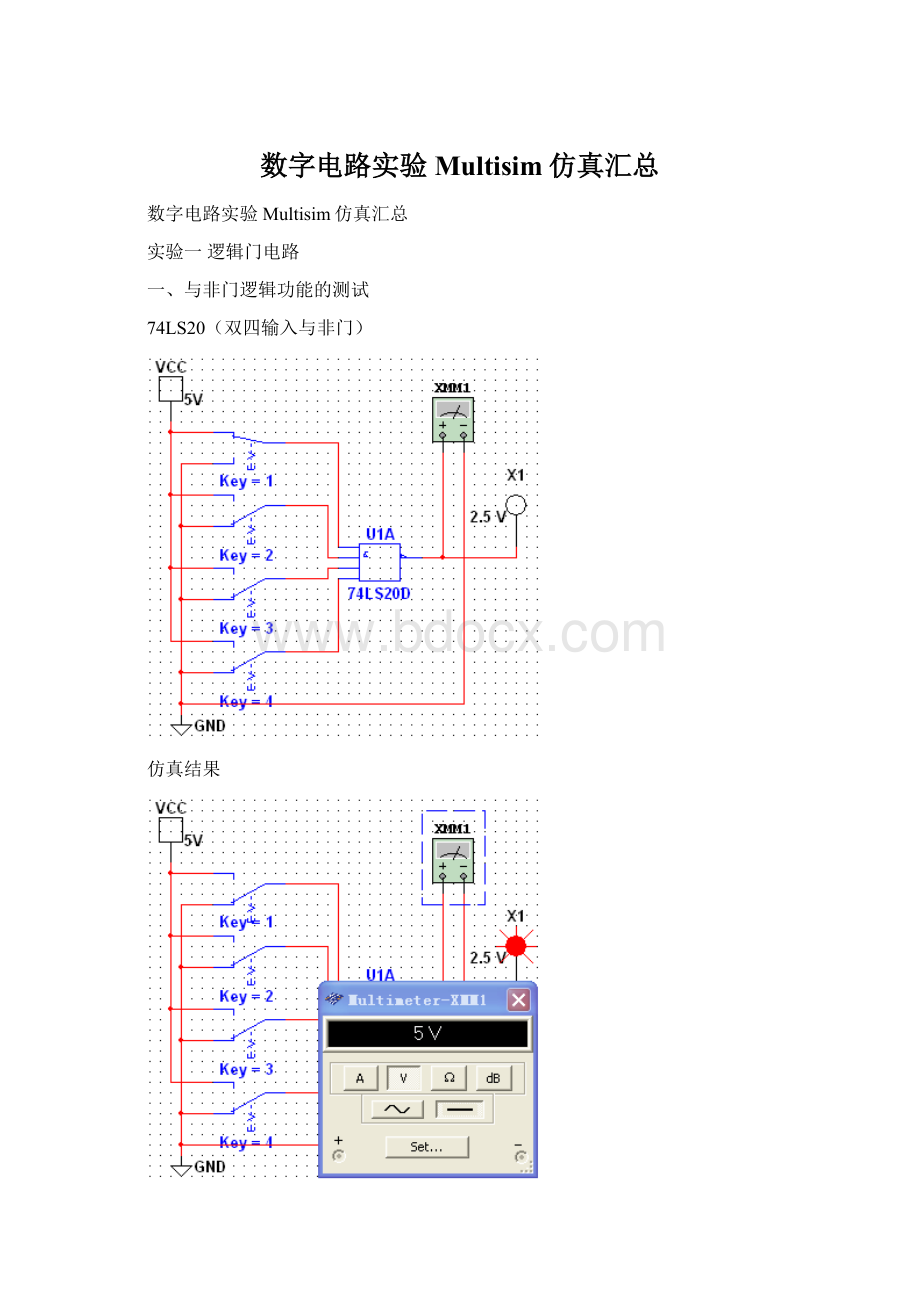

实验一逻辑门电路

一、与非门逻辑功能的测试

74LS20(双四输入与非门)

仿真结果

0

0

0

1

5

1

0

0

1

1

5

1

0

1

1

1

5

1

1

1

1

1

0

0

二、或非门逻辑功能的测试

74LS02(四二输入或非门)

仿真结果:

输入

输出电压(V)

输出逻辑状态

A

B

Y

0

0

5

1

0

1

0

0

1

0

0

0

1

1

0

0

三、与或非门逻辑功能的测试

74LS51(双二、三输入与或非门)

仿真结果:

输入

输出

A

B

C

D

Y

0

0

0

0

1

0

0

0

1

1

0

0

1

1

0

0

1

1

1

0

1

1

1

1

0

四、异或门逻辑功能的测试

74LS86(四二输入异或门)各一片

仿真结果:

输入

输出

A

B

Y

0

0

0

0

1

1

1

0

1

1

1

0

二、思考题

1.用一片74LS00实现Y=A+B的逻辑功能;

2.用一片74LS86设计一个四位奇偶校验电路;

实验二组合逻辑电路

一、分析半加器的逻辑功能

输入

输出

A

B

S

CO

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

二.验证三线-八线译码器的逻辑功能

S1

S2

S3

A2

A1

A0

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

0

φ

φ

φ

φ

φ

1

1

1

1

1

1

1

1

φ

1

1

φ

φ

φ

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

0

1

1

1

1

1

1

1

0

0

0

1

0

1

1

0

1

1

1

1

1

1

0

0

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

0

0

1

1

1

1

0

1

1

1

1

0

0

1

0

1

1

1

1

1

1

0

1

1

1

0

0

1

1

0

1

1

1

1

1

1

0

1

1

0

0

1

1

1

1

1

1

1

1

1

1

0

3.验证数据选择器的逻辑功能

4.思考题

(1)用两片74LS138接成四线-十六线译码器

0000

0001

0111

1000

1111

(2)用一片74LS153接成两位四选一数据选择器;

(3)用一片74LS153一片74LS00和接成一位全加器

(1)设计一个有A、B、C三位代码输入的密码锁(假设密码是011),当输入密码正确时,锁被打开(Y1=1),如果密码不符,电路发出报警信号(Y2=1)。

以上四个小设计任做一个,多做不限。

还可以用门电路搭建

实验三触发器及触发器之间的转换

1.D触发器逻辑功能的测试(上升沿)

仿真结果;

CP

D

Sd

Rd

Q

Q

×

×

1

1→0

0

1

×

×

1

0→1

0

1

×

×

1→0

1

1

0

×

×

0→1

1

1

0

×

×

0

0

0

1

D

CP

Qn+1

Qn=0

Qn=1

0

1

1

0→1

0

0

1

1

1→0

0

0

1

1

1

0→1

1

1

1

1

1→0

1

1

2.JK触发器功能测试(下降沿)

Q=0

Q=0略

J

K

CP

Qn+1

Qn=0

Qn=1

0

0

1

1

0→1

1→0

0

1

0

1

0

1

1

1

0→1

1→0

0

1

0

0

1

0

1

1

0→1

1→0

0

1

1

1

1

1

1

1

0→1

1→0

0

1

1

0

3.思考题:

(1)

(2)

(3)略

实验四寄存器与计数器

1.右移寄存器(74ls74为上升沿有效)

2.3位异步二进制加法,减法计数器(74LS112下降沿有效)

也可以不加数码显示管

3.设计性试验

(1)74LS160设计7进制计数器(74LS160是上升沿有效,且异步清零,同步置数)

若采用异步清零:

若采用同步置数:

(2)74LS160设计7进制计数器

略

(3)24进制

83进制

注意:

用74LS160与74LS197、74LS191是完全不一样的

实验五555定时器及其应用

1.施密特触发器

输入电压从零开始增加:

输入电压从5V开始减小:

3.35-1.65=1.7V

2.单稳态触发器

3.多谢振荡