汽车尾灯控制电路设计毕业设计论文Word文档下载推荐.docx

《汽车尾灯控制电路设计毕业设计论文Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《汽车尾灯控制电路设计毕业设计论文Word文档下载推荐.docx(17页珍藏版)》请在冰豆网上搜索。

直接用AT89S52单片机来实现汽车尾灯控制电路设计。

AT89S52是一种带8K字节闪烁可编程可擦除只读存储器的低电压,高性能CMOS8位微处理器,俗称单片机。

单片机的可擦除只读存储器可以反复擦写1000余次。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89S52是一种高效微控制器,为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

用单片机来实现汽车尾灯控制电路设计,无须外接其他芯片,充分利用了单片机的资源。

3.2方案2——基于电子元件的汽车尾灯控制电路设计

用电子元件接的汽车尾灯控制电路,电路复杂,接点较多,电路稳定性差。

汽车左右和刹车仿真电路

汽车尾灯控制电路设计总体框图

4系统硬件电路的设计

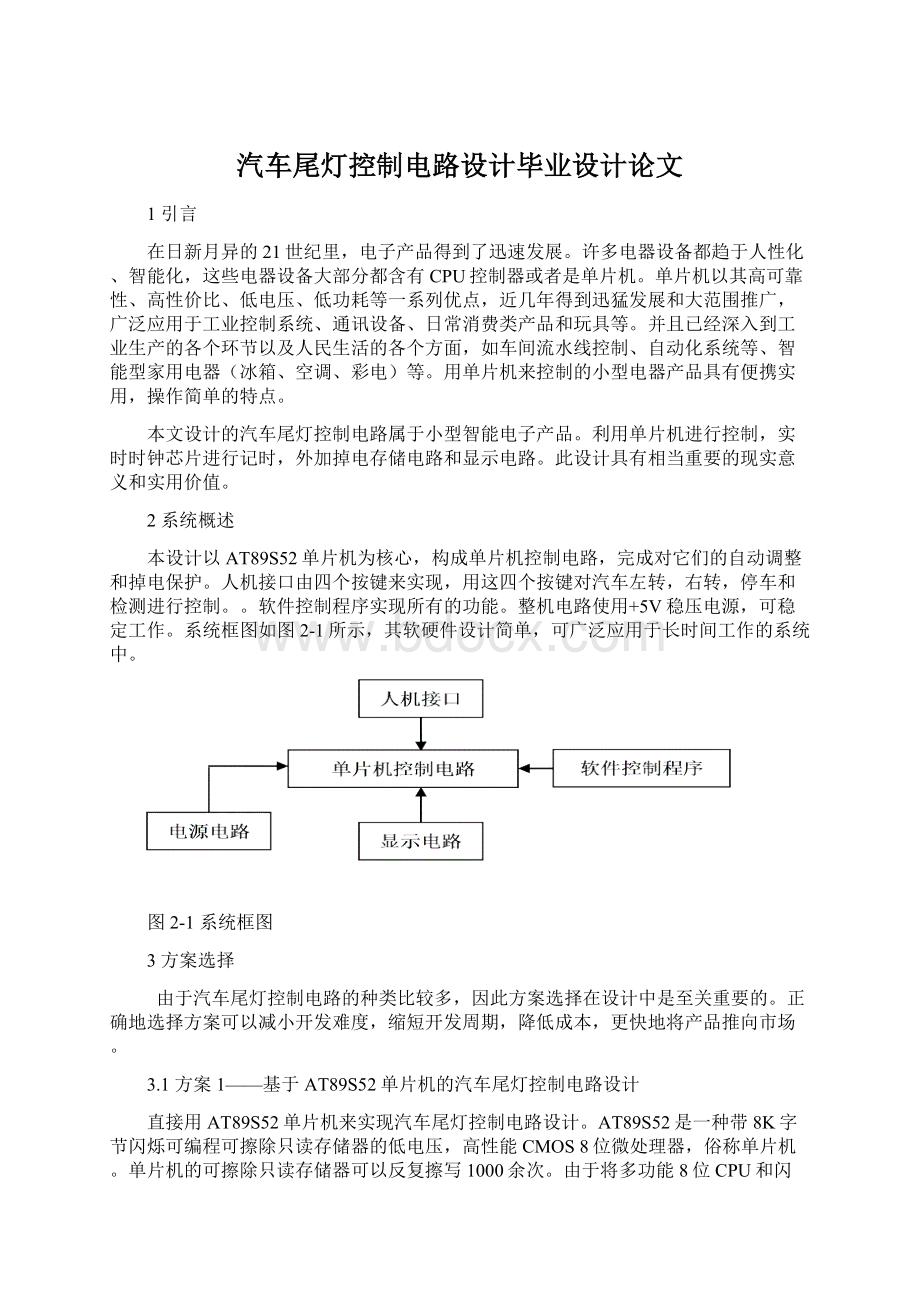

按照系统设计功能的要求,初步确定设计系统由主控模块、键盘接口模块、显示模块共3个模块组成,电路系统构成框图如图4-1所示。

主控芯片使用52系列AT89S52单片机,

图4-1汽车尾灯控制电路系统构成框图

4.1系统核心部分——闪电存储型器件AT89S52

4.1.1AT89S52具有下列主要性能[5]:

·

8KB可改编程序Flash存储器(可经受1000次的写入/擦除周期)

全静态工作:

0Hz~24MHz

三级程序存储器保密

128×

8字节内部RAM

32条可编程I/O线

2个16位定时器/计数器

6个中断源

可编程串行通道

片内时钟振荡器

4.1.2AT89S52的引脚及功能

AT89S52单片机的管脚说明如图4-2所示。

图4-2AT89S52的管脚

(1)主要电源引脚

VCC电源端

②GND接地端

(2)外接晶体引脚XTAL1和XTAL2

XTAL1接外部晶体的一个引脚。

在单片机内部,它是构成片内振荡器的反相放大器的输入端。

当采用外部振荡器时,该引脚接收振荡器的信号,既把此信号直接接到内部时钟发生器的输入端。

②XTAL2接外部晶体的另一个引脚。

在单片机内部,它是上述振荡器的反相放大器的输出端。

采用外部振荡器时,此引脚应悬浮不连接。

(3)控制或与其它电源复用引脚RST、ALE//PROG、/PSEN和/EA/VPP

RST复位输入端。

当振荡器运行时,在该引脚上出现两个机器周期的高电平将使单片机复位。

②ALE//PROG当访问外部存储器时,ALE(地址锁存允许)的输出用于锁存地址的低位字节。

即使不访问外部存储器,ALE端仍以不变的频率(此频率为振荡器频率的1/6)周期性地出现正脉冲信号。

因此,它可用作对外输出的时钟,或用于定时目的。

然而要注意的是:

每当访问外部数据存储器时,将跳过一个ALE脉冲。

在对Flash存储器编程期间,该引脚还用于输入编程脉冲(/PROG)[6]。

③/PSEN程序存储允许(/PSEN)输出是外部程序存储器的读选通信号。

当AT89S52/LV52由外部程序存储器取指令(或常数)时,每个机器周期两次/PSEN有效(既输出2个脉冲)。

但在此期间内,每当访问外部数据存储器时,这两次有效的/PSEN信号将不出现。

④/EA/VPP外部访问允许端。

要使CPU只访问外部程序存储器(地址为0000H~FFFFH),则/EA端必须保持低电平(接到GND端)。

当/EA端保持高电平(接VSS端)时,CPU则执行内部程序存储器中的程序。

(4)输入/输出引脚P0.0~P0.7、P1.0~P1.7、P2.0~P2.7和P3.0~P3.7

P0端口(P0.0~P0.7)P0是一个8位漏极开路型双向I/O端口。

作为输出口用时,每位能以吸收电流的方式驱动8个TTL输入,对端口写1时,又可作高阻抗输入端用。

②P1端口(P1.0~P1.7)P1是一个带有内部上拉电阻的8位双向I/O端口。

P1的输出缓冲器可驱动(吸收或输出电流方式)4个TTL输入。

对端口写1时,通过内部的上拉电阻把端口拉到高电位,这时可用作输入口。

作输入口时,因为有内部的上拉电阻,那些被外部信号拉低的引脚会输出一个电流。

③P2端口(P2.0~P2.7)P2是一个带有内部上拉电阻的8位双向I/O端口。

P2的输出缓冲器可驱动(吸收或输出电流方式)4个TTL输入。

P2作输入口使用时,因为有内部的上拉电阻,那些被外部信号拉低的引脚会输出一个电流。

④P3端口(P3.0~P3.7)P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。

当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。

作为输入,由于外部下拉为低电平,P3口将输出电流,这是由于上拉的缘故。

P3口也可作为AT89S52的一些特殊功能,这些特殊功能见表4-1[7]。

表4-1P3端口的特殊功能

端口引脚

兼用功能

P3.0

RXD(串行输入口)

P3.1

TXD(串行输出口)

P3.2

/INT0(外部中断0)

P3.3

/INT1(外部中断1)

P3.4

T0(定时器0的外部输入)

P3.5

T1(定时器1的外部输入)

P3.6

/WR(外部数据存储器写选通)

P3.7

/RD(外部数据存储器读选通)

4.5键盘电路

本设计共采用按键4个,分别与单片机的P2.0、P2.1、P2.2、P2.3口相连,分别对应汽车左转,汽车右转,刹车和检测的功能。

7结论

本设计硬件电路较简单,所用器件较少,电路中使用了AT89S52单片主要芯片,实现了预计功能。

在对芯片的管脚功能和用法有充分的了解后,根据设计要求设计硬件电路,然后通过软件编程,用按键进行控制,用发光二极管进行显示。

汽车尾灯控制电路可以正常显示汽车的左转,右转,停车和检测功能,基本完成了预期要实现的目标。

参考文献

1.康华光主编,电子技术基础(数字部分),高等教育出版社

2.标准集成电路数据手册TTL电路,电子工业出版社

致谢

不知不觉,六周的毕业设计结束了。

我的毕业论文已整理完毕,电路调试进展良好。

毕业设计的完成意味着我的大学学习生活即将结束,从此我将进入一个新的人生旅途、开始一段崭新的生活——工作。

在此,我衷心地感谢所有在我做毕业设计期间帮助过我的人。

首先我要感谢我的指导老师李杰的大力帮助和支持。

在整个设计过程当中,李老师在大局上指导我毕业设计的每一进程,还在百忙中抽空为我答疑解难,帮我分析讲解毕业设计中所遇到的问题。

不仅如此,李老师还无私的给我提供了丰富的学习资源和良好的学习环境,为我的毕业设计带来了很大方便。

同时在我完成毕业设计的过程中提供了很多指导性的意见,使我受益匪浅。

另外,李老师渊博的学识、严谨的治学态度和为人给了我很大的教育,这些将使我终身受益。

在此,我衷心感谢李老师给予我的帮助和教育。

此外,我还要感谢夏九和李国华同学给予我的无私的帮助,他们在程序编写和调试过程中给予了我莫大的帮助。

在此,我真诚地感谢他们。

最后,我要感谢我的母校——天津工程师范学院,在校期间,这里给我留下了美好的回忆。

特别是在我即将踏上工作岗位的同时,毕业设计整个过程给了我这样一个锻炼的机会,使我加深了对以前知识的理解和巩固,拓宽了知识面,也提高了我对所学知识的综合应用能力。

我要对母校说:

母校有我三五载,我爱母校一万年。

祝愿母校的将来更美好!

附录1:

汽车尾灯控制电路设计电路原理图

附录2主程序

org00h

ajmpstart

ORG001BH;

定时器T1中断程序入口

LJMPtime1;

跳至INTT1执行

org0030h

start:

movTMOD,#10h

movIE,#88h

MOVTH1,#00h

MOVTL1,#00h

movr7,#03h;

setbTR1

turn:

jnbp2.0,is_key

jnbp2.1,is_key

jnbp2.2,is_key

jnbp2.3,is_key

orlp1,#0ffh;

is_key:

jbp2.3,no_check;

anlp1,#0c0h;

jmpturn

no_check:

time1:

pushacc

movTH1,#010h

movTL1,#00h

jbp2.0,left

djnzr7,return

movr7,#3

xrlp1,#3fh

left:

jbp2.1,right

decr7;

cjner7,#6,next1;

movp1,#0fbh

next1:

cjner7,#3,next2;

movp1,#0fdh;

next2:

cjner7,#0,right;

movp1,#0feh

movr7,#9;

right:

jbp2.2,return

cjner7,#6,next11;

movp1,#0f7h

next11:

cjner7,#3,next21;

movp1,#0efh;

next21:

cjner7,#0,return;

movp1,#0dfh

return:

popacc

reti

end

英文资料及中文翻译

6TRANSMISSIONSOFDIGITALDATA:

INTERFACESANDMODEMS

(FromIntroductiontoDataCommunicationsandNetWorking,

BehrouzForouzan)

Oncewehaveencoderourinformationintoaformatthatcanbetransmitted,thenextstepistoinvestigatethetransmissionprocessitself.Information-processingequipmentsuchasPCsgenerateencodedsignalsbutordinarilyrequireassistancetotransmitthosesignalsoveracommunicationlink.Forexample,aPCgeneratesadigitalsignalbutneedsanadditionaldevicetomodulateacarrierfrequencybeforeitissentoveratelephoneline.Howdowerelayencodeddatafromthegeneratingdevicetothenextdeviceintheprocess?

Theanswerisabundleofwires,asortofminicommunicationlink,calledaninterface.

Becauseaninterfacelinkstwodevicesnotnecessarilymadebythesamemanufacturer,itscharacteristicsmustbedefinedandstandardsmustbeestablished.Characteristicsofaninterfaceincludeitsmechanicalspecifications(howmanywiresareusedtotransportthesignal);

itselectricalspecifications(thefrequency,amplitude,andphaseoftheexpectedsignal);

anditsfunctionalspecifications(ifmultiplewiresareused,whatdoeseachonedo?

).ThesecharacteristicsarealldescribedbyseveralpopularstandardsandareincorporatedinthephysicallayeroftheOSImodel.

6.1DIGITALDATATRANSMISSION

Ofprimaryconcernwhenconsideringthetransmissionofdatafromonedevicetoanotheristhewiring.Andofprimaryconcernwhenconsideringthewiringisthedatastream.Dowesendonebitatatime,ordowegroupbitsintolargergroupsand,ifso,how?

Thetransmissionofbinarydataacrossalinkcanbeaccomplishedeitherinparallelmodeorserialmode.Inparallelmode,multiplebitsaresentwitheachclockpulse.Inserialmode,onebitissentwitheachclockpulse.Whilethereisonlyonewaytosendparalleldata,therearetwosubclassesofserialtransmission:

synchronousandasynchronous(seeFigure6-1).

ParallelTransmission

Binarydata,consistingof1sand0s,maybeorganizedintogroupsofnbitseach.Computersproduceandconsumedataingroupsofbitsmuchasweconceiveofandusespokenlanguageintheformofwordsratherthanletters.Bygrouping,wecansenddatanbitsatatimeinsteadofone.Thisiscalledparalleltransmission.

Figure6-1 Datatransmission

Themechanismforparalleltransmissionisaconceptuallysimpleone:

usenwirestosendnbitsatonetime.Thatwayeachbithasitsownwire,andallnbitsofonegroupcanbetransmittedwitheachclockpulsefromonedevicetoanother.Figure6-2showshowparalleltransmissionworksforn=8.Typicallytheeightwiresarebundledinacablewithaconnectorateachend.

Figure6-2 Paralleltransmission

Theadvantageofparalleltransmissionisspeed.Allelsebeingequal,paralleltransmissioncanincreasethetransferspeedbyafactorofnoverserialtransmission.Butthereisasignificantdisadvantage:

cost.Paralleltransmissionrequiresncommunicationlines(wiresintheexample)justtotransmitthedatastream.Becausethisisexpensive,paralleltransmissionisusuallylimitedtoshortdistances,uptoamaximumofsay25feet.

SerialTransmission

Inserialtransmissiononebitfollowsanother,soweneedonlyonecommunicationchannelratherthanntotransmitdatabetweentwocommunicatingdevices.

Theadvantageofserialoverparalleltransmissionisthatwithonlyonecommunicationchannel,serialtransmissionreducesthecostoftransmissionoverparallelbyroughlyafactorofn.

Sincecommunicationwithindevicesisparallel,conversiondevicesarerequiredattheinterfacebetweenthesenderandtheline(parallel-to-parallel).

Serialtransmissionoccursinoneoftwoways:

asynchronousorsynchronous.

AsynchronousTransmission

Asynchronoustransmissionissonamedbecausethetimingofasignalisunimportant.Instead,informationisreceivedandtranslatedbyagreed-uponpatterns.Aslongasthosepatternsarefollowed,thereceivingdevicecanretrievetheinformationwithoutregardtotherhythminwhichitissent.Patternsarebasedongroupingthebitstreamintobytes.Eachgroup,usuallyeightbits,issentalongthelinkasaunit.Thesendingsystemhandleseachgroupindependently,relayingittothelinkwheneverready,withoutregardtoatimer.

Withoutasynchronizingpulse,thereceivercannotusetimingtopredictwhenthenextgroupwillarrive.Toalertthereceivertothearrivalofanewgroup,therefore,anextrabitisaddedtothebeginningofeachbyte.Thisbit,usuallya0,iscalledthestartbit.Toletthereceiverknowthatthebyteisfinished,oneormoreadditionalbitsareappendedtotheendofthebyte.Thesebits,usually1s,arecalledstopbits.Bythismethod,eachbyteisincreasedinsizetoatleast10bits,ofwhich8areinformationand2ormorearesignalstothereceiver.Inaddition,thetransmissionofeachbytemaythenbefollowedbyagapofvaryingduration.Thisgapcanberepresentedeitherbyanidlechannelorbyastreamofadditionalstopbits.

Inasynchronoustransmissionwesendonestartbit(0)atthebeginningandoneormorestopbits(1s)attheendofeachby