nRF51822外部中断学习总结Word格式文档下载.docx

《nRF51822外部中断学习总结Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《nRF51822外部中断学习总结Word格式文档下载.docx(10页珍藏版)》请在冰豆网上搜索。

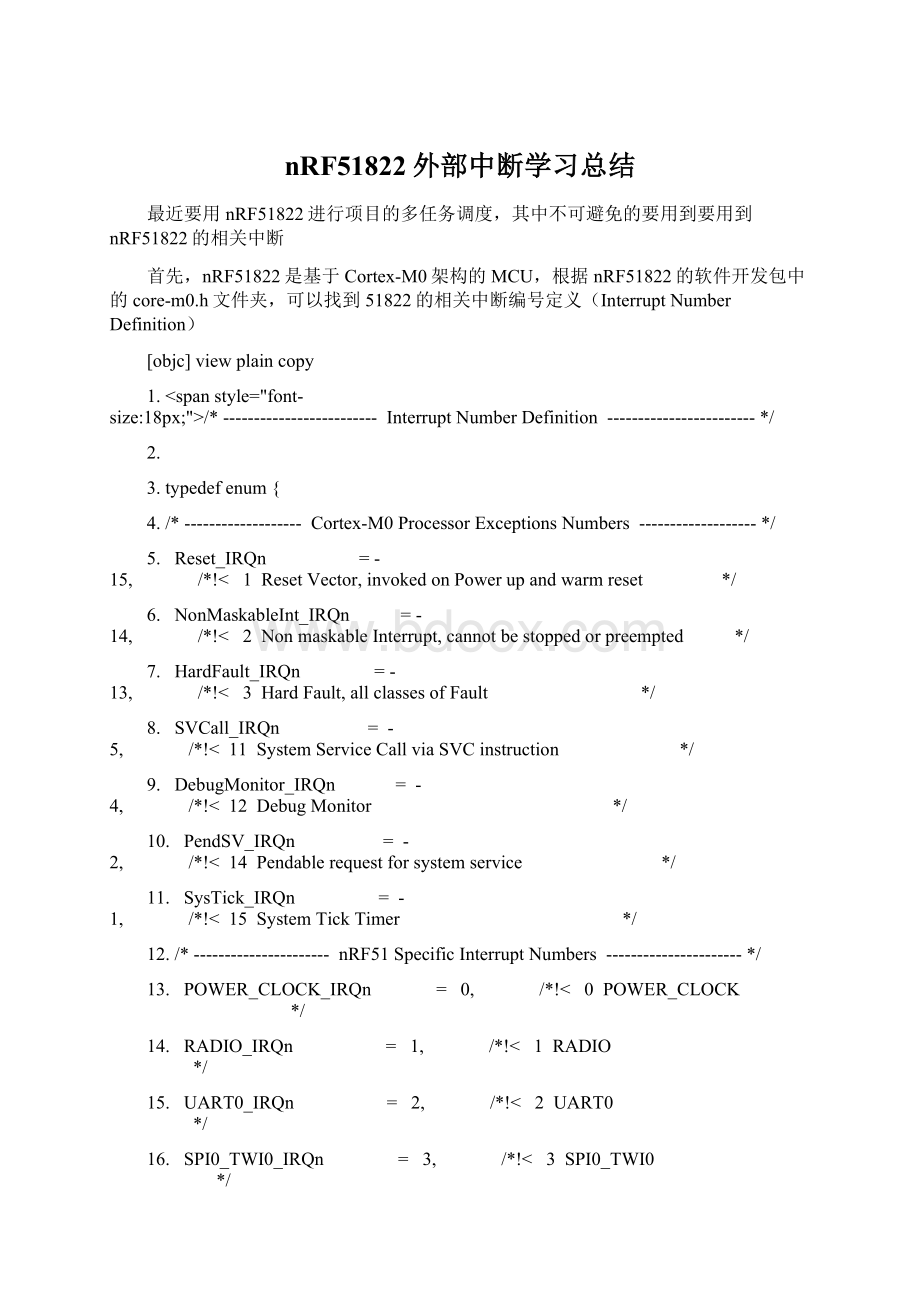

invoked

on

Power

up

and

warm

reset

6.

NonMaskableInt_IRQn

-14,

2

Non

maskable

Interrupt,

cannot

be

stopped

or

preempted

7.

HardFault_IRQn

-13,

3

Hard

Fault,

all

classes

of

Fault

8.

SVCall_IRQn

-5,

11

System

Service

Call

via

SVC

instruction

9.

DebugMonitor_IRQn

-4,

12

Debug

Monitor

10.

PendSV_IRQn

-2,

14

Pendable

request

for

system

service

11.

SysTick_IRQn

-1,

15

Tick

Timer

12./*

----------------------

nRF51

Specific

13.

POWER_CLOCK_IRQn

0,

0

POWER_CLOCK

14.

RADIO_IRQn

1,

RADIO

15.

UART0_IRQn

2,

UART0

16.

SPI0_TWI0_IRQn

3,

SPI0_TWI0

17.

SPI1_TWI1_IRQn

4,

4

SPI1_TWI1

18.

GPIOTE_IRQn

6,

6

GPIOTE

19.

ADC_IRQn

7,

7

ADC

20.

TIMER0_IRQn

8,

8

TIMER0

21.

TIMER1_IRQn

9,

9

TIMER1

22.

TIMER2_IRQn

10,

10

TIMER2

23.

RTC0_IRQn

11,

RTC0

24.

TEMP_IRQn

12,

TEMP

25.

RNG_IRQn

13,

13

RNG

26.

ECB_IRQn

14,

ECB

27.

CCM_AAR_IRQn

15,

CCM_AAR

28.

WDT_IRQn

16,

16

WDT

29.

RTC1_IRQn

17,

17

RTC1

30.

QDEC_IRQn

18,

18

QDEC

31.

LPCOMP_COMP_IRQn

19,

19

LPCOMP_COMP

32.

SWI0_IRQn

20,

20

SWI0

33.

SWI1_IRQn

21,

21

SWI1

34.

SWI2_IRQn

22,

22

SWI2

35.

SWI3_IRQn

23,

23

SWI3

36.

SWI4_IRQn

24,

24

SWI4

37.

SWI5_IRQn

25

SWI5

38.}

IRQn_Type;

39.<

/span>

在进行中断处理时,一般都要按照这个步骤:

1、对要用到的中断初始化;

2、对用到的中断进行使能;

3、对中断进行优先级设置

1、中断初始化

nRF51822的外部I/O(暂时理解的程度以及用过的中断只有I/O中断,其他中断没有实践过)中断是基于任务和事件模式的。

按照nRF51822用户手册,每个GPIOTE通道的以下输入条件可以产生一个事件(在此可将事件理解为一个中断):

上升沿、下降沿或者任何变化。

因此,在进行中断初始化的时候,首先要将相应的中断输入I/O引脚设置为输入模式。

然后通过CONFIG[n]设置GPIOTE通道的模式MODE(任务或者事件)、关联任务OUT[n]或者事件IN[n]的引脚PSEL,触发方式POLARITY。

例如下面是将ROCKER_INTERRUPT引脚初始化为事件下降沿触发的事件IN[0]。

pre

name="

code"

class="

objc"

NRF_GPIOTE->

CONFIG[0]=(GPIOTE_CONFIG_POLARITY_HiToLo<

GPIOTE_CONFIG_POLARITY_Pos)

|(ROCKER_INTERRUPT<

GPIOTE_CONFIG_PSEL_Pos)

3.

|(GPIOTE_CONFIG_MODE_Event<

GPIOTE_CONFIG_MODE_Pos);

在对相关事件的触发方式以及关联引脚初始化完成之后,还需要通过INTENSET寄存器进行使能

1.NRF_GPIOTE->

INTENSET=GPIOTE_INTENSET_IN0_Set<

GPIOTE_INTENSET_IN0_Pos;

//Ê

¹

Ä

Ü

IN0Ê

Â

¼

þ

2、中断使能

在中断初始化中仅仅是对事件n的使能,在此要对相应的中断进行使能。

类比于Cortex-M3架构,在MDK内与NVIC相关的寄存器,MDK为其定义了如下的结构体

NVIC(NestedVectoredInterruptController)嵌套中断向量控制器

14px;

/**

\ingroup

CMSIS_core_register

\defgroup

CMSIS_NVIC

Nested

Vectored

Controller

(NVIC)

\brief

Type

definitions

the

NVIC

Registers

4.

@{

7./**

Structure

type

to

access

(NVIC).

9.typedef

struct

10.{

__IO

uint32_t

ISER[1];

Offset:

0x000

(R/W)

Set

Enable

Register

12.

RESERVED0[31];

ICER[1];

0x080

Clear

RSERVED1[31];

ISPR[1];

0x100

Pending

RESERVED2[31];

ICPR[1];

0x180

RESERVED3[31];

RESERVED4[64];

IP[8];

0x300

Priority

21.}

NVIC_Type;

23./*@}

end

group

*/<

ISER[1]:

中断使能寄存器。

由前边可以看到,nRF51的寄存器编号为0-25,在这里ISER[1]为32位寄存器,总共可以表示32个中断,bit0-bit25分别对应中断0-25(其实后来发现在NVIC_EnableIRQ()函数中是将1左移IRQn位之后又与0x1F,也就是空出了低五位,所以在这里应该是对应的高地址,而把低位给空出来的)。

要使能某个中断,必须设置相应的ISER位为1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、I/O口映射等设置才算是一个完整的中断设置)。

此处是按照STM32中断设置理解的。

ICER[1]:

中断除能寄存器,和ISER的作用恰好相反,用来清除某个中断的使能的。

专门设置一个ICER来清除中断位,而不是向ISER写0来清除,这是因为NVIC的这些寄存器都是写1有效的,写0无效的。

ISPR[1]:

中断挂起控制寄存器。

通过置1可以将正在进行的中断挂起,而执行同级或者更高级别的中断。

ICPR[1]:

中断解挂控制寄存器。

通过置1可以将挂起的中断解挂。

IP[8]:

中断优先级控制寄存器组。

这个寄存器组相当重要。

中断分组与这个寄存器密切相关。

在这里插入一下中断优先级的理解。

因为以前都是用的STM32,在这里就按照Cortex-M3架构来理解。

Cortex-M3中有两个优先级的概念——抢占优先级和响应优先级,有人把响应优先级称作“亚优先级”和“副优先级”,每个中断源都需要被指定这两种优先级。

具有高抢占优先级的中断可以在具有低抢占优先级的中断处理过程中被响应,即中断嵌套。

当两个中断源的抢占优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个(在《原子教你玩STM32》中说在抢占优先级相同的中断,高优先级的响应优先级不可打断低响应优先级的中断,有待考证);

如果他们的抢占优先级和响应优先级相等,则根据他们在中断表中的排位顺序来决定先处理哪一个。

在STM32中需要用NVIC_PriorityGroupConfig(uint32_tNVIC_PriorityGroup)先对中断优先级进行分组,这个分组在一个程序中只能设定一次,是在中断与复位控制寄存器SCB->

AIRCR中设置的,也就是分组之后所有的中断只能按照这个分组方式进行设定抢占优先级和响应优先级。

在对中断优先级进行分组设置之后,要对每个中断的中断源优先级进行设置,也就是设置中断优先级控制寄存器IP,中断源优先级具体设置了该中断源的优先级别。

在此先说一下STM32中断优先级设置的步骤:

系统运行开始的时候设置中断分组,确定组号,也就是确定抢占优先级和子优先级的分配位数,调用函数为NVIC_PriorityGroupConfig();

设置用到的中断的中断优先级别,对每个中断调用函数为NVIC_Init(NVIC_InitTypeDef*NVIC_InitStruct);

而在nRF51822中,我现在还没有碰到中断优先级进行分组的情况,在此就先不写,如果将来用到,再进行相关补充

首先是中断使能,和STM32中在初始化NVIC_InitStruct结构体的同时完成中断使能不同,nRF51822通过专门的函数NVIC_EnableIRQ(IRQn_TypeIRQn)来实现响应中断使能,形参变量IRQn为要进行初始化的中断编号,在本博文的开头已经给出,在SDK的core-m0.h中定义,以下为中断使能函数。

1./**

External

The

function

enables

a

device-specific

interrupt

in

controller.

\param

[in]

IRQn

number.

Value

negative.

7.__STATIC_INLINE

void

NVIC_EnableIRQ(IRQn_Type

IRQn)

8.{

NVIC->

ISER[0]

(1

((uint32_t)(IRQn)

&

0x1F));

10.}

13./**

Disable

disables

19.__STATIC_INLINE

NVIC_DisableIRQ(IRQn_Type

20.{

ICER[0]

22.}

例如,要使能GPIOTE中断,则调用

1.NVIC_EnableIRQ(GPIOTE_IRQn);

3、中断优先级设置

中断优先级设置源函数如下:

sets

priority

an

interrupt.

\note

set

every

core

set.

10.__STATIC_INLINE

NVIC_SetPrior