QuartusII使用教程完整实例2Word文件下载.docx

《QuartusII使用教程完整实例2Word文件下载.docx》由会员分享,可在线阅读,更多相关《QuartusII使用教程完整实例2Word文件下载.docx(13页珍藏版)》请在冰豆网上搜索。

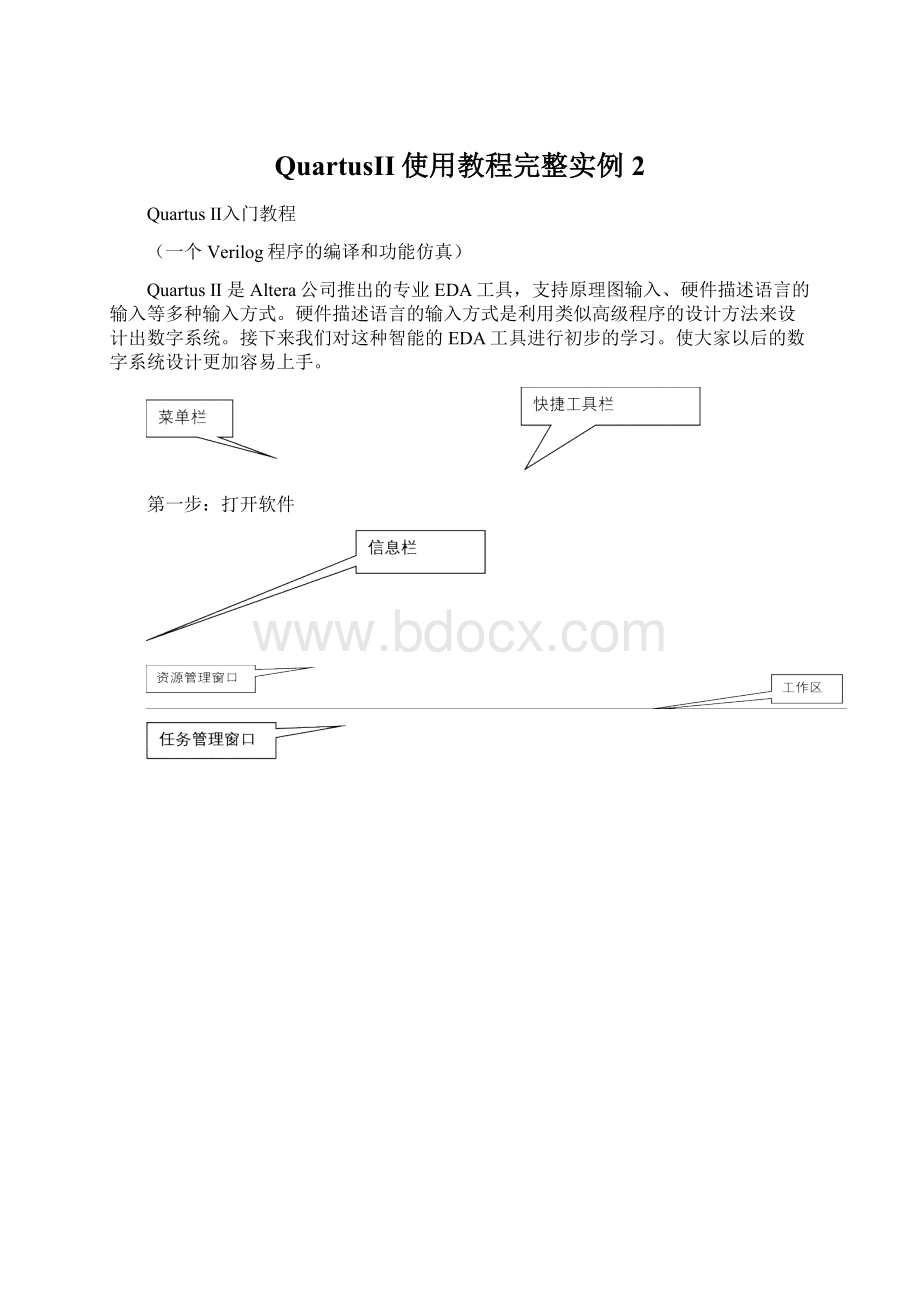

第一步:

打开软件

●快捷工具栏:

提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

●菜单栏:

软件所有功能的控制选项都可以在其下拉菜单中找到。

●信息栏:

编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

第二步:

新建工程(file>

newProjectWizard)

1工程名称:

2添加已有文件(没有已有文件的直接跳过next)

3选择芯片型号(我们选择cyloneII系列下的EP2C70F896C6芯片)

(注:

如果不下载到开发板上进行测试,这一步可以不用设置)

4选择仿真,综合工具(第一次实验全部利用quartus做,三项都选None,然后next)

5工程建立完成(点finish)

第三步:

添加文件(file>

new>

VHDLfile),新建完成之后要先保存。

第四步:

编写程序

以实现一个与门和或门为例,Verilog描述源文件如下:

moduletest(a,b,out1,out2);

inputa,b;

outputout1,out2;

assignout1=a&

b;

assignout2=a|b;

endmodule

然后保存源文件;

第五步:

检查语法(点击工具栏的这个按钮

(startAnalysis&

synthesis))

点击确定完成语法检查

第六步:

(锁定引脚,点击工具栏的

(pinplanner))

如果不下载到开发板上进行测试,引脚可以不用分配)

双击location为您的输入输出配置引脚。

第七步:

整体编译(工具栏的按钮

(startComplilation))

第八步:

testbench仿真

(1)

仿真环境配置:

(2)

点击菜单栏中processing,选择start,选择starttestbenchtemplatewrite。

此时会自动生成testbench模板到项目文件夹simulation\modelsim里面,后缀为.vt

在quatusii界面打开…simulation\modelsim文件夹下的.vt文件

进行修改编辑,程序如下,修改完毕,保存:

(3)在项目管理窗器件上右击选择settings

打开如下界面:

点击

按照.vt内容(Testbenchname要和)填写上面内容,选择modelsim文件夹下.vt文件

依次点击确认,完成设置

(4)选择tools/options,在EDAToolOptions下确定ModelSim-Altera的中ModelSim.exe所在文件夹,通常在…modelsim_ase\win32aloem下

(5)

点击Tools>

RUNEDAsimulationTools>

RTLsimulation即可。

若无错误,系统可自动调用Modesim,

并弹出,

选择否来看仿真结果,波形窗口将出现以下仿真波形。