基于FPGA的PCIe设计.docx

《基于FPGA的PCIe设计.docx》由会员分享,可在线阅读,更多相关《基于FPGA的PCIe设计.docx(14页珍藏版)》请在冰豆网上搜索。

基于FPGA的PCIe设计

基于FPGA的PCIe设计

1.PCIe简介

1.1.PCIe基本架构

PCIe的优势以其复杂性为代价。

PCIe是基于分组的串行连接协议,估计比PCI并行总线复杂10倍以上。

这种复杂性部分源于在千兆赫速率所要求的并行到串行的数据转换以及转向基于分组的实现。

PCIe保持了PCI基于加载存储的基本架构,包括对PCI-X增加的对分割事务的支持。

此外,它引进了一系列底层信息传送要件来管理(如链路层流量控制)以模仿传统并行总线的边带线,且提供了更高水平的robustness和功能。

该规定义了许多特性、能同时支持当今的需求和未来的扩展需要,且同时与PCI保持了软件兼容。

PCIExpress的先进特性包括:

主动电源管理;先进的错误报告;通过端对端循环冗余校验(ECRC)支持的端对端的可靠性;支持热插拔以及服务质量(QoS)流通类。

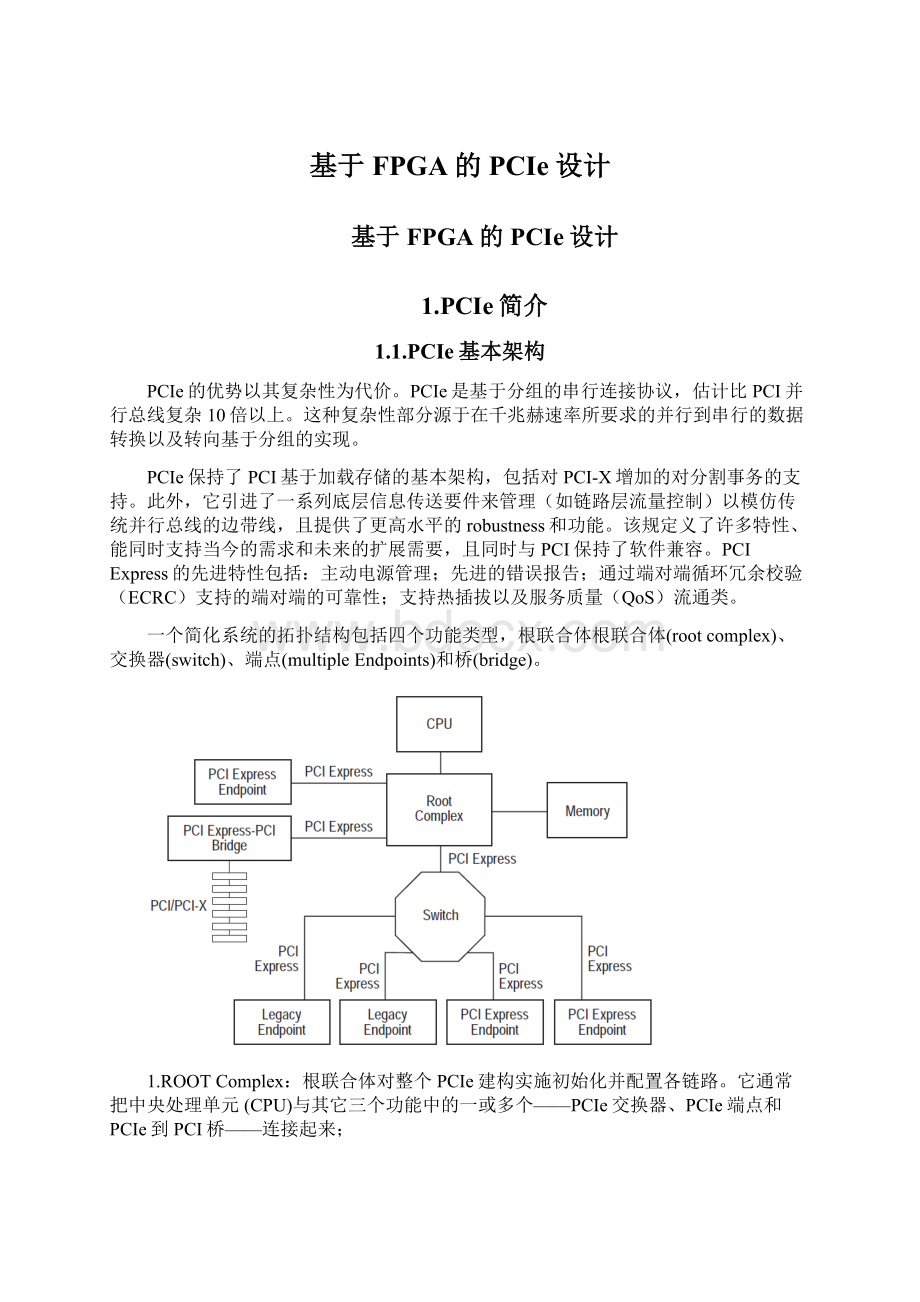

一个简化系统的拓扑结构包括四个功能类型,根联合体根联合体(rootcomplex)、交换器(switch)、端点(multipleEndpoints)和桥(bridge)。

1.ROOTComplex:

根联合体对整个PCIe建构实施初始化并配置各链路。

它通常把中央处理单元(CPU)与其它三个功能中的一或多个——PCIe交换器、PCIe端点和PCIe到PCI桥——连接起来;

2.Endpoint:

端点通常位于终端应用,它负责连接应用与系统的PCIe网络。

端点要求并完成PCIe事务传输。

一般来说,系统的端点比任何其他类型的PCIe部件都要多;

(1)LegacyEndpoint;

(2)PCIExpressEndpoint;

(3)RootComplexIntegratedEndpoint;

3.Switch:

PCIe交换器把数据路由至下游多个PCIe端口,并分别从其中每个端口路由到上游唯一一个根联合体。

PCIe交换器也可以灵活地把数据从一个下游端口路由到另一个下游端口(点对点),它消除了传统PCI系统限制性的树状结构;

4.RootComplexEventCollector;

5.PCIExpress-PCIBridge:

桥用于连接PCIe与系统诸如PCI/PCI-X等其他PCI总线标准,这样的系统同时采用上述各总线架构;

1.2.PCIe协议规格

PCIe规对于设备的设计采用分层的结构,有事务层、数据链路层和物理层组成,各层有都分为发送和接收两功能块。

在设备的发送部分,首先根据来自设备核和应用程序的信息,在事务层形成事务层包(TLP),储存在发送缓冲器里,等待推向下层;在数据链路层,在TLP包上再串接一些附加信息,这些信息是对方接收TLP包时进行错误检查要用到的;在物理层,对TLP包进行编码,占用链路中的可用通道,从发送器发送出去。

事务层包(TLP),数据链路层包(DLLP),物理层(PLP)产生于各自所在层,最后通过电或光等介质和另一方通讯。

这其中数据链路层包(DLLP),物理层(PLP)的包不需要关心,在PCIe

HIP核中封装好了。

在FPGA上做PCIe的功能就是完成事务层包(TLP)的处理。

1.3.处理层(TransactionLayer)

处理层接收来自PCIe设备应用的数据,并将其封装为TLP(TransactionLayerPacket)后,发向数据链路层。

此外事务层还可以从数据链路层中接收数据报文,然后转发至PCIe设备的核心层。

处理层在应用层和数据链路层之间,来产生和接收传输层的包。

处理层包括:

发送数据路径,配置空间和接收路径。

接收数据流程:

1)收到从数据链路层来的TLP;

2)配置空间用来确定处理层的包是否正确;

3)在每个虚拟通道,处理层的包被存在接收buffer中一个特定的部分(由收发类型确定:

posted,non-posted,completion);

4)处理层packetFIFO块用来存储buffer传输层包的地址;

发送数据流程:

1)MegaCore通过tx_cred[35:

0]来给应用层提供信息;

2)应用层会请求传输层给它包,此时应用层需要提供提供PCIExpress传输字头在tx_desc[127:

0]中,已经数据在tx_data[63:

0]中;

3)Megacore会确认suffiicientflowcontrolcredits,并确定是相应还是延迟请求;

4)处理层仲裁各虚拟通道,然后选择优先级高的数据给数据链路层;

1.3.1.处理层结构

1.3.2.TLP报文

TLP有三部分组成,帧头、数据、摘要(或者称ECRC)。

TLP头标长3或者4个DWORD,格式和容随报文类型变化,如下图所示。

●Fmt[1:

0]–FormatofTLP–bits6:

5ofbyte0;

●Type[4:

0]–TypeofTLP–bits4:

0ofbyte0;

●TC[2:

0]–TrafficClass–bits[6:

4]ofbyte1;

●Attr[1:

0]–Attributes–bits[5:

4]ofbyte2;

●TD–1bindicatespresenceofTLPdigestintheformofasingleDWattheendoftheTLP–bit7ofbyte2;

●EP–indicatestheTLPispoisoned–bit6ofbyte2;

●Length[9:

0]–LengthofdatapayloadinDW–bits1:

0ofbyte2concatenatedwithbits7:

0ofbyte3;

数据端为TLP帧头定义下的数据段,如果该TLP不携带数据,那该段为空。

Digest段(可选)是基于头标、数据字段计算出来的CRC,成为ECRC,一般Digest段由IP核填充。

1.3.3.Non-posted&Posted

如果设备发起端发出一个Non-Posted请求,在一定时间后,接收端需要回复一个完成包给发起端。

如果发出的是Posted请求,不需要回复完成包给发起端。

⏹PostedRequests:

RequeststhatdonotrequireaCompletion;

⏹Non-postedRequests:

AvalidRequesterIDisrequiredtoproperlyroutetheresultingcompletions;

除了MemoryWrite和Message事务属于Posted报文,其他事务报文都是Non-posted报文,例如MemoryRead、IO和Configuration等报文。

1.4.数据链路层(DataLinkLayer)

1.4.1.数据链路层结构

■Linkmanagementthroughthereceptionandtransmissionofdatalinklayerpackets,whichareusedforthefollowingfunctions:

■Toinitializeandupdateflowcontrolcreditsforeachvirtualchannel;

■Forpowermanagementofdatalinklayerpacketreceptionandtransmission;

■TotransmitandreceiveACK/NACKpackets;

■DataintegritythroughgenerationandcheckingofCRCsfortransactionlayerpacketsanddatalinklayerpackets;

■TransactionlayerpacketretransmissionincaseofNAKdatalinklayerpacketreceptionusingtheretrybuffer,Managementoftheretrybuffer;

■LinkretrainingrequestsincaseoferrorthroughtheLTSSMofthephysicallayer;

1.4.2.DLLP报文

数据链路层保证来自发送端事务层的报文可以可靠、完整地发送到接收端的数据链路层。

来自事务层的报文在通过数据链路层时,将被添加SequenceNumber前缀和CRC后缀。

数据链路层使用ACK/NAK协议保证报文的可靠传递。

PCIe总线的数据链路层还定义了多种DLLP(DataLinkLayerPacket),DLLP产生于数据链路层,终止于数据链路层。

值得注意的是,TLP与DLLP并不相同,DLLP并不是由TLP加上SequenceNumber前缀和CRC后缀组成的。

1.5.物理层(PhysicalLayer)

物理层是PCIe总线的最底层,将PCIe设备连接在一起。

PCIe总线的物理电气特性决定了PCIe链路只能使用端到端的连接方式。

PCIe总线的物理层为PCIe设备间的数据通信提供传送介质,为数据传送提供可靠的物理环境。

物理层可以分割成2个子层:

电气层和逻辑层。

而有一些公司已经在电气层和逻辑层之间定义和采用了一种接口,这种接口称为PCIExpress物理接口(PIPE)。

控制器物理层用于与PHY的接口,并用于管理许多能够发起链路构建数据包的功能。

一些特殊序列用于建立物理链路、进入和退出低功耗链路状态等。

这些序列用于同步PCIe链路,并进行链路管理。

值得注意的是PCIe设备发送PLP与发送TLP的过程有所不同。

物理层的接收部分负责:

⏹通道映射、通道间去偏移,适用于由多条线路构成的链路。

⏹数据解扰

⏹数据包检测和解帧

⏹检查特殊数据包序列,例如TS1、TS2、跳过和电气空闲。

物理层的发送部分负责:

⏹采用特殊符号插入来对数据包进行封帧,例如采用STD或SDP符号来标志数据包的开始,用END符号来标志结尾。

⏹数据加扰。

⏹链路控制——初始化、带宽和线路反转(lane-reversal)协商。

⏹多条线路发送控制。

⏹生成跳过序列来补偿链路两端的时钟PPM差异。

1.5.1.物理层结构

■Initializingthelink;

■Scramblinganddescramblingand8B/10Bencodinganddecodingof2.5Gbps(Gen1)or5.0Gbps(Gen2)perlane8B/10B;

■Serializinganddeserializingdata;

ThehardIPimplementationincludesthefollowingadditionalfunctionality:

■PIPE2.0InterfaceGen1/Gen2:

8-bit250/500MHz(fixedwidth,variableclock);

■Autospeednegotiation(Gen2);

■Trainingsequencetransmissionanddecode;

■Hardwareautonomousspeedcontrol;

■Autolanereversal;

1.5.2.LTSSM

物理层是PC