西北农林科技大学单片机知识点Word文档格式.doc

《西北农林科技大学单片机知识点Word文档格式.doc》由会员分享,可在线阅读,更多相关《西北农林科技大学单片机知识点Word文档格式.doc(7页珍藏版)》请在冰豆网上搜索。

寄存器间接寻址

片内RAM低128B[@Ri,SP(仅PUSH和POP)]

片外RAM(@Ri,@DPTR)

变址寻址(基址+变址寻址)

ROM(@A+PC,@A+DPTR)

相对寻址

ROM256B范围

位寻址

片内RAM20H~2FH单元的位(128位)

部分SFR中的可寻址位

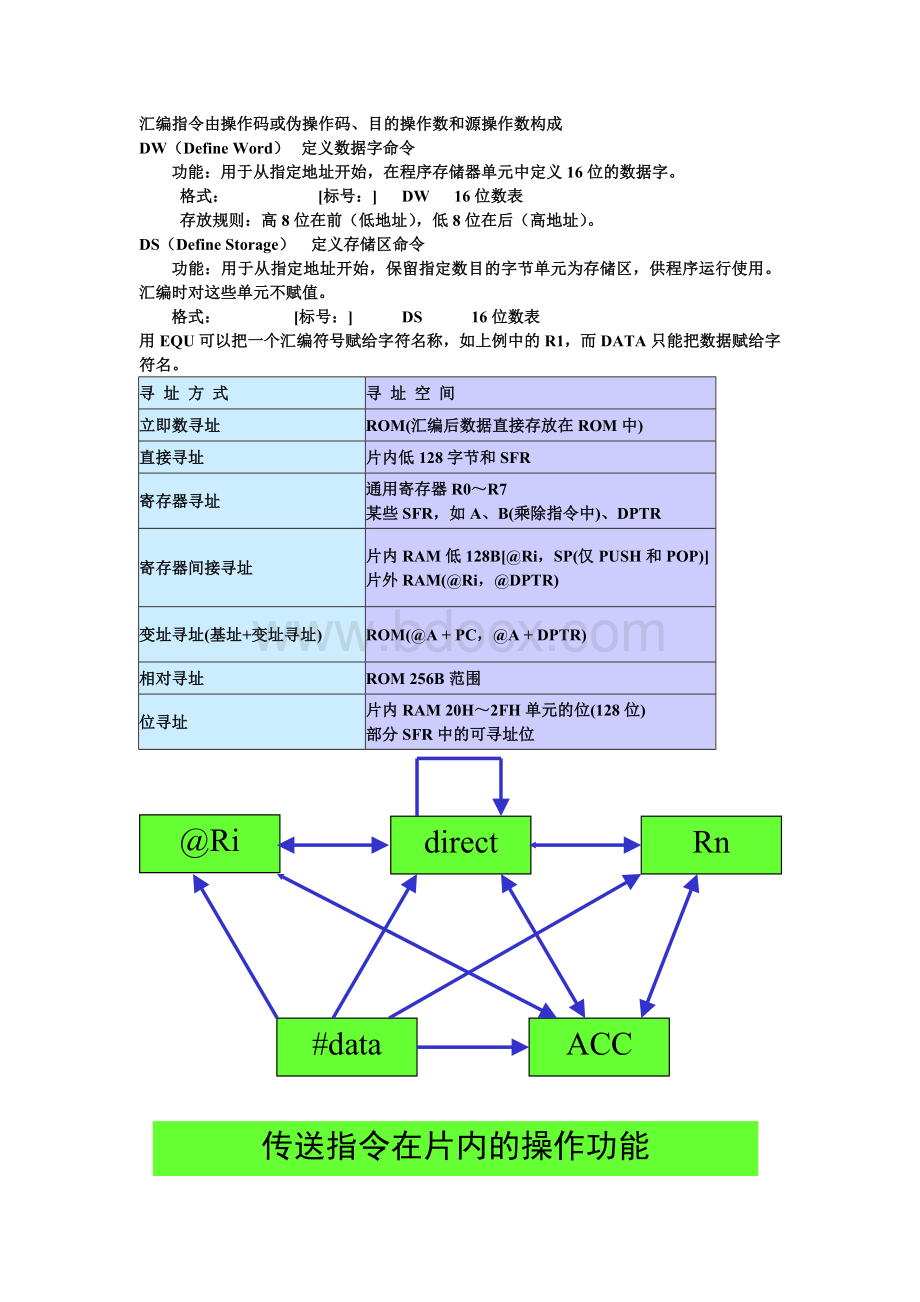

@Ri

direct

Rn

ACC

#data

传送指令在片内的操作功能

A寄存器

@R1、@R0

(外部RAM低256B)

@DPTR

(外部RAM64KB)

整字节交换指令

XCH A,Rn ;

(A)←→(Rn)

XCH A,direct ;

(A)←→(direct)

XCH A,@Ri ;

(A)←→((Ri))

(2)半字节交换指令:

XCHD A,@Ri;

(A)3~0←→((Ri))3~0

(3)累加器高低半字节交换指令:

SWAP A ;

(A)3~0←→(A)7~4

5)堆栈操作指令组:

进栈、出栈两种操作。

PUSH direct;

SP←(SP)+1,(SP)←(direct)

POP direct;

direct←((SP)),SP←(SP)-1

传送类指令一般不影响标志位。

个别影响P位。

但堆栈指令(PUSH和POP)可以直接修改状态字PSW。

乘除指令组

乘积<

0FFH(即(B)=0),则OV=0,否则OV=1。

该运算总使CY=0。

除法当除数为0(B=0)时,OV=1,表明除法无意义,无法进行;

其它情况下,OV=0。

任何情况下,CY=0。

指令

十进制调整的内容(BCD调整)

(1)如果任何两个对应位BCD数相加的结果向高一位无进位时,若得到的结果小于或等于9,则该位不需修正;

若得到的结果大于9且小于16位,则该位进行加6修正。

(2)如果任何两个对应位BCD数相加的结果向高一位有进位时(即结果大于或等于16),该位进行加6修正。

(3)低位修正结果使高位大于9时,高位进行加6修正。

ANL常用于屏蔽字节中的某些位。

欲清除的位和“0”与,欲保留的位和“1”与

ORL用途:

用于使字节中的某些位置“1”。

欲不变的位,用“0”去“或”,

欲置1的位,用“1”去“或”。

异或有一初一全一出零

累加器清0指令:

CLR A ;

A←0

累加器按位取反指令:

CPLA ;

A←(A)

LJMPaddr16

;

跳转范围64KB,PC←addr16,三字节指令

AJMP绝对转移指令

AJMPaddr11

;

跳转范围2KB,PC←(PC)+2

PC10~0←addr11

SJMPrel ;

目的地址=(PC)+2+rel

简洁转移JMP@A+DPTR ;

PC←(A)+(DPTR)

JZ rel

;

若(A)=0,则PC←(PC)+2+rel

若(A)≠0,则PC←(PC)+2

JNZ rel

若(A)≠0,则PC←(PC)+2+rel

若(A)=0,则PC←(PC)+2

CJNEA,#data,rel

若(A)-data=0:

顺序执行PC←(PC)+3

CY=0

若(A)-data>

0:

跳转 PC←(PC)+3+rel

CY=0

若(A)-data<

0:

跳转 PC←(PC)+3+rel

CY=l

DJNZdirect,rel;

三字节指令

LCALL addr16

;

PC←(PC)+3

;

SP←(SP)+1,(SP)←(PC)7~0

SP←(SP)+1,(SP)←(PC)15~8

;

PC←addr16

已知DELAY=1200H,试问MCS-51单片机执行下列指令后,堆栈中数据如何变化?

PC中内容是什么?

MOV SP,#30H

DELAY:

LCALL2356H

(SP)=32H,(31H)=03H,(32H)=12H,PC=2356H。

ACALLaddr11

PC←(PC)+2

;

;

PC10-0←addr11

返回指令

RET;

子程序返回指令

;

PC15~8←(SP),(SP)←(SP)-1

PC7~0←(SP),(SP)←(SP)-1

位地址的表示方法主要有下列四种:

以AC为例

•直接位地址表示:

0D6H(PSW的位6)

•点操作符表示:

PSW.6

0D0H.6

•位名称表示:

AC

将内部RAM中20H单元的第6位(位地址为06H)的内容,传送到P1.0中。

MOV C,06H

MOV P1.0,C

位置位清零指令(共4条)

CLR bit ;

bit←0

CLRCY ;

CY←0

SETBbit ;

bit←1

SETBCY ;

CY←1

ANL C,bit ;

CY←(CY)∧bit

ANL C,/bit ;

CY←(CY)∧

ORL C,bit ;

CY←(CY)∨bit

ORL C,/bit ;

CY←(CY)∨

CPL bit ;

bit←()

CPL C ;

CY←()

以CY内容为条件的转移指令(2条)

JCrel

;

若(CY)=1,则(PC)←(PC)+2+rel,

否则(PC)←(PC)+2

JNCrel

;

若(CY)=0,则(PC)←(PC)+2+rel,

否则(PC)←(PC)+2

该指令一般与比较条件转移指令CJNE一起使用。

以位地址内容为条件的转移指令(3字节指令)

JBbit,rel

;

若(bit)=1,则(PC)←(PC)+3+rel

否则,(PC)←(PC)+3

JNBbit,rel

JBCbit,rel

;

若(bit)=1,则(PC)←(PC)+3+rel,

(bit)←0;

否则,(PC)←(PC)+3

单片机组成部件及功能

CPU程序存储器数据存储器定时/计数器并行I/O口(数据的并行输入和输出)串行口(串行数据传送)中断控制系统时钟电路

EA引脚作用功能选择访问的外部程序存储器对内部EPROM编程时给此引脚施加21v电源

接地时只访问外部程序存储器高电平时先访问外部程序存储器

MCS-51单片机的引脚中有多少根I/O线?

它们分别与单片机对外的地址总线和数据总线之间有什么关系?

其地址总线和数据总线各有多少位?

可以寻址多大的地址空间?

答:

共有4个8位的并行口,P0、P1、P2和P3。

51单片机的三总线:

数据总线:

8位,由P0口提供。

地址总线:

16位,由P0和P2口提供。

可寻址64KB的地址空间。

8051单片机的控制总线信号有哪些?

各有何作用?

(1)EA*/VPP(31脚):

EA*为访问外部程序存储器控制信号,低电平有效。

(2)RST/VPD(9脚):

RST即为RESET,复位信号,高电平有效。

(3)ALE/PROG*(30脚):

地址锁存允许信号。

访问外部存储器时,ALE把P0口输出的低8位地址信息锁存起来,实现低8位地址和数据的分时传送。

(4)PSEN*(29脚):

片外程序存储器读选通信号输出端,低电平有效。

即外部ROM的读信号。

(相当于外部RAM的RD*)

I/O口特点

(1)P0口(39脚~32脚):

P0.0~P0.7统称为P0口,分时提供低8位地址总线和8位双向数据总线。

(2)P1口(1脚~8脚):

P1.0~P1.7统称为P1口,可作为准双向I/O接口使用。

(3)P2口(21脚~28脚):

P2.0~P2.7统称为P2口,作为准双向I/O接口,或提供高8位地址总线。

(4)P3口(10脚~17脚):

P3.0~P3.7统称为P3口,作为准双向I/O接口使用,每个引脚具有第二功能。

8051单片机的PSW寄存器各标志位是什么意义?

分析执行78+119后PSW中各标志位的值。

CY(PSW.7)——进位标志位;

位累加器

AC(PSW.6)——辅助进位标志位

F0(PSW.5)——用户标志位

RS0和RS1(PSW.4,PSW.5)——寄存器组选择位

OV(PSW.2)——溢出标志位

P(PSW.0)一一奇偶标志位。

表明累加器A中数的奇偶性

8051单片机复位后的初始状态是怎样的?

复位方法有几种?

(1)(PC)=0000H

(2)特殊功能寄存器

除(SP)=07H,(P0~P3)=0FFH,其他特殊功能寄