Cadence Design entry HDL 教程Word文件下载.docx

《Cadence Design entry HDL 教程Word文件下载.docx》由会员分享,可在线阅读,更多相关《Cadence Design entry HDL 教程Word文件下载.docx(39页珍藏版)》请在冰豆网上搜索。

原理图的绘制:

在本章中将具体介绍多页原理图的绘制,内容涉及如何添加part,绘制连接线,绘制bus,检查整个设计等等。

第三章:

原理图绘制的高级应用:

在本章中将具体介绍层次式原理图的绘制,原理图网络表的产生,使用globalfind的功能来寻找整个设计中的某个元件以及对元件的属性进行编辑等等。

创建项目

内容概要:

●第一节概念

1、什么是库

2、什么是cds.libfile

3、什么是projectfile

●第二节创建一个项目(project)

●第三节用projectsetup来增加库

第一节概念

在cadence中,一个project包含如下的对象:

1、涉及到的库;

2、本地库(designlibraries)

3、Cds.lib文件

4、Projectfile(.cpm)

接下来,将详细介绍

什么是库?

从设计原理图、PCBLayout直到进行真正的制造,不同的阶段,需要用到的元件的表现形式是不一样的。

原理图中,我们需要元件的符号,如果需要仿真,我们就需要元件的电器模型参数,在PCBLayout阶段,我们则需要元件的PCBFootprint。

在设计的不同阶段,我们把每个阶段软件所需要的同一类型元件(符号、模型或PCBFootprint)组织在一起,就构成了库。

◎Schematiclibraries

原理图中库就是一些逻辑符号,插脚引线以及一些封装信息;

◎Layoutlibraries

LayoutLibraries就是和原理图对应的元件的FootPrint。

◎SimulationLibraries

这些库就是用Verilog或VHDL硬件描述语言来模拟实际元件行为的信息。

Cadence提供很多参考库,另外,还有一个经常要用到的Standard库,Standard库是参考库的一个。

(后续章节将会详细介绍)Standard库位于<

your_inst_dir>

/share/library目录之下。

在Cadence提供的参考库中,包含如下几个文件夹:

sym_1,entity,chips,part_table

下表给出了各个文件的简介:

文件名

描述

sym_1

描述了原理图的符号

entity

描述了原理图符号各个pin

chips

原理图与物理封装的匹配信息

part_table

描述了用户为元件自定义的信息,如为元件定义适合各个企业自身需要的属性。

下图是一个库文件结构的例子。

LocalLibraries就是工程师创建一个项目后,依附项目本身的库。

设计师可以导入Cadence提供的参考库,加以编辑作为localLibraries来使用。

下图是LocalLibraries的结构。

什么是CDS.Lib

Cds.lib定义了设计一个项目所涉及到的库,以及这些库所在的物理地址。

如:

DEFINE54alsttl../../library/54alsttl

DEFINE54fact../../library/54fact

DEFINEtutorial_libworklib

INCLUDE$CONCEPT_INST_DIR/share/cdssetup/cds.lib

DEFINElocal_liblocal_lib

什么是ProjectFile?

当你创建好一个项目的时候,AllegroProjectManager就会自动产生一个ProjectFile。

ProjectFile其文件名称是<

projectname>

.cpm。

察看ProjectFile包含的信息,可以用记事本打开。

在这里不作详细陈述。

创建一个Project

1、选择:

开始〉程序〉AllegroSPB15.5〉ProjectManager

其中,OpenProject是用来打开一个现存的项目,而CreateDesignProject就是新建一个项目。

我们点击CreateDesignProject,出现一个对话框,我们照下图所示输入相应内容:

ProjectName就是所要创建的项目的名称,在该例中,软件将会产生一个tutorial.cpm的projectFile.Location就是定义该项目所处的路径。

2、点击Next,出现新的对话框:

注意:

如果在上述的对话框的左侧,AvailableLibraries中出现的库,和你的出现的不一致,是因为Cds.lib还没有将Cadence所提供的参考库加入到您的设计中。

请参考如下方法添加:

请先安装Cadence提供的参考库。

(第三张光盘)

·

打开<

\share\cdssetup,找到该文件夹中的Cds文件,用记事本打开;

在该文本中添加:

include<

\share\library\cds.lib

也可以将所有需要用的库文件统一放在一个文件夹下,然后在Cds.lib文件中自定义一个库名称,如:

DefineMyD:

\cadence\lib\

关于Define和Include的区别:

1、Define:

可以加载单独的某个库,或者包含多个库的某个文件夹的,但是一定需要给出一个自定义的名称,如DefinemyD:

\cadence\lib\,或者DefineactelD:

\cadence\lib\actel

2、Include:

已经存在一个类似Cds.lib的其他*.lib的文件,我们只需用Include把它包含进来即可。

保存,关闭。

4、点击Next,出现DesignName对话框:

在Libraries下拉选择框中,我们选择tutorial_lib,DesignName中,我们输入desexample。

这样,Desexample便存放在Tutorial_lib中。

5、点击Next,出现Summary对话框,这个对话框显示了前面几步定义好的信息,如果需要修改,请点击Previous返回到前面几步做修改。

6、点击Finish。

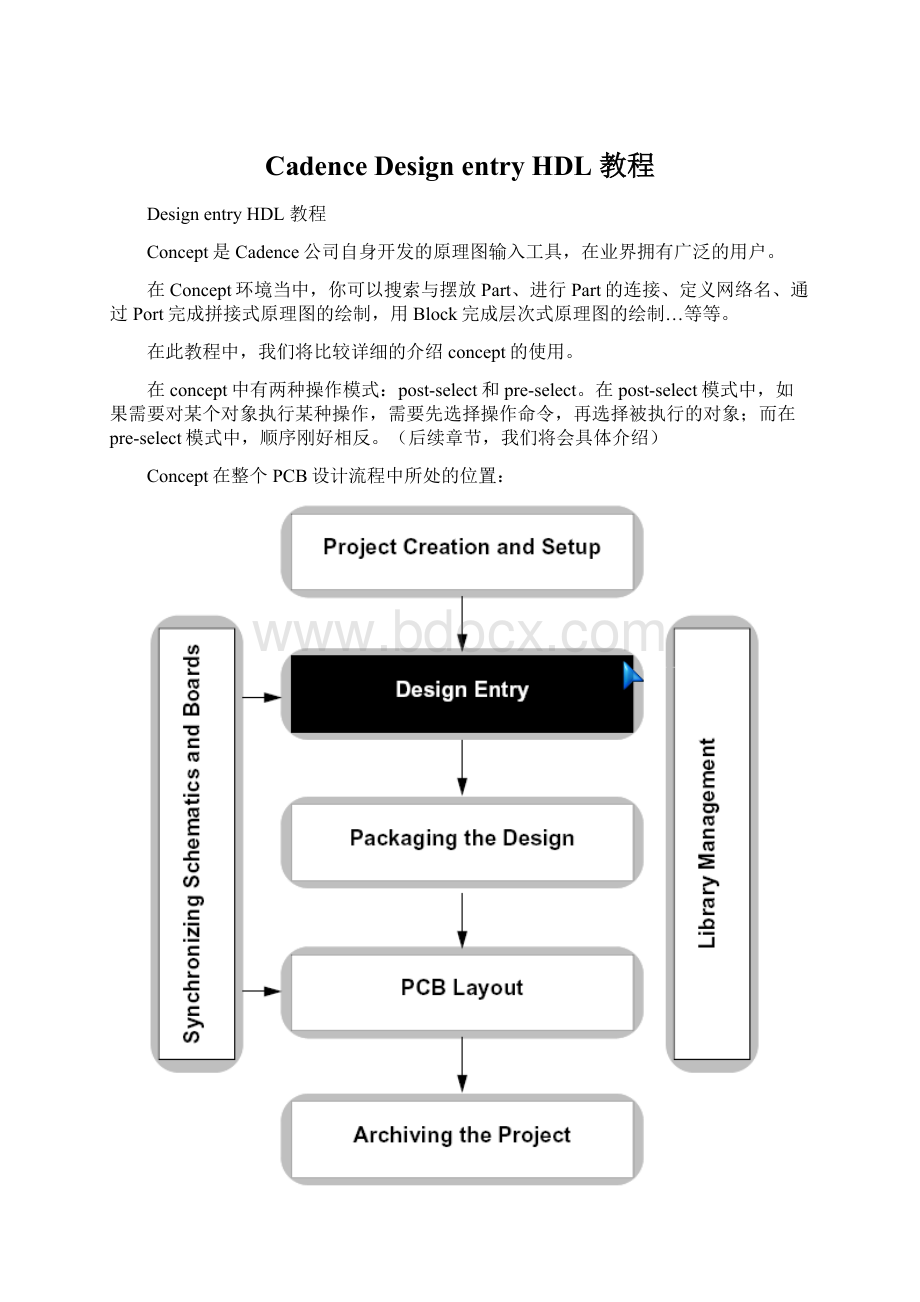

这样,ProjectManager便创建好一个项目,并显示出PCB板设计流程的界面。

使用ProjectManagerSetup来增加库

通过向导创建好一个项目之后,我们也可以使用Setup对项目作一些改变,如增加Libraries或Cell等。

在本节,我们将介绍将项目添加Local_lib到项目中。

3、首先,请打开<

/doc/concepthdl_tut/tutorial_examples文件夹,将该文件夹中的local_lib.zip的文件释放到D:

\Designs\local_lib。

4、点击ProjectManager界面中的Setup,在出现的ProjectSetup对话框选择Global面板,

5、点击Edit,ProjectManager用写字板打开Cds.lib。

6、在写在板中增加如下内容:

DEFINElocal_liblocal_lib

这样,cds.lib就增加了local_lib库。

7、保存并关闭写字板,ProjectManager会出现下面的对话框:

选择Yes。

8、在Availablelibraries列表中选择Local_lib.

9、点击Add。

10、选中Local_lib,点击Up按钮,直到Local_lib处于tutorial_lib之下;

11、选中lsttl库,点击add;

12、点击Allply;

13、切换到PartTable面板,如下图点击Add,增加PhysicalPartTableFiles;

14、在出现的AddPhysicalPartTable对话框中选择File;

15、打开Local_lib文件夹;

16、选中local_lib.ptf然后点击Open;

AddPhysicalPartTable对话框出现Local_lib.ptf的路径:

17、点击Ok。

16、PhysicalPartTableFiles一栏显示出了新增的Local_lib.ptf的路径:

17、点击OK。

第三章原理图的绘制

本章内容概要:

DesignEntryHDL起步;

增加页边框;

增加文字(注释);

选择并添加元件;

元件的连接;

给网络线命名;

增加Port;

增加Power和Ground;

保存原理图;

察看Verilog描述;

绘制总线;

总线接入线绘制;

增加元件的电气属性;

保存并察看错误信息。

DesignEntryHDL起步

画原理图的第一步是用启动DesignEntryHDL。

通过DesignEntryHDL中,才能从提供的库中调用相应得元件,然后进行连接,完成逻辑设计。

在ProjectManager界面中,点击DesignEntry图标即可启动DesignEntryHDL。

启动之后,我们可以在DesignEntryHDL的TitleBar看到DesignName。

在本例中是DESEXAMPLE.SCH.1.1。

下面我们具体解释该名称:

在TitlebarDesignName的后面,我们还可以看到用方括号括住的inhierarchy字样。

Inhierarchy是DesignEntryHDL三种使用模式的一种。

inhierarchy模式

当用户打开一个设计的时候,最先打开的是处于顶层的原理图页,并且,顶层的设计名称也会显示在TitleBar,紧跟在名称之后的是方括号内的inhierarchy字样。

这表示DesignEntryHDL已经识别出设计的层级。

你可以使用ascend和descend命令来察看层级式的原理图。

具体命令是:

File>

Edit>

Hierarchy>

Ascend或File>

EditHierarchy>

Descend。

你也可以使用File>

Return来返回之前察看得原理图页。

使用Pre-Select模式

Pre-select和post-select两种模式都可以使用,De